|

"MTX Plus+" CPU Board -

CPLD Comparison

As the amount of logic in the MTXPlus+ CPU CPLD expanded to

support additional features of the system, the CPLD's resources

became an issue. In the first instance, the quantity of

available logic resources, i.e., the number of macrocells (128)

in the Altera EPM7128S appeared to be the limiting factor.

There was a relatively easy solution to this, Lez had also

obtained a couple of the next size up Altera CPLDs for me - the

EPM7160S (160 macrocells). The 7160 is pin-compatible with the

7128, with the exception that 4 fewer I/O pins are available.

With some slight modification to the CPU board design, such as

removing the external Page Port signals from the CPLD and using

a 74HCT273 instead, some relocation of CPLD I/O would have

allowed the additional logic to fit into the larger CPLD.

However, the design continued to develop and the reduced

number of I/O pins in the 7160 then became a limiting factor. It

would not have been possible to fit in all of the desired

functions into either the 7128 (macrocell constrained) or 7160

devices (I/O constrained).

Tony did some research and identified a possible solution by

replacing the Altera EPM7128S with an Atmel ATF1508AS.

The Atmel website

provides a high level summary of the

ATF15xx series features :

Atmel CPLDs: Industry Compatible

The ATF15xxAS/ASL/ASV/ASVL CPLD family offers

pin-compatible supersets of the popular Altera 7000 and

3000 series devices ranging from 32 to 128 macrocells

with propagation delays from 7.5 to 15 ns for 5V

standard power versions and 15 ns for 3.3V versions. All

devices also support JTAG in-system programming (ISP).

The Logic Doubling™ features of the ATF15xx

family make these products ideal for new designs. The

ATF15xx family offers the most powerful switch matrix

and routing resources of any CPLD while also supporting

multiple independent feedbacks, individual output

enable, global clear and D/T/latch configurable

flip-flops. More global clock pins, a programmable

pin-keeper and the ability to realize two latches per

macrocell are further examples of the enhanced features

available from this CPLD product family. |

Of course, as would be expected, Altera assert that the Atmel

device is not equivalent to their device and produced an

Analysis Report (M-WP-ATF1500-1,

September 1998) justifying their conclusions :

| "The test results show that ATF1508AS devices are

not equivalent to EPM7128S devices. The Atmel

devices have slower timing characteristics (which caused

problems for both synchronous and asynchronous circuits)

and different data sheet parameters than Altera devices.

Additionally, they consume up to four times more current

than Altera devices, which causes the Atmel devices to

exceed thermal reliability limits at certain

frequencies. This increase in power consumption could be

attributed to the fact that the ATF1508AS die size is

twice as large as the EPM7128S die. Lastly, the Atmel

devices do not support ISP in manufacturing environments

with in-circuit testers." |

For use in MTXPlus+, the importance difference between the

two devices is the Logic Doubling™ feature of the Atmel device,

described in detail in an Atmel White Paper (2310A–03/01).

The paper describes how I/O pin to logic cell connectivity

differs between CPLDs and smaller PLDs such as PALs and GALs. In

the smaller devices, all I/O pins are fully connected to all

logic cells. However, as the number of macrocells in a CPLD

increases, the required dye area required to maintain full

connectivity becomes prohibitive and macrocells are typically

grouped into blocks (LABs) which have full connectivity to a

subset of the I/O and limited connectivity with the rest.

When designing the ATF series, Atmel endeavored to retain as

much I/O connectivity and logic reusability as possible, and in

the ATF 1502, 100% connectivity is maintained. The Global bus in

the ATF1500 has all input and feedback signals available to all

logic blocks, In the larger devices in the series, i.e., the

1504 and 1508, 100% connectivity is not achieved and these

devices use the global/regional bus hierarchy for cross-point

allocation. "Even so, Atmel’s CPLDs maintain the highest

connectivity of any CPLD Family."

|

Altera vs. Atmel Macrocell Comparison |

|

|

| Altera EPM7128SLC84-10 |

Atmel ATF1508AS-10JU84 |

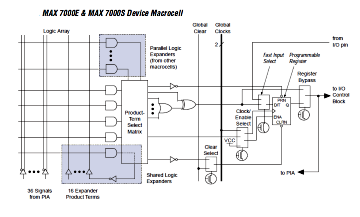

The macrocell schematics from the Altera and Atmel datasheets

help explain the differences between the two devices.

Each macrocell in the Altera device

consists of three functional blocks :

|

| the

logic array |

Combinatorial logic is implemented in the logic

array, which provides five product terms per macrocell.

|

|

the product term select matrix |

Allocates the product terms for

use as either primary logic inputs to the OR and XOR

gates to implement combinatorial functions, or |

| the programmable

register |

Allocates the product terms as secondary inputs to

the macrocell's register clear, preset, clock and clock

enable control functions |

In addition to the directly accessible I/O (7 or 8 pins),

each macrocell in the Altera device has 36 connections to the

Programmable Interconnect Array (PIA).

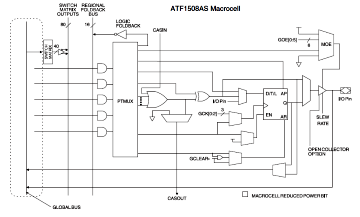

The Atmel device has the same number of directly connected I/O,

but has 40 connections to Atmel's equivalent of the PIA - the

Global Bus.

Each LAB in the Altera device has 16 Shared Logic

Expanders that can be viewed as a pool of

uncommitted single product terms (one from each macrocell) that

feed back into the logic array. These expanders are referred to

as Foldback Terms in the Atmel

datasheet and shown connected to the Regional

Foldback Bus, again, there is 1

Foldback / Shared Expander

term per macrocell.

The Altera macrocell schematic shows Parallel

Logic Expanders, these are unused product terms

that can be allocated to a neighboring macrocell to implement

complex logic functions. Parallel expanders allow up to 20

product terms to directly feed the macrocell OR logic, with 5

product terms coming from the macrocell and the other 15 being

provided by neighboring macrocells in the LAB. The Atmel

datasheet refers to Parallel Expanders

as Cascade Logic terms, with

CASIN and CASOUT

signals connecting to neighboring macrocells in the LAB. Using

CASIN, the Atmel device allows up to

40 product terms to feed the OR logic.

The Atmel macrocell has an enhancement over the Altera

device, there is an additional buried feedback signal that goes

to the Global bus. The extra buried signal can be either

combinatorial or registered, regardless of whether the macocell

output is combinatorial or registered. Feedback of a buried

combinatorial output allows the creation of a second latch

within a macrocell.

|

Feature Comparison |

| |

Altera EPM7128SLC84-10 |

Atmel ATF1508AS-10JU84 |

| Cost (Mouser UK, ex. VAT) |

£23.42 |

£8.93 |

| Propagation Delay (ns) |

6 |

10 |

| Maximum Frequency (MHz) |

147.1 |

125 |

| Useable Gates |

2500 |

3000 |

| Macrocells |

128 |

128 |

| Logic Array Blocks |

8 |

8 |

| Signal Pins |

68 |

68 |

| User I/O Pins (If JTag Used) |

64 |

64 |

| I/O Pins per macrocell |

6 to 16 |

8 to 12 |

| Logic Outputs per macrocell |

16 (to PIA) |

16 (to Global bus) |

| Internal CPLD Macrocell inputs |

36 (from PIS) |

(40 from Global bus) |

| Global Clock Inputs |

2 |

3 |

| Global Clear Inputs |

1 |

1 |

|

EDA Software |

Altera Quartus II 13.0SP1 |

Atmel ProChip Designer 5.0 |

| License Cost |

free |

$499 (2 year license) |

| Basic logic compiler |

n/a |

WinCUPL |

| License Cost |

n/a |

free |

Notional cost per device, based

on 1 device with EDA tools |

£23.42 |

£365.93 |

Notional cost per device, based

on 10 devices with EDA tools |

£23.42 |

£44.63 |

Notional cost per device, based

on 100 devices with EDA tools |

£23.42 |

£12.50 |

For incorporating a CPLD application in a commercial product,

it is clear that, from a cost perspective, the Atmel device

would work out significantly cheaper, even after paying for a

ProChip Designer license. For a small hobbyist project that

might generate a limited number of sales, the Altera device

works out cheaper - the break point after which the Atmel cost

starts to reduce below the Altera cost is ~25 devices.

If the designer just wants to use very basic logic functions

and is happy to program the device using boolean expressions,

then the Atmel device may be preferable for small scale products

too. On the other hand, if the designer wants to be able to use

a fully featured

Electronic Design Automation suite, with a full range of

simulation features and complex function blocks, then the Altera

device is likely the most appropriate choice.

For MTXPlus+, I had hoped to replace the Altera device with the Atmel

one to resolve the specific issues with the CPU board CPLD, but

continue to use the Altera devices for other CPLD

applications because of the availability of Quartus II. However,

as I could not justify the cost of the ProChip Designer License

until I knew for certain that I could "productise" MTXPlus+,

then I could not synthsise and simulate the CPLD logic, so I

will have to stick with the EPM7128S and thought that I would

need to find another solution

to the resource issue on the CPU board.

As it turns out though, Tony has significantly optimised the

Speculator+ design - as we as my bloated clock generation logic

and the complete MTXPlus+ design will now fit into the 7128.

Removing the Page Port from the CPLD means that the reduced

number of pins available in a 7160 is no longer an issue and by

"reserving" (i.e., not using) the pins that would be

unavailable in a 7160, the larger CPLD can be "dropped into" the

board should additional logic resources be needed.

<

Previous

Page Goto

Next

Page >

MTXPlus+ CPLD

Overview

|