|

"MTX Plus+" Memory Map

To understand

the Memory Map for MTXPlus+, it is necessary to describe

the memory configuration of the original MTX computer -

summarised in the table below, it is described in greater detail on my

MTX512 memory pages.

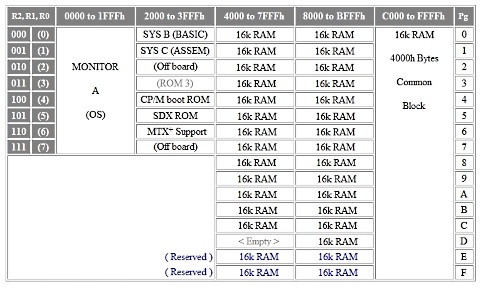

| MTX Computer Memory Map Overview |

|

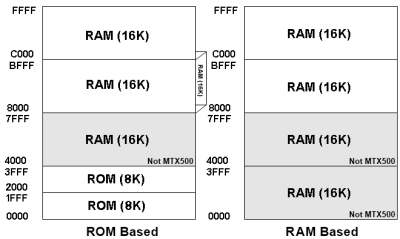

The MTX was designed to operate in two memory

modes :

- ROM based - the "normal" operating mode,

exposing the BASIC interpreter etc., and

- RAM based - used to make all of the memory

address space available to CP/M

|

|

ROMs

The MTX was fitted with 24kBytes of ROM on

the system board.

The first computers, using the 4000-04 version

system board, had a 16KB combined Operating System

(OS) and BASIC language ROM, along with an

8KB Assembly language (ASSEM) ROM.

Later models, using 4000-05 and 4000-06 version

system boards, had separate 8KB ROMs for each of the

OS, BASIC and ASSEM functions (although disassembly

of the ROMs shows that Memotech were forced to

distribute some of the functions due to lack of

space for all of the planned features and the code

does not conveniently fit into the three partitions

that the ROM names would suggest).

|

|

Board Version 4000-04

|

Board Versions 4000-05 &

4000-06

|

| ROM |

Location |

Size |

Function |

ROM |

Location |

Size |

Function |

| A |

9H |

16KB |

OS & |

A |

9H |

8K |

OS |

| |

|

|

BASIC |

B |

8H |

8K |

BASIC |

| B |

8H |

8KB |

ASSEM |

C |

10H |

8K |

ASSEM |

|

|

Of the 24KB of ROM available, 16KB could be

active at a given time, 8KB in the fixed ROM area

and 2 x 8KB blocks available for switching into the

8K paged ROM area (2000h to 3FFFh) as required.

Additional ROMs were installed on option boards and

were also mapped into the paged ROM area as

required.

The original Memotech paged ROMs were

:

| ROM ID |

Name |

Function |

Hardware Location |

| 0 |

(BASIC) |

BASIC |

MTX Computer Board |

| 1 |

(ASSEM) |

Assembler |

MTX Computer Board |

| 2 |

(Spare) |

(Applications) |

(NewWord & Pascal ROM Boards) |

| 3 |

(Spare) |

|

|

| 4 |

CP/M |

FDX Boot |

SM1 Bus Interface Card |

| 5 |

SDX |

SDX Boot |

SDX Disk Controller |

| 6 |

(Spare) |

|

|

| 7 |

GROM |

Games/Node |

External ROMPAKs |

|

|

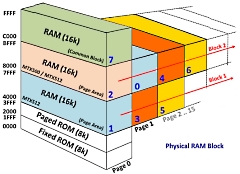

ROM & RAM Mode (RELCPMH = 0)

The Z80, having a 16-bit address

bus, natively supports 64KB of total memory (216),

access to memory outside this range requires the use

of paging.

| Function |

ROM Space |

Paged RAM |

Common Block |

| Size (KB) |

16 |

32 |

16 |

| Address Range |

0000h to 3FFFh |

4000h to BFFFh |

C000h to FFFFh |

The upper 16k of the 64k

address space, from C000h to FFFFh, is a block

common to all RAM pages. In ROM mode, the 8k Monitor

ROM (Operating System) is mapped into 0 to 1FFFh and

the 8k paged ROMs are mapped from 2000h to 3FFFh.

The window between 4000h and BFFFh is mapped as

16 x 32k pages, with each consisting of two 16k

blocks.

|

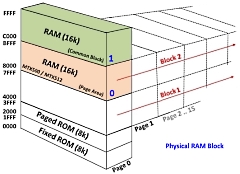

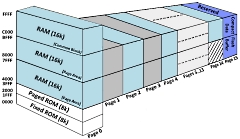

The

common block is always the last block of

RAM, i.e., A15 and A14 are high,

corresponding to the 48-64k block of RAM

for all the available pages. For an

MTX500, its 32k of RAM is

mapped as two 16k blocks in Page 0, from 8000h to FFFFh,

made up of the common block and an

additional half page (16k) of RAM. The

blocks are numbered from 0 to 1 as

shown, with only 48k total memory,

paging is not required. |

|

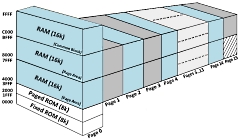

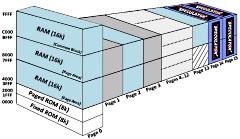

| For an MTX512, the additional 32k

page is added as two half page blocks,

the first filling the gap at Page 0,

Block 1 and the second occupying Page 1,

Block 2. The "final", common, block is

now Block 3 - Blocks 0 and 2 are swapped

from their expected positions and laid

out as per the RAM mapping done in the

original MTX512.

In this case, the paging maps Block 0

as required. |

|

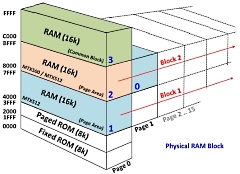

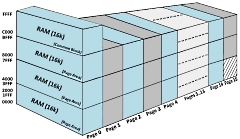

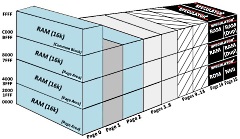

| As more memory is added, each extra

32k physical block is split

across a page boundary. In this example,

an extra 2 pages (4 blocks) have been

added, as in the RS128. Memory

continues to be filled in the same way

until Page 15 which eventually ends up

with a half unoccupied slot of 16k. (MTX

BASIC uses the position of the first

empty block to identify the end of RAM.) |

|

| Regardless of how the RAM is

physically mapped, as far as the CPU is

concerned, all RAM is in consecutive 32k

pages, each page may contain 2 Blocks (a

full page of 32k), 1 Block (a half page

of 16k) or may be empty. With a full

512K of memory, "standard" MTX mapping

would have 32k in all RAM pages, apart

from Page 15 which would contain a half

page in Block 2, Block 1 being empty. |

|

Later

Memotech systems, including the MTX512S2 (256KB RAM), also used paging for the

additional memory - although the paging logic for

the S2 was flawed and only a maximum of

208KB was actually available (as described on

Andy Key's hardware page).

|

RAM Only Mode (RELCPMH = 1)

| Function |

Paged RAM |

Common Block |

| Size (KB) |

48 |

16 |

| Address Range |

0000h to BFFFh |

C000h to FFFFh |

In the same way as in ROM mode, in

RAM only mode, the upper 16k block of

RAM is common to all RAM pages, but

without the need to allocate space for

the ROMs, RAM is paged in up to16 pages

of 48k, between 0000h and BFFFh.

This gives a theoretical maximum of 784k

of RAM (16x48 + 16) but is limited by

the 512kb RAM chip used. |

|

|

MTXPlus+ ROM Configuration

The single 128KB

ROM on the CPU board will contain copies of the Memotech OS, BASIC, ASSEM,

CP/M and SDX ROMs, as well as the support ROM for MTXPlus.

| MTXPlus ROM Map |

|

Address |

Image |

A15 |

A14 |

A13 |

| 0000-1FFF |

OS |

0 |

0 |

0 |

| 2000-3FFF |

ASSEM |

(ROM 1) |

0 |

0 |

1 |

| 4000-5FFF |

BASIC |

(ROM 0) |

0 |

1 |

0 |

| 6000-7FFF |

(not used) |

(ROM 2) |

0 |

1 |

1 |

| 8000-9FFF |

(empty) |

(ROM 3) |

1 |

0 |

0 |

| A000-BFFF |

FDX |

(ROM 4) |

1 |

0 |

1 |

| C000-DFFF |

SDX |

(ROM 5) |

1 |

1 |

0 |

| E000-FFFF |

MTX+ support |

1 |

1 |

1 |

The OS and BASIC ROMs are

assembled as a single 16k unit just like the MTX-04

board. |

|

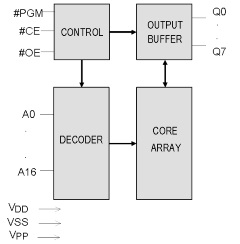

Winbond W27C010

block diagram |

|

|

|

The

decode logic for the on-board ROMs will be done in the CPLD,

should additional ROMs be needed in future, the will need to

be decoded on their own I/O board.

Some customisation has been done on the

original MTX OS ROM to integrate the enhanced features if

MTXPlus+ with the original OS, this is describe on the

MTXPlus+ ROM page.

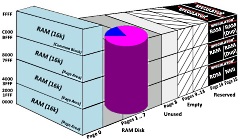

MTXPlus+ RAM Configuration (RELCPMH = 0)

The base design of MTXPlus+ supports a maximum of 512KB of

RAM using a single 512KB SRAM, using the same page size (32KB) and

window (4000h and BFFFh) as the original MTX series.

When CF support

was added, a FAT32 structure was used

and a 32k block

of memory was reserved to provide a

data buffer for the Compact Flash drive.

This page was "hidden" above what

MTX BASIC can normally see by moving the

empty block to Page 14 block 1.

Finding the empty block here, MTX BASIC

will not attempt to use Page 15.

When the CF file structure was

changed to CP/M, this reserved block was

no longer used. |

|

|

With 32k having been reserved and

hidden from MTX BASIC, PRINT PEEK(64122) returned

"14", signifying that 14 + 1, i.e., 15 x 32k pages of RAM

(480k) were available to BASIC. |

When Speculator+

support was added, the 32k buffer was increased to

64k to provide 4x16kb pages of protected RAM for

Speculator+ use, by moving the empty block to Page

13 block 1.

More details of the Speculator+

memory map are on the

Speculator+

page. |

|

|

With 64k having been reserved and hidden from MTX

BASIC, PRINT PEEK(64122) now returns

"13", signifying that 13 + 1, i.e., 14 x 32k pages of RAM

(448k) are available to BASIC. |

MTXPlus+ RAM Configuration (RELCPMH = 1)

| When Speculator+

is not running, RAM mode (RELCPMH = 1)

is most likely to be used for running

CP/M. |

|

Since CP/M 2.2

can only use 64k of RAM, the best use

for the remaining memory 384k (448 - 64)

is for a RAM disk. The closest standard

sized RAM disk is Type 52 (320 k),

configured from CP/M by

RECONFIG F:52

This

leaves 64k unused - as much as the

MTX512 had in the first place ! |

|

|