# Designer's manual

#### LIST OF CONTENTS

|     |                   |             |        |             |        |     |    |   |   |   |   |   |   | Page  |

|-----|-------------------|-------------|--------|-------------|--------|-----|----|---|---|---|---|---|---|-------|

| 1.  | Introduction      |             |        | •           |        |     |    |   | • |   |   |   |   | . III |

| 2.  | Technical Aspects | s .         |        |             |        | •   | •  |   |   | • | • |   |   | . 1   |

| 3.  | Loading and Con   | npatibility |        |             |        | •   | •  |   | • |   | • | • | • | . 5   |

| 4.  | Use of TTL.       |             | •      | •           |        |     |    | • | • |   |   | • | • | . 9   |

| 5.  | Quality and Relia | ability     | •      | •           |        |     | •  | • |   | • | • | • | • | . 27  |

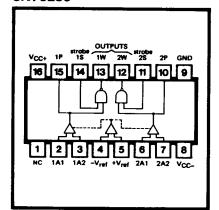

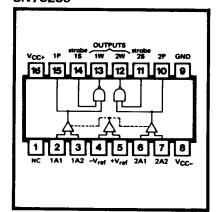

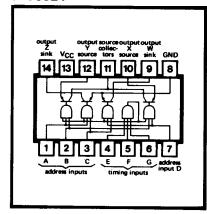

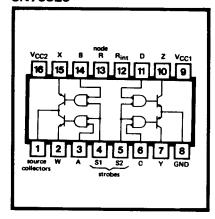

| 6.  | Ordering Instruct | tions .     | •      | •           |        |     | •  |   | • |   | • |   | • | . 34  |

| 7.  | Mechanical Data   |             |        |             | •      | •   |    | • | • | • | • | • | • | . 35  |

| 8.  | Circuit Selection | Guide       |        |             | •      | •   |    | • |   | • | • | • | • | . 37  |

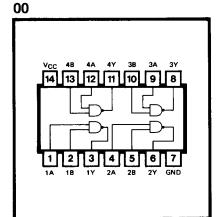

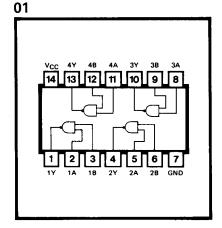

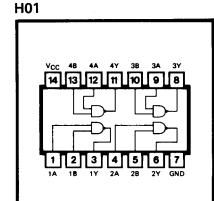

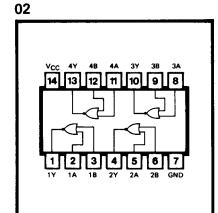

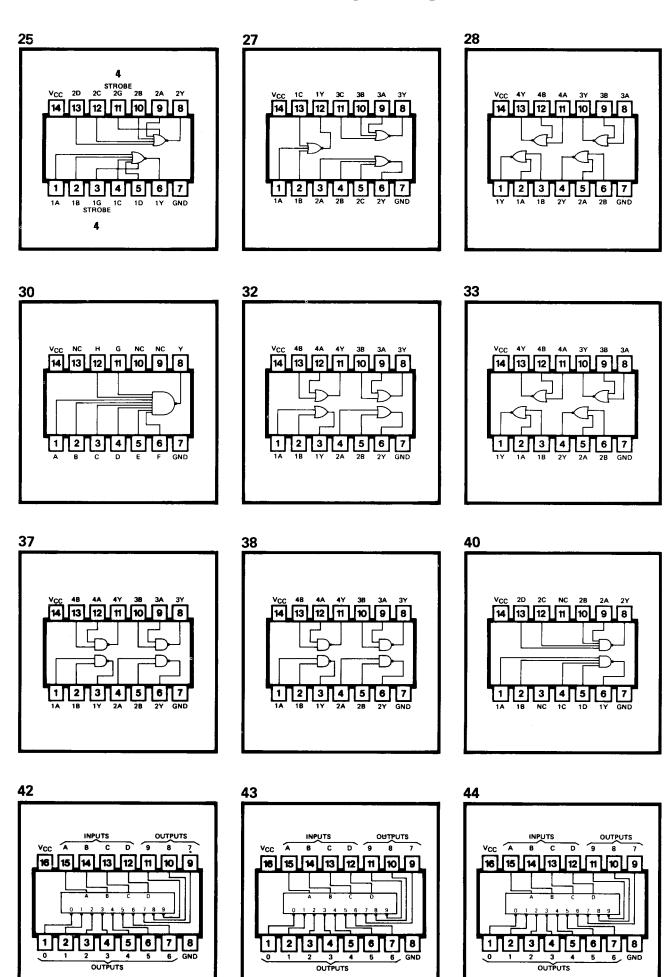

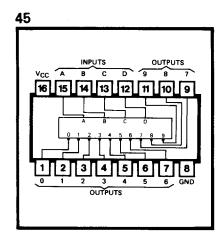

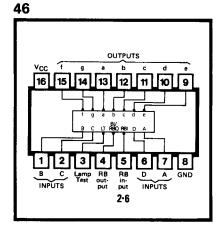

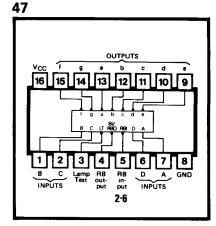

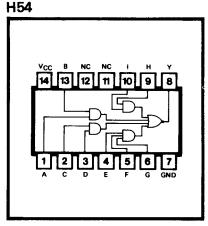

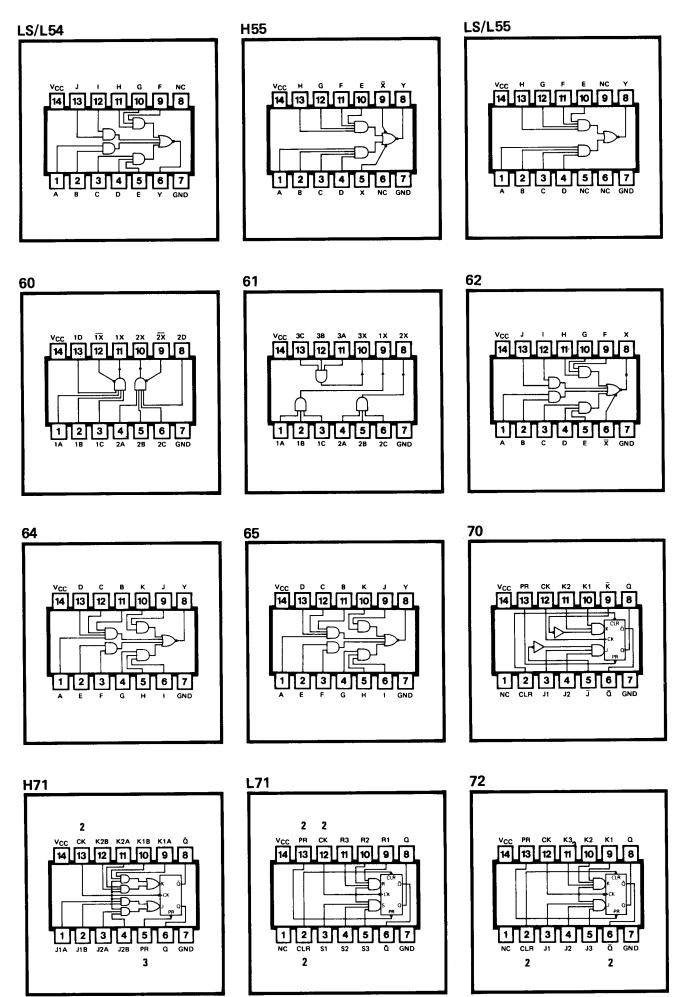

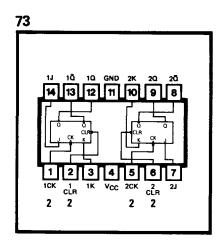

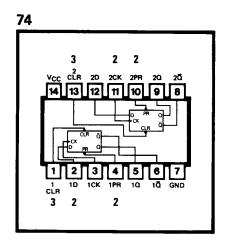

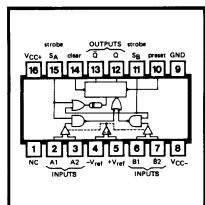

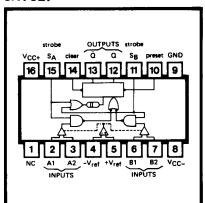

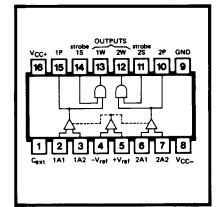

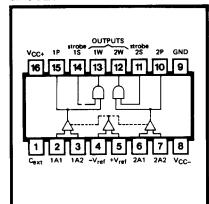

| 9.  | Pin Configuration | n Guide     | •      | •           | •      | •   | •  | • | • | ٠ | • | • | • | . 43  |

| 10. | Applications of   | TTL Logic   | ;      |             |        |     |    |   |   |   | • |   | • | . 65  |

|     | (i)               | Gates       |        |             |        |     |    |   |   | • | • | • | • | . 67  |

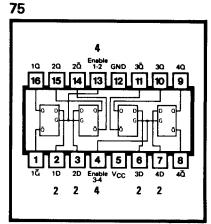

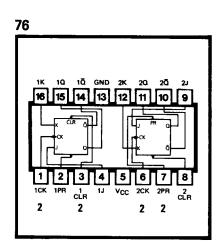

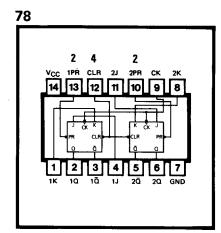

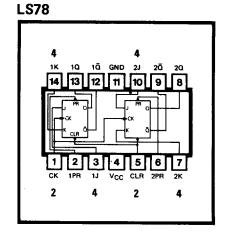

|     | (ii)              | Flip Flop   | s and  | Cou         | ınters |     |    | • | • | • | ٠ | • | • | . 75  |

|     | (iii)             | Shift Reg   |        |             |        | •   |    |   |   |   | • | • | • | . 87  |

|     | (iv)              | Decoders    | and    | Mult        | iplex  | ers |    |   | • | • | • | • | ٠ | . 91  |

|     | (v)               | Arithmet    | ic De  | vices       |        |     |    |   |   | • |   | • | ٠ | .101  |

|     | (vi)              | Monosta     | bles   |             | •      |     |    |   |   | • | • | • | • | . 121 |

|     |                   |             |        |             |        |     |    |   |   |   |   |   |   | . 125 |

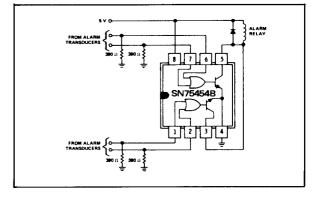

| 11. | Applications of   | Interface   | Device | es<br>• • • | •      | •   | •  | • | • | • | • | • |   | . 127 |

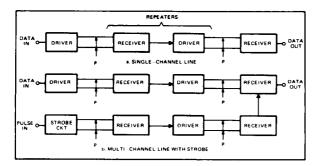

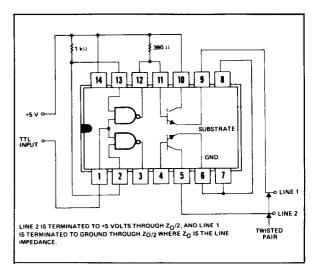

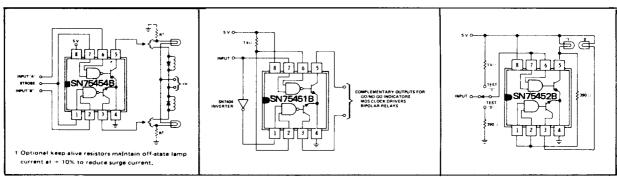

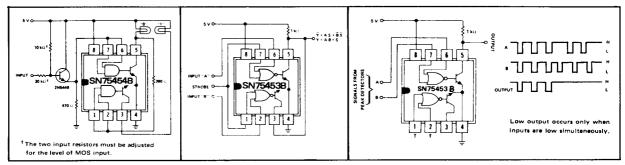

|     | (i)               | Line Dri    |        |             |        |     | 1: |   | • | • | • | • | • | . 135 |

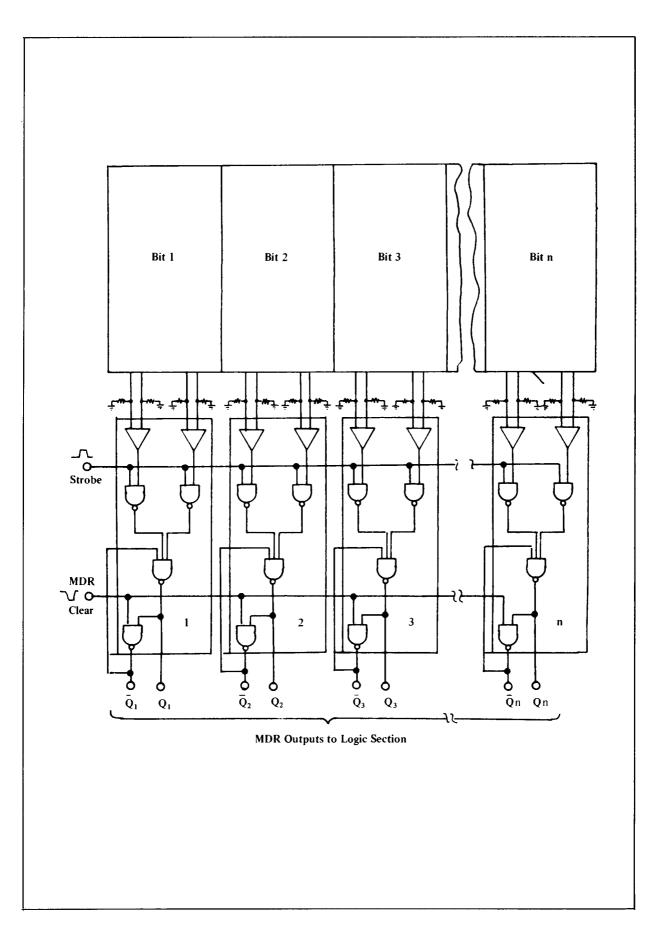

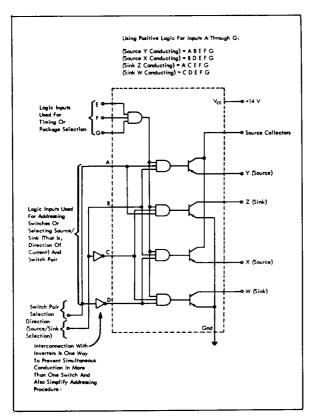

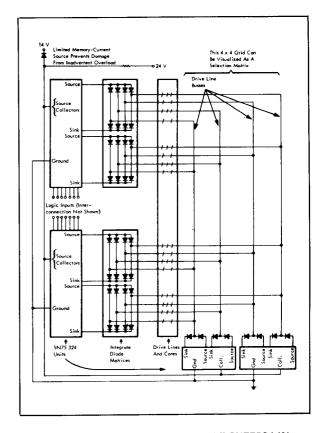

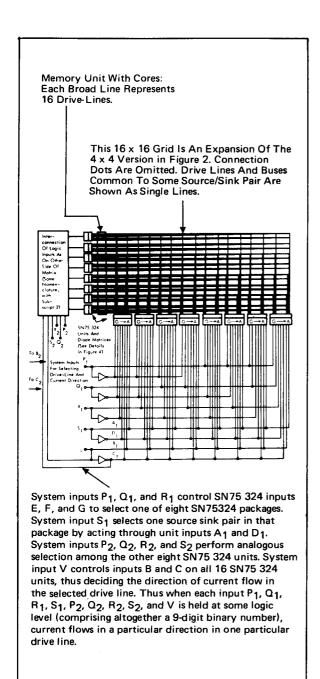

|     | (ii)              | Memory      |        |             |        |     |    |   |   | • | • | • | • | . 153 |

|     | (iii)             | Peripher    | al Dri | vers        | •      | •   | •  | • | • | • | • | • | • | . 155 |

| 12. | Applications of   | Memory I    | Device | s           |        |     | •  | • |   | • | • |   |   | .159  |

| 13. | Bibliography      |             | . •    | •           |        |     |    | • | • |   | • | • | ٠ | . 167 |

Copyright © 1973 by Texas Instruments Limited. All Rights Reserved. This publication, or parts thereof, may not be reproduced in any form without permission of the publisher, Texas Instruments Limited.

Texas Instruments reserves the right to make changes at any time in order to improve design and supply the best product possible. Information contained in this publication is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patents or rights of others which may result from its use. No licence is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

### Introduction

#### **SYSTEM 74 INTRODUCTION**

System 74 is a new look at logic design.

Texas Instruments have the justifiable reputation for anticipating the needs of designers with the continued introduction of technically innovative devices. To complement this technical capability we now introduce System 74. The most comprehensive service to designers of logic equipment. It is your guarantee of quality, reliability, economy and service, and is available only from Texas Instruments Ltd. and the approved System 74 Distributors.

System 74 starts with a range of over 300 TTL and TTL compatible devices from these 6 major families:

| SN74N   | Standard TTL              |

|---------|---------------------------|

| SN74LN  | Low Power TTL             |

| SN74LSN | Low Power Schottky TTL    |

| SN74HN  | High Speed TTL            |

| SN74SN  | High Speed Schottky TTL   |

| SN75N   | TTI. Compatible Interface |

But System 74 is more than just this.

Logic design is complex. To optimise your systems for speed, power, reliability, and economy, you will want to mix all the families contained in System 74.

Take an example

This immediately poses some questions:-

- 1. Will it work?

- 2. How can I compute the loading?

- 3. How reliable will it be?

- 4. Can I modify it?

- 5. Can I buy all the devices from one source and can I be sure that they will be compatible?

This Manual shows a way of answering these questions in minutes. It contains full information on devices and pin-outs, and extensive sections on the application of TTL and interface devices. Also included are sections on quality and reliability together with a unique method of computing interfamily loading.

In the unlikely event that you find a question that cannot be answered by this manual the System 74 Technical Enquiry Service is now available at Texas Instruments—Dial Bedford 67466, ask for System 74 and you will be connected to the World's largest semiconductor manufacturers.

System 74 is also a new pricing concept. For the first time the Design Engineer is given mixed pricing on list price quantities across all the families.

Now you can buy all your devices on the same order and qualify for the price of the total quantity mix.

This not only saves money but simplifies purchases on Design Quantities. We call it "One Stop Shopping" and think you will find this a great advantage.

The field of logic design will continue to grow with the introduction of new technologies and more complex devices. System 74 will keep you up to date with all these developments as they happen. Ask us to add your name to the System 74 mailing list by completing the card at the back of this book.

## Technical Aspects

#### **TECHNICAL ASPECTS OF SYSTEM 74**

As suggested in the introduction to this manual, System 74 allows the designer to readily select from around 300 TTL compatible functions. In order to make this an attractive and practical philosophy, the basic characteristics and parameters of the individual families comprehended in System 74 are presented in this manual to allow the reader to make a comparative evaluation of the five TTL ranges available. The information presented does not replace the comprehensive data sheets available but is intended to outline the basic compatibility of all 74 series TTL products and their relationship to the 75 series of interface devices.

The basic family in System 74 is the SN 74N series transistor—transistor logic, and a thorough discussion of the history and evolution of this popular form of digital integrated circuit logic is given in Application Report B124. The complete range of product included in System 74 is contained in the Selection Guide section of this manual.

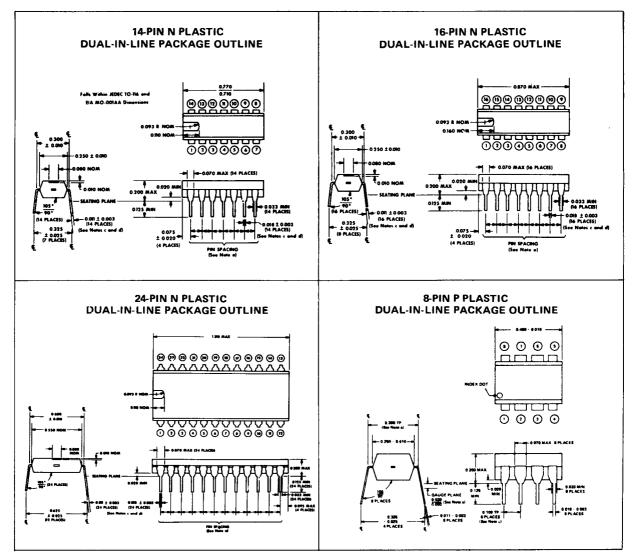

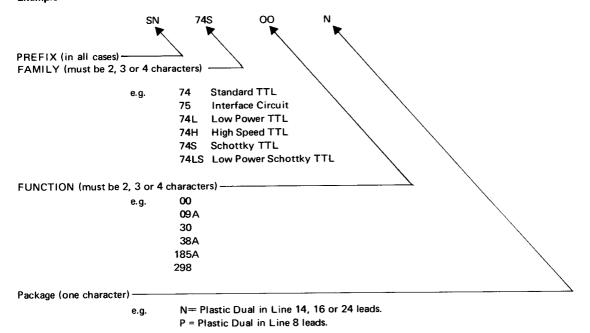

All System 74 products are offered in the commercial  $0^{\circ}$ C to  $70^{\circ}$ C operating temperature range and are packaged in "plastic" dual-in-line N Pack. The product ranges included are as follows:-

| SN74N   | Standard TTL           |

|---------|------------------------|

| SN74LN  | Low power TTL          |

| SN74LSN | Low power Schottky TTL |

| SN74HN  | High speed TTL         |

| SN74SN  | Schottky TTL           |

| SN75N   | Interface devices      |

|         |                        |

The SN74 series ranges have basically similar circuit design, logic capability and operate on similar voltage levels. The differences are those of speed and power dissipation. For example, SN74LN has very low dissipation and hence has a low speed of operation, and SN74SN is fast and consumes a greater power. This can be summarised as in Table 1 using typical gate characteristics for power dissipation and propagation delays:-

| PARAMETER                                | 74L            | 74L*            | 74LS            | 74              | 74H             | 74S              | UNIT |

|------------------------------------------|----------------|-----------------|-----------------|-----------------|-----------------|------------------|------|

| Typical Propagation Delay                | 33             | 20              | 10              | 10              | 6               | 3                | ns   |

| Typical Power Dissipation                | 1              | 5               | 2               | 10              | 22              | 20               | mW   |

| Speed/Power Product                      | 33             | 100             | 20              | 100             | 132             | 60               | PÍ   |

| Flip-Flop Clock Input<br>Frequency Range | DC to<br>3 MHz | DC to<br>20 MHz | DC to<br>45 MHz | DC to<br>35 MHz | DC to<br>50 MHz | DC to<br>125 MHz |      |

MOTE: SN74L\*N devices are those low power products derived from SN74 series which are half-power versions of the standard products. These are identified in the selection guide by use of setterisks.

The speed/power product in picojoules is a commonly accepted figure of merit for integrated circuit families obtained by multiplying typical propagation delay in nanoseconds by typical power dissipation in milliwatts. As would be expected the most recently designed families are demonstrably improving this measure, (with 74LS at 20 picojoules offering the best speed/power product). It should be remembered that speed/power product is derived from typical gate parameters and that complex functions can improve this considerably. Thus, a speed/power product for a System 74 system using principally complex functions will be better than an equivalent system built using gates.

SN75 series includes functions such as line drivers and line receivers, memory drivers, sense amplifiers, and peripheral drivers to provide TTL compatible interfaces with transmission lines, core and MOS memories, and simple interfaces to relays, lamps and other electromechanical devices. All SN75 series products specified in the selection guide have SN74 series compatible inputs or outputs, as relevant, and with few exceptions have parameters similar to standard SN74 TTL.

Before deriving and considering the D.C. parameters of System 74 TTL families the significance and notation of these parameters will be discussed.

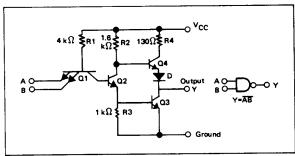

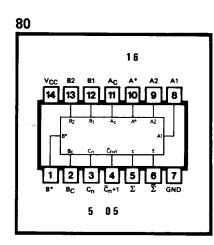

Fig. 2. Schematic diagram and logic symbol for SN74 NAND gate.

The output shown for this gate is similar to all active pullup output devices throughout System 74 and is subject to two voltage parameters.

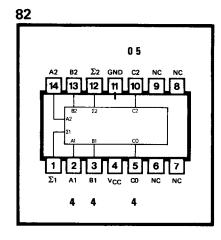

V<sub>OL</sub> is maximum low state output voltage when driving full load (i.e. maximum fan-out)

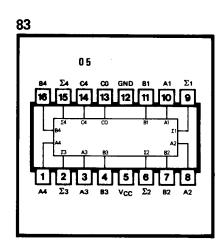

V<sub>OH</sub> is minimum high state output voltage when driving full load (i.e. maximum fan-out)

These parameters, thus, fully determine the worst-case voltage swing of the output.

The inputs are similarly subjected to voltage parameters.

V<sub>IL</sub> is maximum input voltage guaranteed to appear as a low state input voltage.

V<sub>IH</sub> is minimum input voltage guaranteed to appear as a high state input voltage.

These parameters fully determine the worst case voltage operating thresholds of an input. All voltages are positive w.r.t. the ground or zero voltage terminal.

The voltages are accompanied by current parameters, which obey the following convention. Currents flowing into inputs or outputs are positive and those flowing out of inputs or outputs are negative.

$I_{\mbox{OL}}$  is maximum positive current into a low state output at not more the  $V_{\mbox{OL}}$

I<sub>OH</sub> is maximum negative current out of a high state output at not lower than V<sub>OH</sub>

These parameters indicate the capability of an output to drive inputs of other functions.

$I_{IL}$  is maximum negative current out of an input held at  $V_{OI}$

$I_{\mbox{\footnotesize IH}}$  is maximum positive current into an input held at  $V_{\mbox{\footnotesize OH}}$

These parameters indicate the input requirements with worst case driving voltages.

Other parameters and operating conditions are specified in the data sheet and once again Application Report B124 provides excellent background.

The basic parameters outlined above will be used to compare the families in System 74 to estimate worst case noise immunities and drive capability and demonstrate the basic compatibility that exists across all System 74 TTL families.

#### **SYSTEM 74 D.C. PARAMETERS**

|     | SN74L | SN74L* | SN74LS | SN74  | SN74H | SN74S | UNITS |

|-----|-------|--------|--------|-------|-------|-------|-------|

| VOL | 0.3   | 0.4    | 0.5    | 0.4   | 0.4   | 0.5   | V     |

| VOH | 2.4   | 2.4    | 2.7    | 2.4   | 2.4   | 2.7   | V     |

| IOL | 2.0   | 8.0    | 8.0    | 16.00 | 20.00 | 20.00 | mA    |

| IOH | -200  | -400   | -400   | -400  | -500  | -1000 | Aμ    |

| VIL | 0.7   | 0.8    | 0.8    | 0.8   | 0.8   | 0.8   | v v   |

| ViH | 2.0   | 2.0    | 2.0    | 2.0   | 2.0   | 2.0   | v     |

| ηL  | -0.18 | -0.8   | -0.36  | -1.6  | -2.0  | -2.0  | mA    |

| ΊΗ  | 10.00 | 20.00  | 20.00  | 40.00 | 50.00 | 50.00 | μA    |

This chart pulls out from the data, those parameters having significant effect on inter-range compatibility. All devices operate with a positive supply voltage of nominally 5 volts and have similar absolute maximum ratings for supply and applied input voltages. The tabulated values apply only to active pullup output devices with inputs of unit load. Thus, flip-flops and other devices having inputs which represent two or more loads and also devices with open collector, resistive pull-up or buffer outputs, represent special cases.

#### **NOISE IMMUNITY**

Worst case D.C. noise immunity is a primary consideration and is defined as follows:-

D.C. noise immunity is the Difference between input threshold and input voltage applied using worst case values.

Thus: Low state Noise Immunity =  $V_{IL} - V_{OL}$ High state Noise Immunity =  $V_{OH} - V_{IH}$

A comparison across the range reveals the following results:-

|   |                            | SN74L        | SN74L*       | SN74LS       | SN74         | SN74H        | SN74S        |                             |

|---|----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|-----------------------------|

| • | NOISE<br>IMMUNITY<br>VOLTS | 0.4v<br>0.4v | 0.4v<br>0.4v | 0.3v<br>0.7v | 0.4v<br>0.4v | 0.4v<br>0.4v | 0.3v<br>0.7v | (low state)<br>(high state) |

The worst case across the range is SN74LSN or SN74SN driving SN74L when low state noise immunity is 0.2V. (see table above).

These results indicate a favourable condition of overall noise immunity in a system employing products from all the ranges, bearing in mind that worst-case D.C. noise immunity is really a guarantee of worst case operation and typical noise immunities are closer to 1.0 volts for both low and high states.

Fan-out is the term used to describe the capability of our output to drive inputs. This is normally specified within a range and is guaranteed as follows:—

LOW STATE FAN-OUT = IOL - IIL HIGH STATE FAN-OUT = IOH - IIH

This gives the results:-

|         |            | SN74L | SN73L* | SN74LS | SN 74  | SN74H | SN 74S |

|---------|------------|-------|--------|--------|--------|-------|--------|

| FAN-OUT | LOW STATE  | 20    | 10     | 20     | 10     | 10    | 10     |

| PAN-001 | HIGH STATE | 20    | 20     | 20     | 10(20) | 10    | 20     |

Thus the commercial ranges of SN74LN and SN74SN have a fan-out of 20 in the high state only. All recent devices in standard SN74N also provide a high state fan-out of 20 and where this becomes important the data sheet should be checked.

It is possible to derive fan-outs from range to range by using the simple formulae above and this together with a rationalised approach to estimating System 74 inter-range fan-out is presented in the section on Loading and Compatibility.

This discussion on the technical aspects of System 74 has listed the product ranges initially offered. A comparison of the ranges from both an A.C. and a

D.C. point of view has established that a philosophy of both horizontal and vertical selection of devices can offer the designer not only an effective increase of functions available, but also, the opportunity to optimise system design for speed and power dissipation.

## Loading and Compatibility

#### LOADING AND COMPATIBILITY

In the previous section on the technical aspects of System 74 sufficient basic information is supplied to show that all the products offered share a similarity of characteristics allowing them to be used together. They are fully compatible.

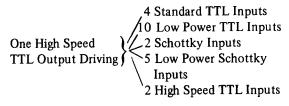

The principal aim of this section is to demonstrate a method of inter-range Fan-Out computation that is simple, effective and allows optimal specification of each range. The argument is based on the SN74N ranges of TTL, but SN75N series Interface products can be considered as standard SN74N in that their designed capability to drive or be driven from TTL is parametrically based on standard SN74N.

Having demonstrated that the TTL ranges of SN74LN, SN74LSN, SN74HN, SN74N and SN74SN are completely compatible with regard to operating voltage levels, it becomes an elementary exercise to derive inter-range fan-out by respectively considering the current output capabilities of the different ranges and the input current requirements. The following matrix chart shows the result of calculating D.C. fanout across all the TTL ranges.

|        |      | DRIVING |      |      |      |      |      |  |  |  |  |

|--------|------|---------|------|------|------|------|------|--|--|--|--|

|        |      | 74L     | 74L* | 74LS | 74   | 74H  | 748  |  |  |  |  |

|        | 74L  | 5       | 2.5  | 2.5  | 2.5  | 2.0  | 1.0  |  |  |  |  |

|        | 74L* | 20      | 10.0 | 10.0 | 5.0  | 4.0  | 4.0  |  |  |  |  |

| Ü      | 74LS | 10      | 5.0  | 5.0  | 5.0  | 4.0  | 2.0  |  |  |  |  |

| DRIVEN | 74   | 40      | 20.0 | 20.0 | 10.0 | 8.0  | 8.0  |  |  |  |  |

|        | 74H  | 50      | 25.0 | 25.0 | 12.5 | 10.0 | 10.0 |  |  |  |  |

|        | 74S  | 50      | 25.0 | 25.0 | 12.5 | 10.0 | 10.0 |  |  |  |  |

#### SYSTEM 74 INPUT WEIGHTING CHART (STANDARD OUTPUT-UNIT LOAD)

#### **Notes**

- 1. This chart applies only to standard outputs driving unit load inputs. Buffer outputs, open-collecter outputs and resistive pull-up outputs are considered separately, as are greater than unity load inputs.

- SN74L\* includes half power versions of standard SN74 as identified by asterisks in the Selection Guide.

As stated, the fan-outs shown are calculated simply by considering the current parameters contained in the data sheets of each range. It should be noted that in most cases the fan-out is limited by the low-state output sink current. In other cases the fan-out is limited by the high-state output source current. Some examples of different cases are given.

|     | SN74L | SN74L* | SN74LS | SN74 | SN74H | SN74S      | UNITS |

|-----|-------|--------|--------|------|-------|------------|-------|

| lOL | 4.0   | 8.0    | 8.0    | 16.0 | 20.0  | 20.0       | mA    |

| IOH | 200   | 400    | 400    | 400  | 500   | -1000      | μA    |

| IH  | 10.0  | 20.0   | 20.0   | 40.0 | 50.0  | 50.0       | μA    |

| IIL | -0.18 | -0.8   | 0.36   | 1.6  | 2.0   | <b>2.0</b> | mA    |

SYSTEM 74 D.C. CURRENT PARAMETERS (STANDARD OUTPUT-UNIT LOAD)

#### EXAMPLE ONE

SN74 TO SN74L LOW STATE FANOUT IS  $\frac{16 \text{ mA}}{0.18 \text{ mA}}$  = 88 SN74 TO SN74L HIGH STATE FANOUT IS  $\frac{400 \text{ mA}}{10 \text{ mA}}$  = 40

LIMITING CASE IS HIGH STATE FANOUT OF 40

#### **EXAMPLE TWO**

SN74S TO SN74H LOW STATE FANOUT IS  $\frac{20 \text{ mA}}{2 \text{ mA}} = 10$ SN74S to SN74H HIGH STATE FANOUT IS  $\frac{1000 \text{ mA}}{50 \text{ mA}} = 20$

LIMITING CASE IS LOW STATE FANOUT OF 10

An appreciation of this mechanism is necessary. Where the high state fan-out is greater than the low state, it is permissible to connect unused inputs to used inputs since this has no effect on low state fan-out but does increase high state fan-out requirements. In fact SN74S, SN74L\* devices and recently introduced SN74N products are specified to provide high state fan-outs of 20 and low state fan-outs of 10 specifically to deal with unused inputs. SN74L and SN74LS devices provide fan-outs of 20 in either state.

This derivation and charting of fanout rules provides useful information, but does leave a signifi-

cant question unanswered. Where for example an SN74 output is driving a combination of inputs from some or all of the other ranges, the designer is still faced with the task of computing, in terms of input currents, the total loading effect. Thus, the fanout chart given is useful in computing the fan-out situation where the driven inputs are all from the same range. To improve the overall usefulness a normalising technique is applied to the fan-out chart.

Divide all fan-out values into 100 provides the following Input Weighting Chart.

|   |                   |     | DRIVING |      |      |      |      |  |  |  |  |

|---|-------------------|-----|---------|------|------|------|------|--|--|--|--|

|   |                   | 74L | 74L*    | 74LS | 74   | 74H  | 74\$ |  |  |  |  |

|   | 74L               | 5   | 2.5     | 2.5  | 2.5  | 2.0  | 1.0  |  |  |  |  |

| _ | 74*               | 20  | 10.0    | 10.0 | 5.0  | 4.0  | 4.0  |  |  |  |  |

|   | 74*<br>74L*<br>74 | 10  | 5.0     | 5.0  | 5.0  | 4.0  | 2.0  |  |  |  |  |

| E | 74                | 40  | 20.0    | 20.0 | 10.0 | 8.0  | 8.0  |  |  |  |  |

|   | 74H               | 50  | 25.0    | 25.0 | 12.5 | 10.0 | 10.0 |  |  |  |  |

| ļ | 74S               | 50  | 25.0    | 25.0 | 12.5 | 10.0 | 10.0 |  |  |  |  |

SYSTEM 74 INPUT WEIGHTING CHART (STANDARD OUTPUT-UNIT LOAD)

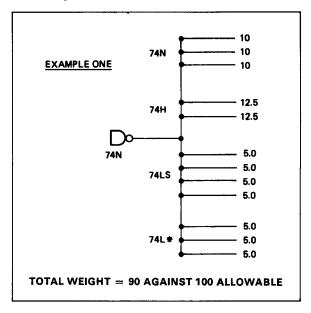

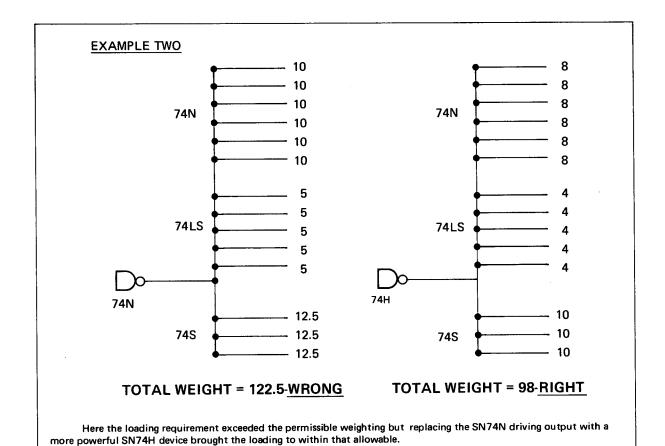

This variation of the fanout chart converts the fanout values to input weighting where the maximum weight applied to an output is one hundred. As shown the weight of a driven input is dependent on the type of driving output i.e. SN74L driven from SN74 has a weight of 2.5, or a weight of 2 when

driven by SN74H.

Thus, to compute the loading effect of a combination of inputs simply add the appropriate input weight values. Up to one hundred represents a permissible loading, greater than one hundred will cause data sheet operating conditions to be exceeded.

In this case a complex loading situation is simply computed and found to be satisfactory.

#### Notes

- The input weighting chart demonstrates the fact that System 74 allows very high fan-out situation.

For instance a standard SN74S output can drive 100 SN74L inputs and thus simplify many design problems.

- 2. The input weighting chart is derived for standard outputs driving unit load inputs. However, its use can be simply extended to other situations. Thus, an SN74 buffer driver has three times the drive capability of a standard output and this allows the weighting to be increased to 300. This applies to all buffers with normal active pull-up outputs and thus an SN74S buffer can drive 300 low power inputs.

- 3. A certain number of System 74 products have input loading of greater than unity, i.e. flip-flops. In this case the input weighting is increased in proportion to the increase in input loading above unity.

Thus, when driving the clock input of an SN74L flip flop from SN74, the input weighting shown on the chart should be increased from 5 to 10.

This system is derived from the data sheets, and they represent the most authoritative and complete source of design information. However, given an understanding of the derivation of this input weighting system, the designer has a valuable tool for quick evaluation of complex loading problems.

The most effective method for utilizing this sytem is to use it as a feasibility check. In the standard case where total allowable weighting is one hundred the following procedure is suggested:-

A RESULT OF UP TO 90 - NO PROBLEM

A RESULT OF BETWEEN 90-110-CHECK AGAINST DATA

A RESULT OF OVER 110 – FIND ANOTHER SOLUTION.

The system can be extended to any situation where it is possible to derive a loading figure from the data sheets and can be simply modified to include SN75 series products, open collector TTL functions and pull-up resistors, by adding additional rows and columns. The designer can thus maintain flexibility by generating additional information and discarding that not required for a particular project thus keeping complexity and possibility of error to an acceptable minimum.

### Use of TTL

#### **USE OF TTL**

System 74 is a very easy family of logic to use. With some types of logic there are many complications both from the logic design point of view and the system building. These add up to cost time and money before producing the final unit. Fan out calculations, the number of inputs that one gate can drive, can be different for almost every output, whereas, as seen it is very simple with System 74. The designer is also helped, more than many realise, by the multitude of complex functions which are standard catalogue items. It is no longer necessary to design an up/down counter from basic gates and flip flops. Such a function and others which are even more elaborate are now quite commonplace.

The ability to make sophisticated devices allows new techniques which would otherwise be unthinkable. An example is the use of ROM look up tables for multiplication. Another is the use of multiplexers instead of shift registers for parallel to serial conversion and vice versa. These new techniques can give a reduction in package numbers and apparent complexity.

Ambient temperature and supply voltage considerations are simpler with System 74. Due to the worse-case worse-case way in which System 74 devices are specified, provided they are nowhere outside the operating voltage and temperature ranges but no matter what the combination and distribution of voltage and temperature, then the devices will work correctly.

On top of this comes the safety margin which System 74 devices have. A typically series 74N output can sink about twice its guaranteed logical 'O' current of 16mA and still have an output voltage of less than 400mV.

Usually that output transistor will sink 40 or 50mA before it comes out of saturation. The logical '1' output current will typically be several milliamps giving an even greater safety factor.

As will have been seen there are few special considerations which need to be made. A brief look at the design of the logic and its testing will justify this.

#### **Design Characteristics**

System 74 TTL digital integrated circuit families optimize the advantages of saturated logic circuitry and monolithic semiconductor technology, yielding improved performance in the speed/power ranges which meet the needs of current and future designs. In other forms of logic circuitry (non-monolithic) maximum use is made of lower cost passive components (diodes and resistors) instead of higher performance (and higher cost) transistors. However, in monolithic circuitry it costs very little more to

build transistors than diodes or resistors. Therefore, transistors are used to take advantage of the improved performance and also to buffer the fluctuations in currents that occur as resistor values change. The TTL multiple emitter input transistor replaces conventional input diodes, and an active pull-up output transistor eliminates the slow rise times associated with passive pull-up.

Each low-capacitance emitter of the input transistor offers very little loading to the driving circuit. In addition to providing some gain when this transistor is turned on (one or more emitters at a low voltage), a low impedance path (approximately  $V_{\text{CE}(\text{sat})}$ ) is established to remove the base charge from and turn off the phase-splitter transistor. When compared to a passive-component input, the TTL input is considerably faster.

Another important feature which reduces overall switching time of the TTL circuit is the active pull-up output. In addition to reducing the turn-off time, the double-ended output provides a low-impedance path in both the logical 0 and logical 1 states for sourcing or sinking current to highly capacitive loads and for rejecting capacitively-coupled a.c. noise.

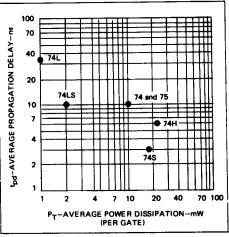

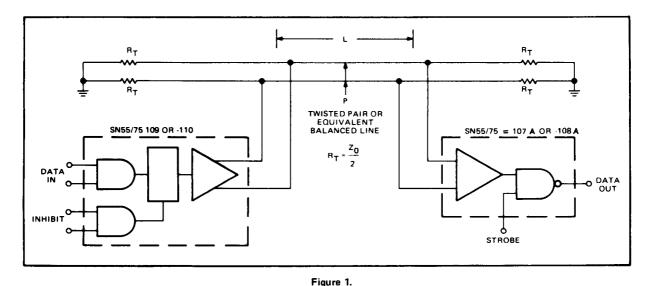

A comparison of typical saturated digital logic family speed/power products is shown in Table A and Figure 1

Table A

| Circuit      | t <sub>pd</sub> (ns) | P <sub>T</sub><br>(mW) | Speed/<br>Power<br>Product | Typical<br>Fan-Out |

|--------------|----------------------|------------------------|----------------------------|--------------------|

| 74L          | 33                   | 1                      | 33                         | 10                 |

| TTL          |                      |                        |                            |                    |

| 74           | 10                   | 10                     | 100                        | 10                 |

| TTL          | 1                    | 1                      |                            |                    |

| 74H          | 6                    | 23                     | 138                        | 10                 |

| TTL          | ļ                    |                        |                            |                    |

| DTL          | 25                   | 5                      | 125                        | 8                  |

| DCTL         | 15                   | 10                     | 150                        | 3                  |

| RCTL         | 30                   | 10                     | 300                        | 4                  |

| RTL          | 50                   | 10                     | 500                        | 4                  |

| 7 <b>4</b> S | 3                    | 19                     | 57                         | 10                 |

| 74LS         | 10                   | 2                      | 20                         | 20                 |

| 75           | 10                   | 10                     | 100                        | 10                 |

Figure 1.

Specification sheets can be misleading unless test conditions are clearly stated. One of the most important but least apparent benefits of System 74 TTL ICs is the guarantee that worst-case test conditions are used when specifications are prepared. The data sheets verify these worst case test conditions, including supply currents which are specified at maximum supply voltages.

#### **Worst-Case Temperature**

All d.c. limits shown on the data sheet are guaranteed over the entire temperature range of 0°C to 70°C. Texas Instruments guarantees one value over a temperature range since the designer is limited by whatever happens to be the worst value of a particular parameter regardless of the temperature at which it occurs.

#### **Worst-Case Loading**

For a logical one output voltage test, a guaranteed fan-out of ten is simulated by drawing at least ten times the current drawn by a worst-case input.

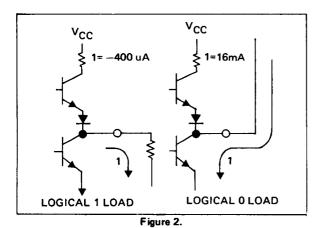

For example: 400  $\mu$ A is drawn from the output of a Series 74N gate. Since an input at 2.4V can draw no more than 40  $\mu$ A, the 400  $\mu$ A drain represents a worst-case normalized fan-out of 10. Similarly, in the logical zero state, current equal to a worst-case fan-out of ten is "sunk" into the lower output transistor. See Figure 2.

Worst-Case Supply Voltage

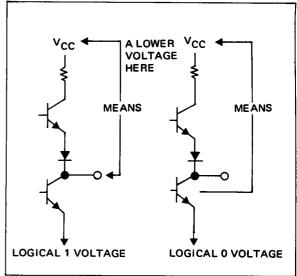

The logical one output voltage follows changes in the supply voltage practically volt for volt; therefore, when measuring logical one output levels, the worstcase supply voltage is the lowest allowable.

Similarly, the low supply voltage limit is used when a logical zero output is tested since the lower voltage reduces the base drive to the output transistor and makes it more difficult to keep the transistor in saturation. See Figure 3.

Figure 3.

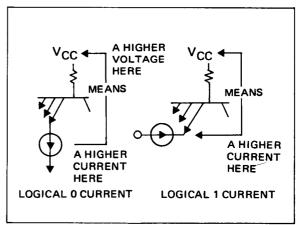

Requirements are different, though, when an input is tested. Here, the high-limit power supply voltage is used, i.e. 5.25V, since the higher voltage results in more current into and out of the input. See Figure 4.

Figure 4.

These tests are extreme since supply voltages remain generally constant throughout any given system, but worst-case testing here gives added assurance of reliable system operation.

#### Worst-Case Conditions on Unused Inputs

In addition to selecting worst case supply voltages for various output conditions, worst-case voltages are also applied to the unused inputs as shown in the illustrations.

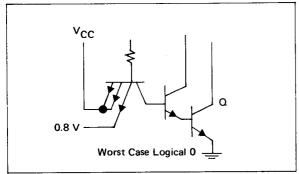

When a worst-case logical zero (0.8V) is applied to an input and where that voltage is required to hold the output transistor Q in the off state — unused inputs are returned to the maximum supply voltage. This represents the worst-case condition since these high voltages would tend to turn on the transistor Q if it were not for the low input. See Figure 5.

Figure 5.

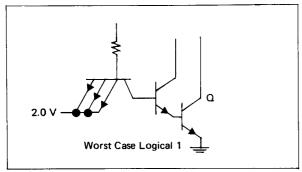

When a minimum logical one (2.0V) is applied to an input to turn on the output transistor Q, the worst case is to hold all other inputs at the minimum logical one voltage which is 2.0V. Therefore, all inputs are tied together and taken to this voltage. See Figure 6.

Figure 6.

#### **Worst-Case Supply Current**

Power supply current requirements for all System 74 TTL circuits are specified as maximum current drains with power-supply voltage at  $V_{CC} = MAX$ . When power supply currents are specified at the nominal  $V_{CC}$  (5 volts), the true worst-case current drain is not obtained.  $I_{CC}$  at nominal  $V_{CC}$  is, in fact, approximately 91% of the worst-case value, and the resulting power dissipation is approximately 82% of the worst-case value.

In summary, worst-case testing of every parameter may result in figures that look less impressive than those obtained with more typical testing, but it gives you extra assurance that every circuit will perform correctly in your system, under worst-case conditions.

With a linear system it is possible to very simply measure the performance and accuracy. A digital system however either works correctly or has faults. It is difficult to tell how near equipment is to malfunctioning. Although it has been said that there are few things to take into special consideration, there are simple guidelines which enable the best to be obtained from a system.

These general guidelines will be covered in the next few pages. Idiosyncrasies and features of individual devices will be discussed in the Applications Sections.

#### **Power Supply**

The supply voltage can be between 4.75V and 5.25V. Also different parts of the system do not have to be at the same voltage, provided it is never outside the above limits. As well as regulation only having to be 5%, ripply can also be up to 5%.

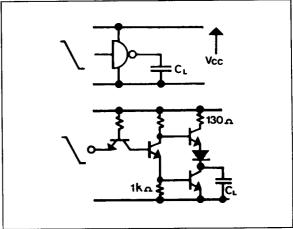

One of the things to bear in mind about power supplies for TTL systems is that not only must they cope with power consumption of the TTL circuits and any external resistors, but they must also be able to handle circuit switching transients and system capacitance at the designed operating frequency. Consider a simple TTL gate with a load capacitance  $C_{I}$ .

Figure 7.

When the input to the gate goes low there comes a point in the transition when the upper transistor in the totem pole output turns on, while the lower output transistor is still in the process of turning off due to the stored charge in the base/collector junction, discharged through the  $1k\Omega$  resistor. As a result there is a brief period in time during the transition when both output transistors are on.

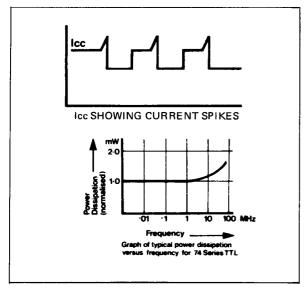

Now the dynamics of the switching and internal feedback are such that this condition only lasts for about 7ns with 74N Series TTL. The maximum current which flows down the output is not so much governed by the 130 ohm resistor (which would allow up to 25mA) but rather by the switching dynamics, and it is in fact about 8mA max. One can illustrate the current drawn by the circuit when switching as below.

The charge represented by the current spike is independent of frequency and input rise and fall times (so long as these are submicrosecond) and is about 30.  $10^{-12}$  coulombs. As the frequency rises these small spikes start to contribute to the average  $I_{CC}$  current. A graph below shows this. At 10 MHz for instance,  $I_{CC}$  =  $10^7 \times 30 \times 10^{-12}$  amps = 0.3mA. Thus  $I_{CC}$  (total) = 2.3mA =  $I_{CC}$  (DC) + 15%.

Figure 8

Now one of the other factors one should consider is the charge/discharge of load capacitance  $C_L$ , typically 15pF in a system with short lead lengths.  $C_L$  is charged from about 0.3 volts to 3.3 volts each cycle, which represents 15 x  $10^{-12}$  x 3 = 45 x  $10^{-12}$  coulombs. At 10MHz this can be expressed as follows.

$$I_{CC}$$

(capacitance) =  $10^7 \times 45 \times 10^{-12} = 0.45 \text{ mA}$ .

$$I_{CC}$$

(total) =  $I_{CC}$  (DC) +  $I_{CC}$  (transient) +  $I_{CC}$  (capacitance)

$$= 2.0 + 0.3 + 0.45 = 2.75$$

mA.

This is a typical figure for a gate circuit.

The increased system current required at 10MHz can be directly related to the number of output nodes in the system by adding the DC current to 0.75mA x the number of nodes.

From these considerations, it is possible to determine the size of power supply required. One can then arrange for the supply to have sufficient regulation and stability. Even with the best regulation some mains-borne noise can propagate through the regulator. In severe cases, R.F. filter the primary of the transformer and use one wound with an electrostatic screen.

#### Decoupling

Decoupling should be distributed on the board with 0.1  $\mu$ F ceramic capacitors for every 5 to 10 packages. These are designed to decouple high frequency noise which the logic, being fast, is capable of propagating. They must therefore be connected across the  $V_{CC}$  and ground lines (that go to the same package) by short leads and good R.F. practice. The

actual power supply, which may claim to be a low impedance, will cease to be so at frequencies above a few kilohertz. Therefore earth planes and broad tracks with decoupling are necessary to give a low impedance supply at the device.

#### Grounding

Care should be taken with the construction and layout of the logic. System 74 is fast (it has fast edges), even the low power devices. Therefore some consideration must be given to the way gates are put together. A ground plane is desirable. It can also have the  $V_{CC}$  track on the same side of the p.c.b., if it is wide and decoupled well. If this physically cannot be done, then the earth and supply rails should be as broad as possible wherever possible.

In terms of inductance, it is advantageous to parallel tracks. Paralleling two tracks is much better than doubling the width of a narrow track.

Data rise and fall times into TTL devices should be 50ns except in the case of Schmitt triggers.

If the edges are not this fast then it is possible for a gate to be affected by noise or feedback as the input voltage is at the threshold. The effect looks like a burst of oscillation as the gate output switches from one state to the other. This can of course affect bistable elements such as counters giving an apparent random change in the outputs. Slow edges usually come from input signals (or deliberate time constant circuits which should thus be avoided). Schmitt trigger gates ('13, '14 and '132), as will be seen, can be used to advantage here.

Unused inputs of ALL TTL devices should be tied to guaranteed logic levels.

An input left open circuit on the bench will act as a logical '1' input. In practise this should definitely not be done. Again it can be connected to  $V_{CC}$  but this should be done with caution.

One of the first things to remember is that even the most stable power supplies can have transients. In most industrial applications these days it is usual to see considerable coupling of external noise sources (controllers, motors, contactors, etc.) into power supply distributions in logic systems.

It is unwise to tie up unused inputs to  $V_{CC}$  since in most environments it is difficult to maintain power supplies within the 5.5 volt rating demanded by this. There are four alternatives:

- 1. Leave them open circuit.

- 2. Tie them to V<sub>CC</sub> through a current limiting resistor.

- 3. Tie them to the output of an unused gate held in the one state.

- 4. Common them with another input on the same gate and drive them.

Whilst "1" is satisfactory for gates, it slows down propagation delay because the capacitance to ground associated with the input (bond wire, package pin, etc. approx. 1.5pF) adds an extra time constant in the tpd(o) equivalent to about 1.0 ns.

Data inputs to flip-flops and counters should always be tied somewhere, and preset/clear lines MUST be tied to a voltage. This is because of high regeneration from preset/clear lines which causes latching to occur for much lower levels of noise energy.

"2" is satisfactory, but requires an external component. The value of the resistor should be a minimum of 750 $\Omega$ . The capacitance-to-ground time constant is eliminated, but there is still emitteremitter capacitance accounting for approximately 0.5

ns delay in  $t_{pd(o)}$ .

"3" is a very good method since unused inputs are then in the same environment as driven inputs, i.e. a low impedance system (Z. out (1)  $\approx 100\Omega$ ) with two diodes up to  $V_{\mbox{\footnotesize{CC}}}$  for over-voltage protection. Speed

is the same as "2

"4". If there is spare fan-out capability in the system, commoning up inputs results in optimum speeds, since all stray capacitance associated with inputs is being driven from low impedance. For the purposes of fan-out computation, two inputs paralleled (on the same gate) have a fan-in of 1 in the zero state, and may be taken as 1.5 in the high state. System 74 TTL has, in many cases, a fan-out of 10 in the low state, and 20 in the high state, allowing extensive commoning of inputs for optimum speed.

#### Summarizing:

Do not, if possible, tie spare inputs to  $V_{CC}$ .

Do not, if possible, leave gate inputs floating.

Do not, if at all possible, leave date inputs floating.

NEVER leave preset or clear lines floating.

In small to medium systems, try to tie unused inputs to a spare gate held in the one state - if this is not possible, use a resistor to V<sub>CC</sub>. In large systems, drive all spare inputs for optimum speeds.

#### INPUT RATINGS

#### **Positive Rating**

The date sheets guarantee a 5.5 volt rating on inputs with a 1mA current maximum. Essentially this guarantees a breakdown condition on the input rather than a leakage current, and TI test for the worst case configuration with other inputs at earth.

In this way TI guarantee the base emitter breakdown voltage of the input under test and include the effect of all the currents flowing as a result of the emitter - emitter gain in the multi-emitter transistor. The base of the transistor sits a V<sub>BE</sub> above earth, and therefore the actual junction breakdown is guaranteed at  $5.5 - V_{BE} = 4.8$  volts.

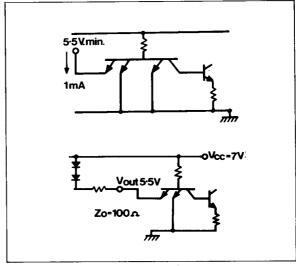

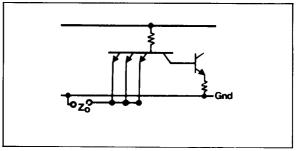

When driving the input from another TTL gate in the one state, the driven input sees about 100 ohms in series with two diodes as shown below.

Figure 9

When  $V_{\mbox{\footnotesize{CC}}}$  rises above the recommended operating limits of 5.25 to 7 volts - the maximum rating for System 74 devices – the  $V_{out}$  of the driving gate rises to about 1.5 volts below  $V_{CC}$ , i.e. 5.5 volts which represents the DC rating of the following gates' input.

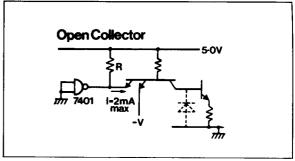

So when you're driving into TTL from any device with a resistive pull up to V<sub>CC</sub>, there's no V<sub>BE</sub> limiting like we have in the TTL stage outlined above, and in these circumstances you must define a minimum value for resistor R to limit the breakdown current which will flow into the TTL input under V<sub>CC</sub> fault conditions. We recommend a minimum value for this resistor of 750 ohms. This limits the maximum breakdown current in any input to 2mA which is a safe value to use as a DC rating.

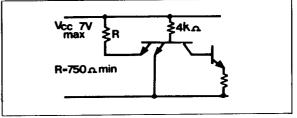

If you need a lower value resistor (for instance to increase the wired AND capability of open collector TTL devices) then you can make use of the higher breakdown voltage obtained if other inputs are not at earth, but tied together.

Figure 10.

The base of the multi-emitter transistor will now sit at 2.1 volts and the breakdown voltage seen at the emitters will be 4.8 + 2.1 = 6.9 volts. And only a nominal current limiting resistor, R, of 100 ohms is needed for a maximum  $V_{CC}$  rating of 7 volts. This gives plenty of scope for a wide wired AND application. In all cases it is preferable to use the highest value resistor possible up to 1 kilohm, consistent, of course, with the application.

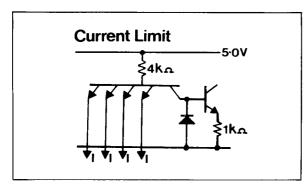

Negative transients caused by switching on transmission lines are well within the device rating, so they are no problem. However, DC ratings are governed by a current or a voltage limit, whichever is the more stringent, and they are defined as follows:

Figure 11.

The current above is drawn from the substrate via the collector isolation diode shown -1 = 5mA per input maximum or 25mA total, whichever is smaller.

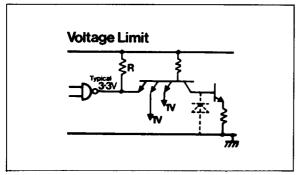

Now for voltages, the limit in the configuration shown below is limited by the 5.5 volt emitter — emitter DC breakdown condition, and therefore the maximum negative voltage guaranteed on the inputs is -2.2 volts.

Figure 12.

As with positive voltages greater than 5.5 volts, there is also a limit with negative voltages above the 5.5 volt rating, and a maximum current limit of 2mA must be observed into any input.

Consider the circuit below. Here the maximum negative value for V is given by  $I_{max} = 2mA$  (DC rating), so where V = -2.2 volts maximum this gives  $R_{min} = 850$  ohms with a nominal  $V_{CC}$  of 5.0 volts.

Figure 13.

It is not recommended to use System 74 devices with inputs taken to negative voltages. However, if this is really necessary, one can make use of the increased negative voltage rating available by driving all the inputs together as shown in the circuit below.

Figure 14.

In this way no emitter breakdown can occur and it ensures that the  $Z_0$  of the source is sufficient to limit the current to 5 mA per input (one can safely assume equal current sharing).

Increased fan out can be obtained by paralleling devices in the same package.

Gate expanders should lie as close as possible to the gate being expanded. This avoids capacitive loading and noise pick-up.

Input date to master slave JK flip flops should not be changed when the clock is high.

#### **NOISE IMMUNITY**

Noise immunity is a vital consideration when evaluating integrated circuits since noise can, under certain conditions, falsely trigger gates and introduce errors into the system.

First consider the effect of noise on the individual device.

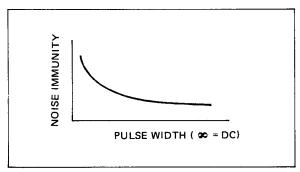

#### a-c or d-c noise

It is difficult to define a-c noise and even more difficult to relate it to a specification. Generally, d-c noise is worst case. When noise immunity is plotted against pulse width, it can be shown that the circuit is more immune to noise as pulse width decreases. See Figure 15.

Figure 15.

#### Susceptibility

When discussing a-c noise, the term "noise susceptibility" is more appropriate than "noise immunity".

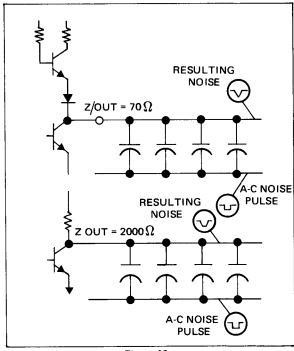

#### Low logical one a-c noise susceptibility

An important feature of the design is the output configuration which both supplies current (in the logical 1 state) and sinks current (in the logical 0 state) from a low impedance. Typically, logical 0 output impedance is  $12\Omega$  and logical 1 output impedance is  $70\Omega$  for standard Series 74N circuits. See Figure 16. This low output impedance in either state rejects capacitively coupled a-c pulses and ensures small R-C time constants which preserve waveshape integrity.

This means a-c noise susceptibility is far better than logic circuits which have 2000-ohm logical one output impedances.

As a result, System 74 TTL is much more effective than other forms of logic at preventing noise from

Figure 16.

ever appearing at the output. In addition, it has high immunity to d-c noise from supply voltage and ground sources.

#### Supply Voltage Noise

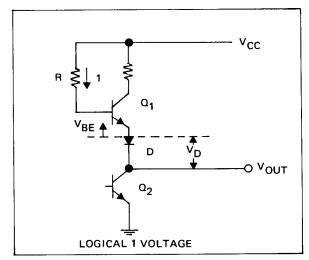

Notice that the output of a System 74 gate, Figure 17, is similar to an emitter-follower circuit. For loads even considerably higher than fan-outs of ten, the transistor  $Q_1$  does not saturate when the gate is in the logical one state. Therefore:

$$V_{OUT} = V_{CC} - IR - V_{BE(Q_1)} - V_D$$

Figure 17.

As the voltage changes across the resistor R, the base emitter junction of  $Q_1$ , and the diode are small, the output voltage follows the supply voltage very closely in the logical one stage. A negative voltage change on the supply line is reflected almost directly to the signal output line.

The high logical one d-c noise immunity reduces the probability of false triggering due to supply voltage variation.

#### Ground line noise

In the logical zero state,  $Q_2$  saturates and a positive transistion on the ground line is seen on the signal line.

Therefore, both supply voltage noise and ground line noise appear as signal line noise. Thus, the treatment of d-c noise can be discussed comprehensively by concentrating on the signal line only.

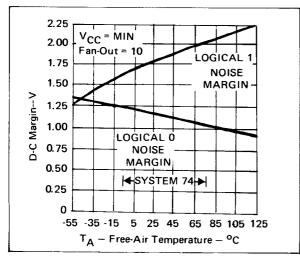

#### Typical d-c noise immunity

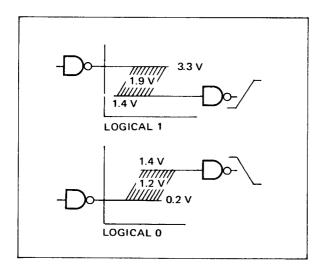

System 74 gates change state as the changing input voltage passes through an approximate 1.4 volt threshold. The output is typically 3.3 volts in the

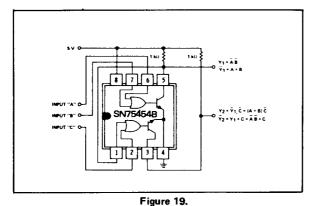

logical one state (see Figure 18) and 0.2 volt in the logical zero state. Therefore, the output can typically tolerate 1.9 volts of negative-going noise in the one state and 1.2 volts of positive-going noise in the zero state before causing the gate it is driving to falsely trigger. In both states, System 74 has more than one volt typical noise immunity. See Figure 19.

Figure 18.

Figure 19.

#### Guaranteed d-c noise immunity

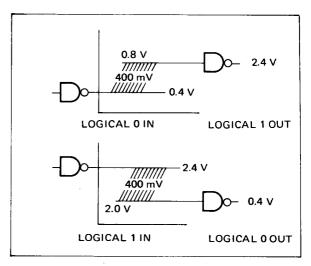

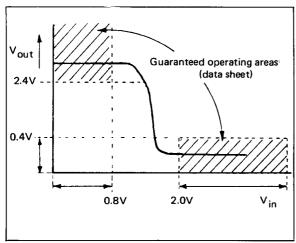

Simply stating that a circuit will not falsely trigger is not an adequate guarantee for a design engineer. The manufacturer must also guarantee an absolute output voltage limit which will not be exceeded when noise is applied to an input. Figure 20 shows these guaranteed voltages.

Figure 20.

The logical zero input test voltage is 0.8 volt, and TI guarantees a maximum logical zero output of 0.4 volt which gives a guaranteed noise immunity of 400 millivolts.

Likewise, the logical one input test condition is 2.0 volts which is 0.4 volt below the guaranteed minimum logical one output of 2.4 volts.

In both states, guaranteed noise immunity is 400 millivolts.

Having seen what noise immunity is inherent in the device design now consider the noise immunity of a system and how it can be simply improved.

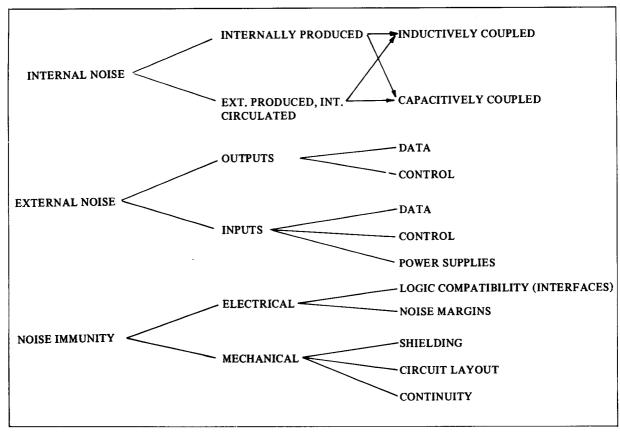

Noise considerations in digital systems may be summarised as shown in Figure 21.

Each topic shown cannot be considered in isolation, but must take into consideration the influence of other factors, for example, internal noise only becomes important if it is significant compared with data levels.

#### **Internal Noise Generation**

High frequency signal components due to fast transition times at the outputs of logic elements are the main source of internally generated noise. These components are still present when data rates are low, demanding that high frequency techniques should be used no matter what the pulse repetition rate.

As device logic levels change, circuit currents flowing also change. These changes are due to:-

- (i) Different currents required to maintain the new logic level.

- (ii) Transients due to lines charging and discharging.

- (iii) Conduction overlap of the transistors in a TTL output stage.

Figure 21.

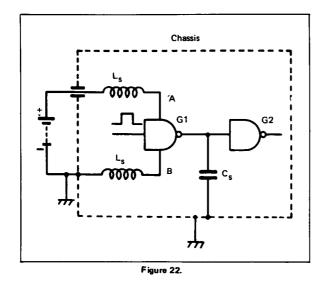

Figure 22 shows the stray circuit elements associated with these transients.

Capacitance  $C_s$  is the capacitance to ground the surroundings of the output connection from gate G1 to the input of gate G2.  $L_s$  and  $L_g$  are the self inductances of the ground and supply lines respectively.

When the gate output changes from a logical '0' to a logical '1' capacitance  $C_{\rm S}$  must be charged through inductance  $L_{\rm S}$  from the supply. The charging current

$I_s$  being  $C_s$ .  $V/t_r$ , where V is the voltage difference between the logical '1' and '0' levels and  $t_r$  is the voltage rise time at the gate output. For standard TTL with typical rise and fall times of 7 ns or less, interconnection charging currents can be greater than 8mA per output. This together with conduction overlap in the output stage indicates that care should be taken with system layout so as to minimise supply line impedance and interconnection inductance.

In a practical system the following steps should be taken to minimise the generation of internal noise.

(i) The power supply distribution system should be of low impedance.

This can be achieved by two methods:

- (a) A low impedance transmission line formed by a stripline above a ground plane or line.

- (b) Medium impedance line with decoupling to ground at regular intervals by discrete R.F. capacitors, e.g. disc ceramics. Decoupling should be carried out every 8 to 10 packages. Use 0.01 μF to 0.1 μF or 200pF per totem pole output, whichever is the greater value. These should be distributed throughout the circuit, not lumped together. Both ends of a long ground bus-bar should be returned to a common point.

- (ii) Gates that drive lines must be decoupled at the package. The decoupling capacitor and transmission line ground should be commoned as near to the driving device ground as is practical.

- (iii) Power gates formed by paralleling gates should utilise a single package with its decoupling capacitor.

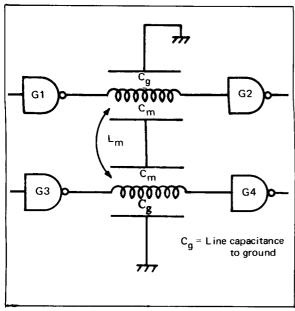

Noise that has gained entry to equipment as well as that which is internally generated can couple into adjacent signal and power lines. This can take place through common impedances or as shown in Figure 23.

Here two lines carrying signals, or signal and noise, are in close proximity to one another. Cross coupling exists between these two lines due to mutual capacitance and inductance  $C_m$  and  $L_m.$  In order to analyse this configuration, it is convenient to consider  $C_m$  and  $L_m$  forming a mutual impedance  $Z_m$  between the two lines. If the line impedances are  $Z_0$ , the gate output impedances are  $Z_1$ , the logic swing at the output of gate G1 is  $V_s$ , and the coupled component of  $V_s$  at the input of G4 is  $V_{\rm in}$ .

$$V_{in} = V_s / (1.5 + Z_m / Z_o) (1 + Z_1 / Z_0) \dots 1$$

Figure 23.

The following practical conclusions can be drawn from equation 1.

- 1. To minimise cross talk between two lines their mutual impedance should be as high as possible and the line impedance as low as possible.

- 2. Such lines should be coaxial cables with low impedances  $Z_0$  and very little external field giving a high  $Z_m$ .

In practice the line impedance cannot be too low or the logic swing at the receiving gate will be restricted and line reflections will be significant compared with logic levels.

Stripline conductors above a ground plane can have controlled impedances giving excellent crosstalk properties.

Single wires, whilst being inexpensive and convenient, have poor cross-talk and reflection characteristics limiting their usable length to 25cm or less with standard TTL.

For lines less than 5m in length twisted pairs with  $Z_0$  between  $50\Omega$  and  $150\Omega$  are satisfactory provided that the sending gate is restricted to line driving. (This is explained in more detail in the section on driving transmission lines.)

#### **External Noise**

In any digital system provision must be made for the transmission of input and output data and control signals between the logic system and its peripherals. The current and voltage levels chosen for transmission are generally incompatible with TTL as they are dictated by considerations such as line impedance, noise environment, contact resistance, etc.

The influence of external noise on a TTL logic system is determined mainly by the type of interface circuits used to transfer signals into the logic system. These circuits cannot be designed effectively unless the input requirements of a TTL gate are understood.

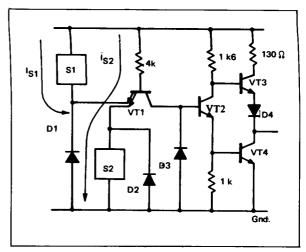

Figure 24.

Figure 24 shows the circuit diagram of a standard 74N series gate, where  $I_{S1}$  is the current to be 'sourced' and  $I_{S2}$  to be 'sunk' by the driver circuits S1 and S2.

Transistor VT1 is a multiemitter transistor with a  $4k\Omega$  base resistor to the supply voltage  $V_{CC}$ . If any input emitter is grounded base current flows out of the grounded emitter saturating transistor VT1 and turning 'off' transistor VT2 allowing its collector to

rise towards  $V_{CC}$ . The output of emitter follower transistor VT3 is, therefore, a logical '1'. If all input emitters of VT1 are high, i.e. logical '1' then its base collector diode is forwarded biassed and transistors VT2 and VT4 are saturated. The collector of VT4 is therefore at  $V_{CE(sat)}$ , i.e. logical '0'. Since the input transistor is now operating in an inverse mode with the collector to base diode forward biassed, an inverse emitter current, dependent upon inverse gain and base current, must flow into each emitter. The input voltage at which VT1 changes from normal to inverse mode of operation, i.e. the gate threshold voltage, is determined by its collector potential. This is defined by the  $V_{BE}$ 's of VT2 and VT4, giving a typical threshold of 1.4V.

A typical transfer characteristic of the circuit of Figure 24 is shown in Figure 25.

Figure 25.

To obtain maximum noise immunity logical '0' and '1' input levels should be far removed from the gate threshold. This means that any interface circuit must be able to sink base current of VT1 when in the logical '0' state and source the inverse emitter current when in the logical '1' state in order to maintain maximum noise immunity.

#### **Interface Circuits**

An interface circuit must perform the following operations:-

- Transform input logic levels to those of TTL. This must be achieved without loss of noise margin.

- (ii) Filter out unwanted noise whose frequency components lie outside the signal frequency range. Noise that occurs within the signal frequency spectrum, i.e. comparable with data bit rate, can only be removed by logical means.

(iii) The interface circuit must take into consideration the transfer characteristics of the circuit that it is driving. The basic TTL gate is a saturating amplifier with a range of input voltages around its threshold where the gate will act as a high gain (>55dB power gain at 10MHz) high frequency linear amplifier.

The rise and fall times of data edges into TTL required for oscillation-free switching, are dependent upon a number of factors. These include the driving source impedance, gate loading, layout and supply decoupling. In practice, interface circuits should have rise and fall times (10-90%) < 50 ns between logical '0' and '1' levels.

#### Input Interfacing

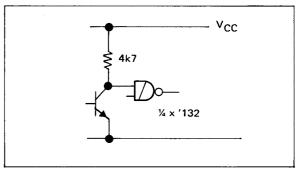

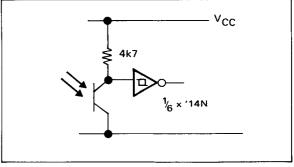

Figure 26a shows one of the simplest ways of connecting into TTL.

Figure 26a.

Figure 26b.

The transistor, when switched on and saturated, sinks the input current of the gate and when the transistor is off the gate input current which is then very small is provided by the resistor. Ideally, the gate should be a Schmitt trigger such as the '132N, to avoid oscillation and noise problems when the input voltage is around 1.5V. (A phototransistor can also be interfaced by this scheme as in Figure 26b).

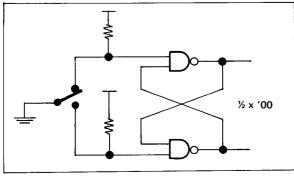

Another well tried method where the inputs are driven by a low impedance such as a switch, uses a pair of gates across coupled as a latch, as shown in Figure 27. This arrangement can reduce the problems of switch bounce without needing a time constant.

Figure 27.

A transistor, as in Figure 28, allows interfacing with high impedances, although with this simple arrangement the threshold will be at only 0.7 of a volt. There is therefore less than 0.7V noise immunity.

In most systems it is advantageous to have higher thresholds in order to overcome voltage drops down

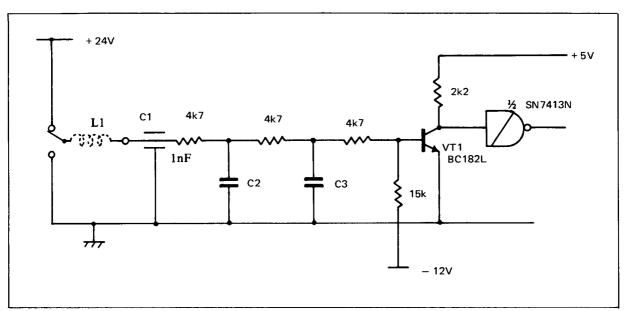

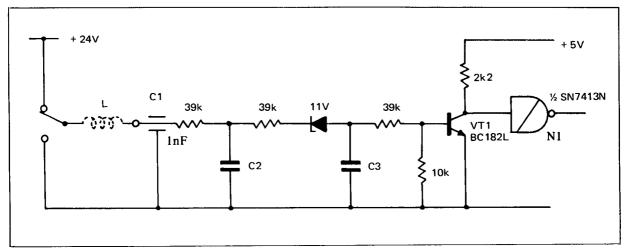

lines and contact resistance etc. Such circuits which have thresholds of about 12V are shown in Figures 28 and 29.

Both circuits consist of CR low pass filters followed by a transistor buffer and a Schmitt trigger. Capacitor C1 is a lead through ceramic. This, together with L (lead inductance), forms a low pass filter removing high frequency components that would otherwise, due to layout, be very difficult to remove. The logic threshold for the circuit of Figure 28 is arranged to be 12V midway between the input logic levels, 0 and 24V. The values of C1, C2 and C3 should be chosen to give the required frequency response.

Both circuits have a series resistor between capacitor C3 and transistor VT1. This limits the rate of discharge of C3 through the base emitter diode of transistor VT1.

Figure 28.

Figure 29.

#### **Optical Interfaces**

In many industrial systems it is possible for very large transient common mode voltages to exist between equipments. In cases such as these an isolated coupler such as reed relays, transformers or optical devices must be used in order to transmit date. An alternative is to attenuate the signal and common mode offset until the common mode voltage is sufficiently low to be acceptable. The signal is then detected by a high gain differential comparator. This system does, however, have poor noise rejection unless common mode paths are carefully balanced.

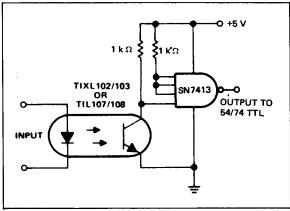

An economical method giving a high degree of isolation (>1kV) and reasonable speed is the optical coupler, as shown in Figure 30.

Figure 30.

The optical isolator consists of an infrared emitter and receiver diode electrically isolated from each other, but maintained in the same package. The emitter diode forward current is in the order of 15mA to obtain a receiver current of 2mA (TIL 111). A suitable buffer between the diode output and TTL input must be provided which in the simplest form would be a TTL Schmitt trigger. A maximum bit rate of approximately 60kHz can be obtained with the circuit of Figure 29. If higher bit rates are required then the TIL 111/2 should be followed by a wideband operational amplifier such as the SN7511 operated in the virtual earth mode.

#### Interface Filters

The previous few circuits have concentrated on the voltage requirements of an interface, although Figures 28 and 29 will be low pass filters.

The filter shown in Figure 30 is all that is needed in the majority of cases, to eliminate noise associated with input signals. To maintain noise immunity at the Schmitt input the maximum value of resistor R should be limited to  $250\Omega$  when being driven from standard 74N Series TTL.

This, therefore, determines the value of capacitor C for a given 3dB cut-off frequency,  $f_0$ , of the filter, i.e. C = 1/2 II R. $f_0$ . The rate of attentuation past the cut-off frequency is 6dB/octave. For larger rates of attentuation and faster response times multipole Chebyshev filters can be used. Since the input to the Schmitt is always positive with respect to ground, capacitor C may be a large value electrolytic.

#### Low pass filter, Chebyshev

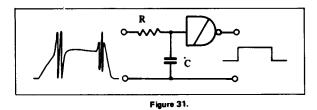

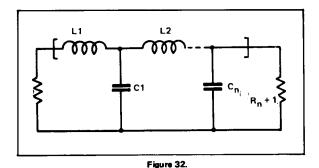

These filters should be used when digital equipment is required to operate under conditions of extreme electrical noise. The Chebyshev filter is characterised by an amplitude frequency response that ripples in the pass band and falls off rapidly past the cut-off frequency  $f_O$ . The general form of this type of filter is shown in Figure 31.

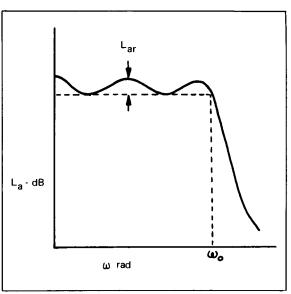

The amplitude frequency response of such a filter is shown in Figure 32.

Figure 33.

This circuit form is well suited to mechanical construction since the capacitive elements can be lead throughs. The required D.C. operating conditions for the Schmitt trigger are easily satisfied since the filter has almost zero impedance at D.C.

A compromise has to be made between the number of elements and the rate of attentuation past the cut-off frequency. In practice, a four element filter that has an attenuation of 60dB at  $4\omega_{\rm O}$  is usually satisfactory. The load impedance  $R_{\rm n}+1$  is determined by the input impedance of the Schmitt trigger, which in turn determines the filter source impedance  $R_{\rm O}$ . For this reason it is more practical to use a different filter design which will match a low source impedance to the input impedance of the Schmitt trigger (4k approx.).

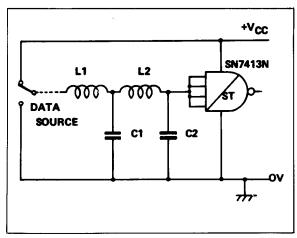

Such a design is shown in Figure 34 and component values are tabulated in Table B for various cut-off frequencies.

Figure 34.

Element values for 4 element filter with  $L_{ar}$  = 1dB and  $L_a$  = -60dB at  $4\omega_0$ .

Table B

| f <sub>o</sub> (kHz) | L1(mH) | C1(pF) | L2(mH) | C2(pF) |

|----------------------|--------|--------|--------|--------|

| 100                  | 9.0    | 420    | 8.2    | 760    |

| 200                  | 4.5    | 220    | 4.1    | 380    |

| 500                  | 1.8    | 84     | 1.6    | 150    |

| 1000                 | 0.9    | 42     | 0.8    | 76     |

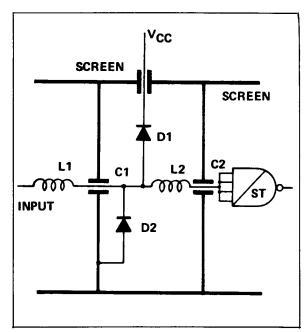

Since the inductive and capacitive components are  $\infty$  1/f<sub>O</sub>, element values for any cut off frequency f<sub>O</sub> may be calculated from the tables given. Additional components may be added to the circuit of Figure 9 to enable it to handle very large voltage surges at the filter input as shown in Figure 35.

Figure 35.

Diodes D1 and D2 limit the input swing into the Schmitt trigger, they should be situated after inductor L1 so that the rate of rise of voltage across diodes D1 and D2 is limited.

#### Interfacing to Other Devices

The equipment may require an interface between High Noise Immunity Logic and TTL or between MOS and TTL. Specially for the former there is a HNIL to TTL device (and also one for the opposite direction, TTL to HNIL). MOS to TTL et vice versa is usually simple. Interfacing with the high threshold versions is described fully in report CA170. The low threshold (TTL compatible) types can be interfaced directly, or with perhaps a few resistors.

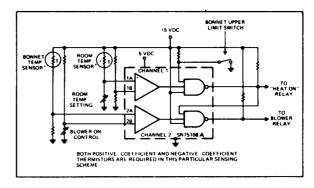

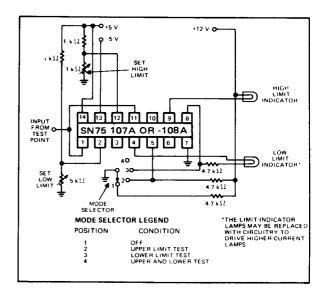

Memories are another area requiring interfacing. The series 75 sense amplifiers can be used to detect the low output from a core memory or certain MOS memories. They sense the pulse of 20mV or so between two sense lines of the memory plane regardless of its polarity and convert it into a TTL signal. Balanced-line receivers such as the 75107 can be used, as well as for their original purpose, as level detectors or comparators. They have the advantages of high speed, up to about 20MHz, and a full fan-out TTL output. In fact, they make good interfaces between high frequency, low amplitude signals and TTL, such as is required at the input to a frequency counter.

#### **Output Interfacing**

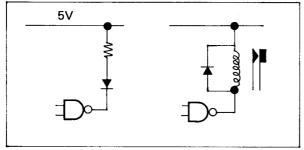

A standard TTL output stage can sink 16mA. This is sufficient to operate LEDs and small relays as shown in Figure 36.

Figure 36.

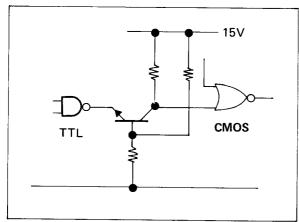

The LED can be visible or infra-red. It can even be the first half of an Optically Coupled Isolator. Interfacing with CMOS can be achieved as shown in Figure 37.

Figure 37.

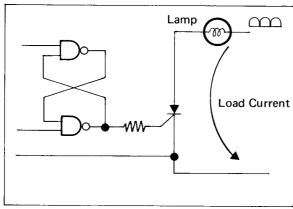

A gate can drive a SCR for switching on a lamp as in Figure 38.

Figure 38.

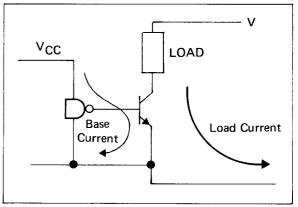

The SCR solution for driving lamps is useful as it is not affected by the cold current of the lamp which may be 10 or 20 times the nominal operating current of the lamp. Another way of driving a large load without using an SCR is via a transistor. The current into the base which is available from the gate when its output goes high, is at least 70 percent of the minimum specified short circuit current.

Figure 39.

For more specific outputs there are memory drivers, peripheral drivers and balanced line drivers. There is even a Nixie tube driver. Outputs are an unexpected source of faults.

The output must not inject noise back into the logic, either on the 5V rail or as earth noise. For instance, when laying out the circuits in Figure 38 and 39 it is important to make sure that the load current does not flow along the logic ground line.

#### Line Driving

When an interconnection is above a certain length depending upon the edge speeds being propagated, it is necessary to consider the interconnection as a transmission line. As the different families within System 74 have different speeds this length will vary from family to family.

Table C

| Series   | Speed (ns) | length<br>(approx) (cm) | line impedance ( $\Omega$ ) |  |

|----------|------------|-------------------------|-----------------------------|--|

| 74       | 10         | 50                      | 100                         |  |

| 74H      | 6          | 50                      | 75-100                      |  |

| 74L      | 33         | 200                     | 150                         |  |

| 74LS     | 10         | 50                      | 150                         |  |

| 74S      | 3          | 25                      | 75                          |  |

| 75 (=74) | 10         | 50                      | 100                         |  |

These lengths are listed in Table C along with a suggested line impedance for using with each series of outputs. Due to the input and output characteristics of TTL very acceptable waveforms can be obtained using System 74.

The following rules have been established for the elimination of transmission-line troubles in TTL systems.

- Use direct wire interconnections that have no specific ground return for lengths up to about half those in Table C. A ground plane is always desirable.

- 2. Direct wire interconnections must be routed close to a ground plane if they are longer and should never exceed Table C.

- 3. When using coaxial or twisted-pair cables, design around approximately  $100\Omega$  characteristic impedance for series 74N. Coaxial cable of  $\cong 100\Omega$  impedance is recommended. For twisted pair No. 26 or No. 28 S.W.G. wire with thin insulation twisted about 30 turns per foot works well. Higher impedances increase cross talk, and lower impedances are difficult to drive. Use the impedances listed in Table C for other series.

- 4. Ensure that transmission-line ground returns are carried through at both transmitting and receiving ends.

- 5. Connect reverse termination at driver output to prevent negative overshoot.

- 6. Decouple line-driving and line-receiving gates as close to the package  $V_{CC}$  and ground pins as practical, with a 0.1  $\mu F$  capacitor.

- 7. Gates used as line drivers should be used for that purpose only. Gate inputs connected directly to a line-driving output could receive erroneous inputs due to line reflections, long delay times introduced, or excessive loading on the driving gate.

- 8. Gates used as line receivers should have all inputs tied together to the line. Other logic inputs to the receiving gate should be avoided, and a single gate should be used as the termination of a line.

- Any device that derives internal feedback from its outputs should not be used for line driving. Such devices are bistables, shift registers and monostables.

- Gates that drive back wiring via an edge connector should be mounted near the connector ground in order to provide a low impedance return for line currents.

One of the useful things about System 74 TTL is that it does not need clamp diodes. Clamp diodes are low forward impedance diodes placed under TTL inputs with the object of minimizing "line ringing" or "line reflection" when mismatching occurs between driving and driven gates and the line along which the signal is propagating.

Figure 40.

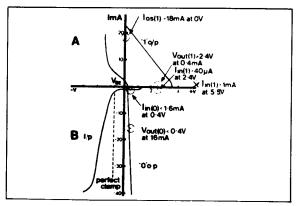

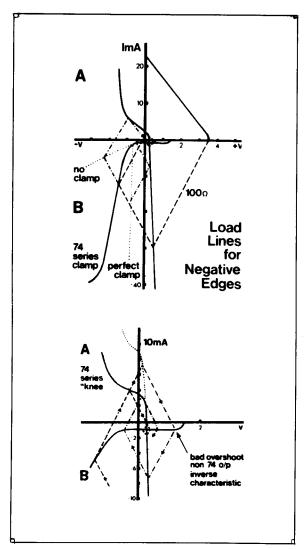

To perform line ringing calculations one can use a graphical approach. In Figure 40 are the input and output characteristics of a 74N Series gate. The data sheet guaranteed parameters are indicated by the crosses.

Quadrants A and B respectively are the inverse output and inverse input characteristics — areas of operation which are not normally guaranteed, but of vital importance to the study of line ringing phenomena. The B characteristic is usually known as "input clamping". Added is the plot for a perfect clamp at  $V_{\mbox{\footnotesize{BE}}}$  below zero volts.

Figure 41.

Load lines are also superimposed on the second diagram with slope equal to line impedance so that line ringing can be calculated for a negative edge of the waveform. These are for a 100 ohm line showing normal 74 Series clamping compared with perfect clamping and no clamping at all. There is virtually no difference in the resulting overshoot for the three cases, and the reason for this is the nature of the characteristic in the A quadrant.

The exact portion of the characteristic which is a design feature of System 74 TTL, is the 'knee' and the point at which it crosses the current axis. If this is pushed up the current axis, bad overshoot results. So we make sure that our process control maintains this

knee at about 4mA. In this way we eliminate the need to add extra components to our circuits to modify characteristics in the A quadrant by, for instance, adding clamp diodes.

### Quality and Reliability

#### **QUALITY AND RELIABILITY**

This subject can be divided into separate areas of discussion. The reliability of components is a function of good design and processing by the manufacturer. The quality of components supplied to the user is a function of measurement and selection. The Quality Assurance personnel are responsible for supplying a defined quality of product and also to perform a continuous monitor of production processing in order to feed back information to manufacturing personnel who can then control processing to maintain quality.

Clearly, this feedback and maintenance of quality during production is important both to the user and producer. No producer can afford to produce such a quality that a significant part is rejected by Q.A. Neither can a Q.A. department tolerate continued rejection of poor quality from production. This situation would mean less product of acceptable quality available to the user at relatively higher cost.

Thus, the Quality Assurance and Reliability department has two distinct functions.

- 1. To test to a defined quality level by statistical means all product from manufacturing and then either return the product to manufacturing for rescreening or pass them to finished goods inventory.

- 2. To take random samples of product, straight from production and fully subject these to rigorous 100% electrical, mechanical and environmental testing. The results of this are made available on a quarterly basis in the form of a report. The primary object of this, in addition to providing test results, is to generate a failure rate analysis from which Mean Time Between Failures (MTBF) can be calculated.

These aspects of quality and reliability are discussed below. The third aspect is the feedback obtained from customers. Using this information an in-use failure rate can be estimated from results for major projects in the industry. This is expected to indicate that product quality is better than defined by the Q.A. Department in line with the philosophy of manufacturing product of a higher quality than defined by published quality levels.

#### **QUALITY**

In common with most industries supplying components in high volume a statistical method is used to estimate the quality level of product supplied to the customers. It can be shown that to guarantee quality by individual testing would require 300% testing. That is, each component would have to be tested 3 times by different operators using different test equipments. Even at this level of testing some non-perfect components would evade this surveillance. A statistical sampling method is currently used

whereby a sample of each production lot submitted to Q.A. is 100% tested and acceptance or rejection of the total lot depends upon the performance of the sample. All lots are 100% tested during the production phase, but this testing is not that used to guarantee the final quality. It is part of the procedure where every production process is monitored and immediate feedback supplied at each process step.

Texas Instruments currently uses an AQL sampling plan. The AQL (Acceptable Quality Level) plan specifies the maximum deviation from perfect quality that is acceptable to the industry. The AQL is considered as that quality of a lot which has a probability of acceptance of 0.95. An inspection level is specified with the AQL which determines the number of samples to be tested. Although the number of samples increases with lot size, the ratio of sample size to lot size decreases.

The defence specification DEF-131-A contains the details of sample size, lot size, and failures permitted for a given AQL and inspection level.

System 74 quality is governed by the following AQL and inspection levels:-

|                 | A.Q.L. | INSPECTION LEVEL |

|-----------------|--------|------------------|

| FUNCTIONAL      | 0.15%  | 11               |

| D.C. PARAMETERS | 1.0%   | H                |

| A.C. PARAMETERS | 2.5%   | 1                |