|              | General Information                              |

|--------------|--------------------------------------------------|

|              | Interchangeability Guide                         |

|              | Glossary/Timing Conventions/Data Sheet Structure |

|              | Dynamic RAMs                                     |

|              | Dynamic RAM Modules                              |

| - 16<br>- 17 | EPROMs/PROMs                                     |

| _            | ROMs                                             |

|              |                                                  |

| 2            | Military Products                                |

|              | Military Products Applications Information       |

|              |                                                  |

|              | Applications Information                         |

## ATTENTION

These devices contain circuits to protect the inputs and outputs against damage due to high static voltages or electrostatic fields; however, it is advised that precautions be taken to avoid application of any voltage higher than maximumrated voltages to these high-impedance circuits.

Unused inputs must always be connected to an appropriate logic voltage level, preferably either supply voltage or ground.

Additional information concerning the handling of ESD sensitive devices is provided in Section 12 in a document entitled *''Guidelines for Handling Electrostatic-Discharge-Sensitive (ESDS) Devices and Assemblies.''*

OCTOBER 1977-REVISED NOVEMBER 1985

- 16,384 X 1 Organization

- 10% Tolerance on All Supplies

- All Inputs Including Clocks TTL Compatible

- Unlatched Three-State Fully TTL-Compatible Output

- Performance Ranges:

|            | ACCESS  | ACCESS  | READ   | READ-   |  |

|------------|---------|---------|--------|---------|--|

|            | TIME    | TIME    | OR     | MODIFY- |  |

|            | ROW     | COLUMN  | WRITE  | WRITE   |  |

|            | ADDRESS | ADDRESS | CYCLE  | CYCLE   |  |

|            | (MAX)   | (MAX)   | (MIN)  | (MIN)   |  |

| TMS4116-15 | 150 ns  | 100 ns  | 375 ns | 375 ns  |  |

| TMS4116-20 | 200 ns  | 135 ns  | 375 ns | 375 ns  |  |

| TMS4116-25 | 250 ns  | 165 ns  | 410 ns | 515 ns  |  |

|            |         |         |        |         |  |

- Page-Mode Operation for Faster Access Time

- Common I/O Capability with Early Write Feature

- Low-Power Dissipation

- Operating . . . 462 mW (Max)

- Standby . . . 20 mW (Max)

- 1-T Cell Design, N-Channel Silicon-Gate Technology

- 16-Pin 300-Mil (7,62-mm) Package Configuration

#### description

The TMS4116 series is composed of monolithic high-speed dynamic 16,384-bit MOS random-access memories organized as 16,384 one-bit words, and employs single-transistor storage cells and N-channel silicon-gate technology.

All inputs and outputs are compatible with Series 74 TTL circuits including clocks: Row-Address Strobe  $\overline{RAS}$  (or  $\overline{R}$ ) and Column-Address Strobe  $\overline{CAS}$  (or  $\overline{C}$ ). All address lines (A0 through A6) and data in (D) are latched on chip to simplify system design. Data out (Q) is unlatched to allow greater system flexibility.

Typical power dissipation is less than 350 milliwatts active and 6 milliwatts during standby (V<sub>CC</sub> is not required during standby operation). To retain data, only 10 milliwatts average power is required which includes the power consumed to refresh the contents of the memory.

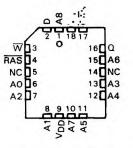

The TMS4116 series is offered in a 16-pin dual-in-line plastic (N suffix) package and is guaranteed for operation from 0°C to 70°C. The package is designed for insertion in mounting-hole rows on 7,62-mm (300-mil) centers.

#### operation

#### address (AO-A6)

Fourteen address bits are required to decode 1 of 16,384 storage cell locations. Seven row-address bits are set up on pins A0 through A6 and latched onto the chip by the row-address strobe (RAS). Then the

<sup>†</sup>The term "read-write cycle" is sometimes used as an alternative to "read-modify-write cycle."

|     | N P        | ACKA  | GE         |

|-----|------------|-------|------------|

|     | (то        | P VIE | V)         |

| VBB | d1         | U16   | D vss      |

| D   |            | 15    | CAS        |

| Ŵ   | □3         | 14    | Da         |

| RAS | 04         | 13    | D A6       |

| AO  |            | 12    | A3         |

| A2  | 6]         | 11    | <b>A</b> 4 |

| A1  |            | 10    | <b>A5</b>  |

| VDD | <u>Ц</u> 8 | 9     | D vcc      |

|     |            |       |            |

| PIN   | NOMENCLATURE          |

|-------|-----------------------|

| A0-A6 | Addresses             |

| CAS   | Column-Address Strobe |

| D     | Data Input            |

| Q     | Data Output           |

| RAS   | Row-Address Strobe    |

| VBB   | - 5-V Power Supply    |

| Vcc   | 5-V Power Supply      |

| VDD   | 12-V Power Supply     |

| VSS   | Ground                |

| W     | Write Enable          |

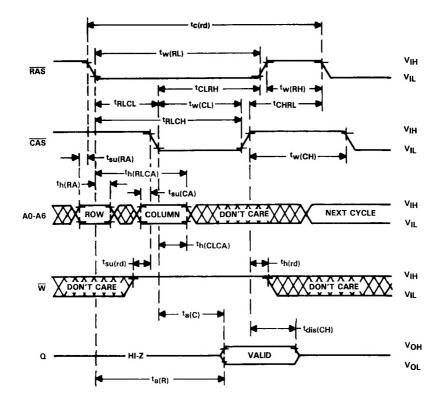

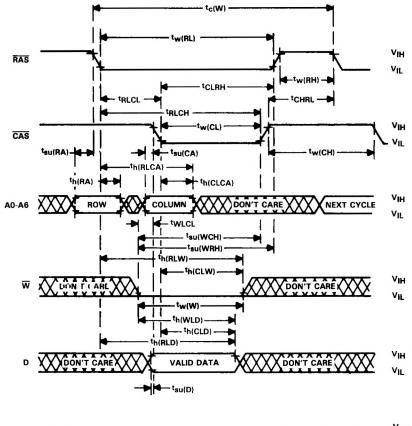

seven column-address bits are set up on pins A0 through A6 and latched onto the chip by the columnaddress strobe (CAS). All addresses must be stable on or before the falling edges of  $\overline{RAS}$  and  $\overline{CAS}$ .  $\overline{RAS}$  is similar to a chip enable in that it activates the sense amplifiers as well as the row decoder.  $\overline{CAS}$  is used as a chip select activating the column decoder and the input and output buffers.

#### write enable (W)

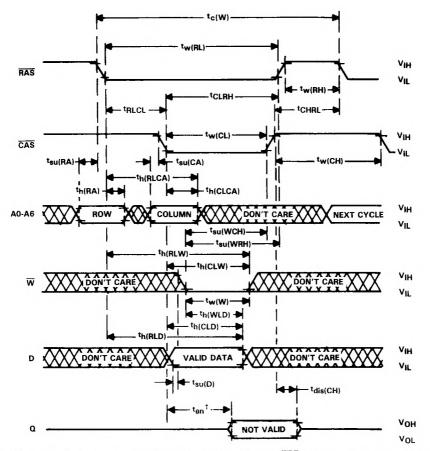

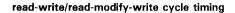

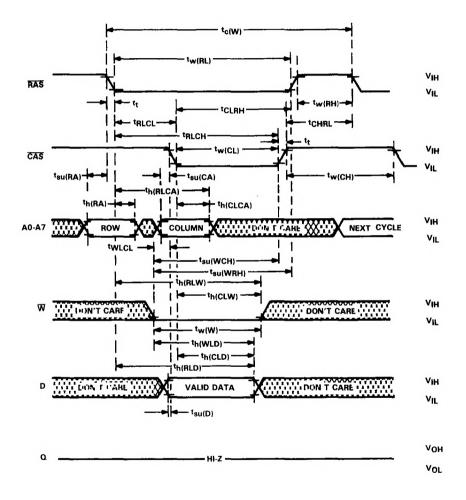

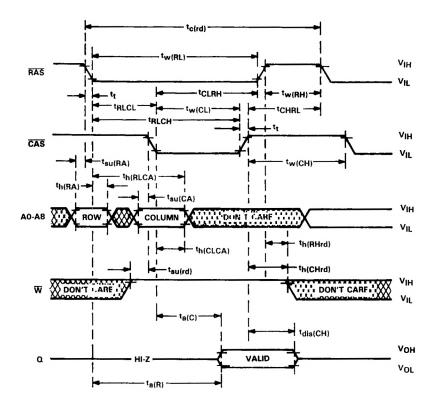

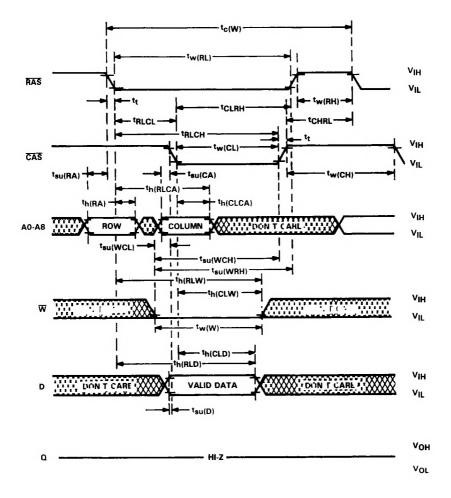

The read or write mode is selected through the write-enable  $(\overline{W})$  input. A logic high on the  $\overline{W}$  input selects the read mode and a logic low selects the write mode. The write-enable terminal can be driven from standard TTL circuits without a pull-up resistor. The data input is disabled when the read mode is selected. When  $\overline{W}$  goes low prior to  $\overline{CAS}$ , data out will remain in the high-impedance state for the entire cycle permitting common I/O operation.

#### data in (D)

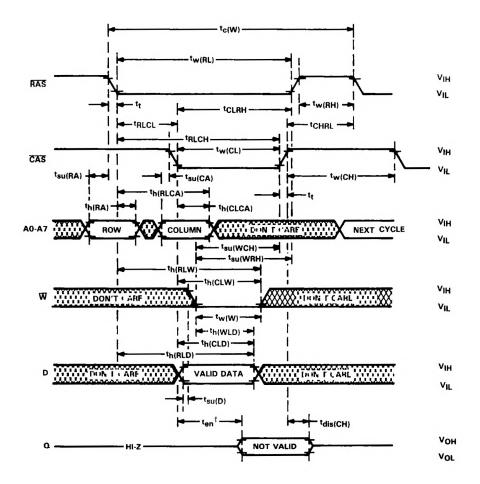

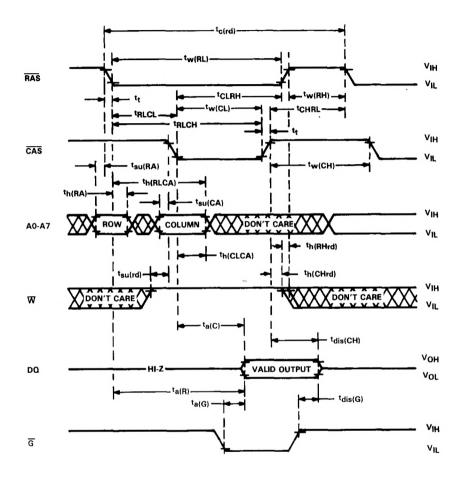

Data is written during a write or read-modify-write cycle. Depending on the mode of operation, the falling edge of  $\overrightarrow{CAS}$  or  $\overrightarrow{W}$  strobes data into the on-chip data latch. This latch can be driven from standard TTL circuits without a pull-up resistor. In an early write cycle,  $\overrightarrow{W}$  is brought low prior to  $\overrightarrow{CAS}$  and the data is strobed in by  $\overrightarrow{CAS}$  with setup and hold times referenced to this signal. In a delayed-write or read-modify-write cycle,  $\overrightarrow{CAS}$  will already be low, thus the data will be strobed in by  $\overrightarrow{W}$  with setup and hold times referenced to this signal.

#### data out (Q)

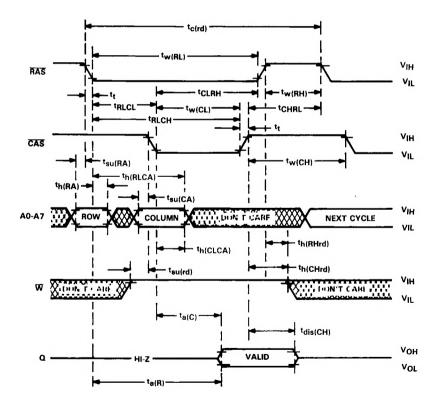

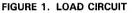

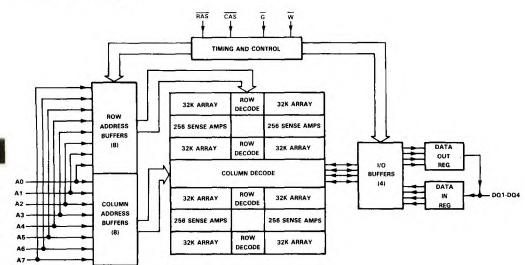

The three-state output buffer provides direct TTL compatibility (no pull-up resistor required) with a fan out of two Series 74 TTL loads. Data out is the same polarity as data in. The output is in the high-impedance (floating) state until  $\overline{CAS}$  is brought low. In a read cycle, the output goes active after the enable time interval  $t_a(C)$  that begins with the negative transition of  $\overline{CAS}$  as long as  $\underline{t_a(R)}$  is satisfied. The output becomes valid after the access time has elapsed and remains valid while  $\overline{CAS}$  is low;  $\overline{CAS}$  going high returns it to a high-impedance state. In an early write cycle, the output is always in the high-impedance state. In a delayed-write or read-modify-write cycle, the output will follow the sequence for the read cycle.

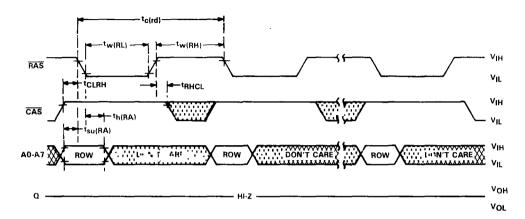

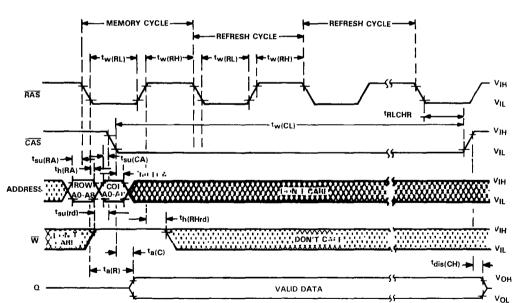

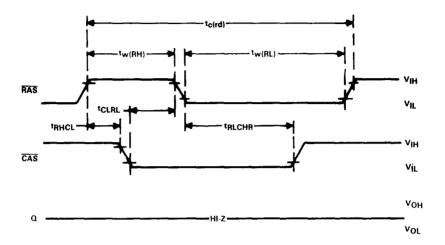

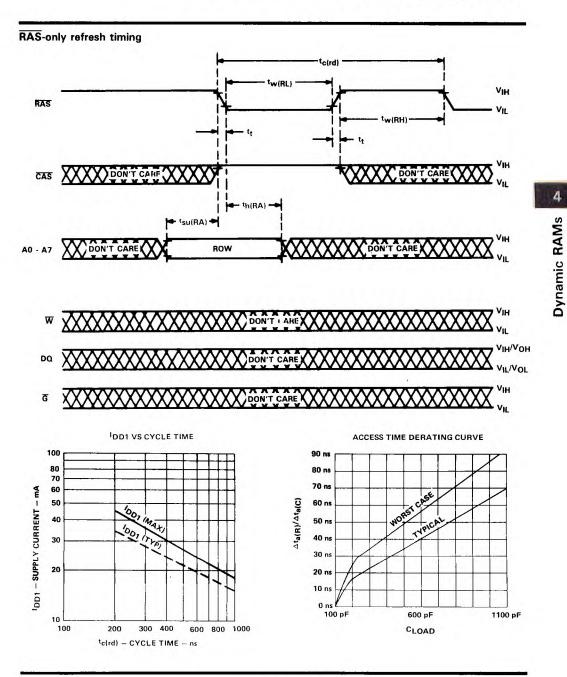

#### refresh

A refresh operation must be performed at least every two milliseconds to retain data. Since the output buffer is in the high-impedance state unless CAS is applied, the RAS-only refresh sequence avoids any output during refresh. Strobing each of the 128 row addresses (A0 through A6) with RAS causes all bits in each row to be refreshed. CAS remains high (inactive) for this refresh sequence, thus conserving power.

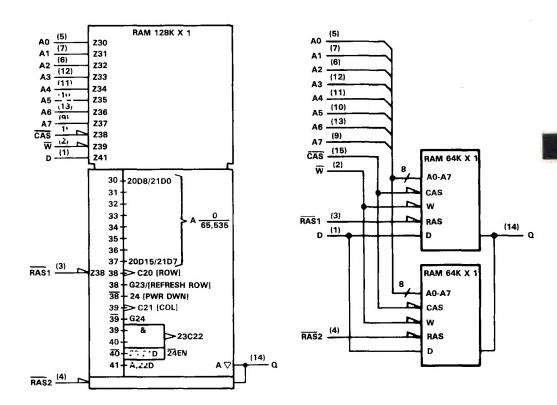

#### page mode

Page-mode operation allows effectively faster memory access by keeping the same row address and strobing successive column addresses onto the chip. Thus, the time required to setup and strobe sequential row addresses on the same page is eliminated. To extend beyond the 128 column locations on a single RAM, the row address and RAS is applied to multiple 16K RAMs; CAS is decoded to select the proper RAM.

#### power up

VBB must be applied to the device either before or at the same time as the other supplies and removed last. Failure to observe this precaution will cause dissipation in excess of the absolute maximum ratings due to internal forward bias conditions. This also applies to system use, where failure of the VBB supply must immediately shut down the other supplies. After power up, eight  $\overline{RAS}$  cycles must be performed to achieve proper device operation.

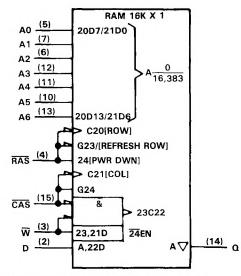

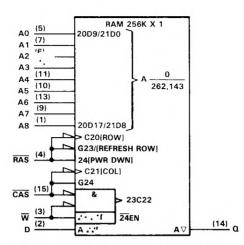

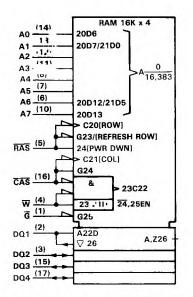

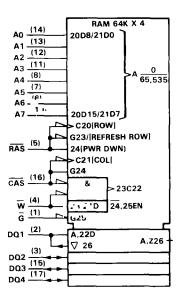

## logic symbol<sup>†</sup>

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

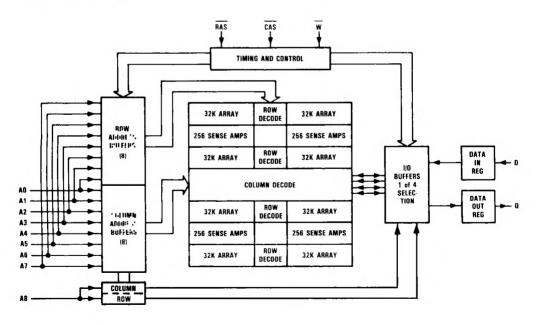

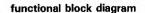

#### functional block diagram

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Voltage on any pin (see Note 1)                  | -0.5 V to 20 V   |

|--------------------------------------------------|------------------|

| Voltage on VCC, VDD supplies with respect to VSS | . $-1$ V to 15 V |

| Short circuit output current                     | 50 mA            |

| Power dissipation                                | 1 W              |

| Operating free-air temperature range             | . 0°C to 70°C    |

| Storage temperature range                        | -65°C to 150°C   |

<sup>†</sup> Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: Under absolute maximum ratings, voltage values are with respect to the most-negative supply voltage, VBB (substrate), unless otherwise noted. Throughout the remainder of this data sheet, voltage values are with respect to VSS.

#### recommended operating conditions

|       |                                      |                             | MIN  | NOM | MAX  | UNIT |

|-------|--------------------------------------|-----------------------------|------|-----|------|------|

| VBB   | Supply voltage                       |                             | -4.5 | -5  | -5.5 | V    |

| Vcc   | Supply voltage                       |                             | 4.5  | 5   | 5.5  | V    |

| VDD   | Supply voltage                       |                             | 10.8 | 12  | 13.2 | v    |

| Vss   | Supply voltage                       |                             |      | 0   |      | V    |

| VIH   | High-level input voltage             | All inputs except RAS, CAS, | 2.4  |     | 7    | v    |

| • 111 | riigh lovel inper voltage            | RAS, CAS, W:                | 2.7  |     | 7    |      |

| VIL   | Low-level input voltage (see Note 2) |                             | -1   | 0   | 0.8  | V    |

| TA    | Operating free-air temperature       |                             | 0    |     | 70   | °C   |

NOTE 2: The algebraic convention, whera the more negative (less positive) limit is designated as maximum, is used in this data sheet for logic voltage only.

|                   | PARAMETER                  | TEST CONDITIONS                                                    | MIN | TYPT | MAX        | UNIT |

|-------------------|----------------------------|--------------------------------------------------------------------|-----|------|------------|------|

| VOH               | High-level output voltage  | 1 <sub>0H</sub> = -5 mA                                            | 2.4 |      |            | V    |

| VOL               | Low-level output voltage   | $l_{OL} = 4.2 \text{ mA}$                                          |     |      | 0.4        | V    |

| ų                 | Input current (leakage)    | $V_I = 0 V$ to 7 V,<br>All other pins = 0 V except $V_{BB} = -5 V$ |     |      | 10         | μΑ   |

| 10                | Output current (leakage)   | $V_0 = 0$ to 5.5 V,<br>CAS high                                    |     |      | ± 10       | μA   |

| IBB1              |                            |                                                                    |     | 50   | 200        | μA   |

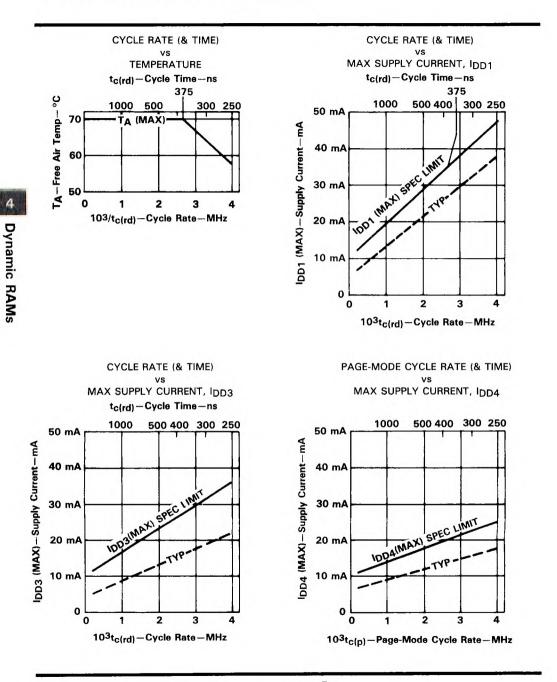

| ICC1‡             | Average operating current  | Minimum cycle time                                                 |     | 125  | <b>4</b> § | mA   |

| IDD1              | during read or write cycle |                                                                    |     | 27   | 35         | mA   |

| IBB2              | A COMPANY AND A COMPANY    |                                                                    |     | 10   | 100        | μA   |

| ICC2              | Standby current            | After 1 memory cycle                                               |     |      | ±10        | μA   |

| IDD2              |                            | RAS and CAS high                                                   |     | 0.5  | 1.5        | mA   |

| IBB3              |                            | Minimum cycle time                                                 |     | 50   | 200        | μA   |

| ICC3              | Average refresh current    | RAS cycling,                                                       |     |      | ±10        | μA   |

| IDD3              |                            | CAS high                                                           | _   | 20   | 27         | mA   |

| IBB4              |                            | Minimum cycle time                                                 | 1   | 50   | 200        | μA   |

| ICC4 <sup>‡</sup> | Average page-mode current  | urrent RAS low,                                                    |     |      | 4§         | mA   |

| IDD4              |                            | CAS cycling                                                        |     | 20   | 27         | mA   |

#### electrical characteristics over full ranges of recommended operating conditions (unless otherwise noted)

<sup>†</sup> All typical values are at  $T_A = 25^{\circ}C$  and nominal supply voltages.

<sup>‡</sup> V<sub>CC</sub> is applied only to the output buffer, so I<sub>CC</sub> depends on output loading.

§ Output loading two standard TTL loads.

#### capacitance over recommended supply voltage range and operating free-air temperature range, f = 1 MHz

|        | PARAMETER                             | TYP <sup>†</sup> MAX | UNIT |

|--------|---------------------------------------|----------------------|------|

| Ci(A)  | Input capacitance, address inputs     | 4 5                  | pF   |

| Ci(D)  | Input capacitance, data input         | 4 5                  | pF   |

| Ci(RC) | Input capacitance, strobe inputs      | 8 10                 | pF   |

| Ci(W)  | Input capacitance, write enable input | 8 10                 | pF   |

| Co     | Output capacitance                    | 5 7                  | pF   |

#### switching characteristics over recommended supply voltage range and operating free-air temperature range

|                      | DADAMETER                          | TEAT CONDITIONS                                                                          | ALT.             | 14.4 | 116-15 | 15454 | 116-20 | r₩5-116-25 |     | UNIT |

|----------------------|------------------------------------|------------------------------------------------------------------------------------------|------------------|------|--------|-------|--------|------------|-----|------|

|                      | PARAMETER                          | TEST CONDITIONS                                                                          | SYMBOL           | MIN  | MAX    | MIN   | MAX    | MIN        | MAX | UNIT |

| <sup>t</sup> a(C)    | Access time from CAS               | CL = 100 pF,<br>Load ≃ 2 Series<br>74 TTL gates                                          | <sup>t</sup> CAC |      | 100    |       | 135    |            | 165 | ns   |

| <sup>t</sup> a(R)    | Access time from RAS               | t <sub>RLCL</sub> = MAX,<br>C <sub>L</sub> = 100 pF,<br>Load ≈ 2 Series,<br>74 TTL gates | <sup>t</sup> RAC |      | 150    |       | 200    |            | 250 | ns   |

| <sup>t</sup> dis(CH) | Output disable time after CAS high | C <sub>L</sub> = 100 pF,<br>Load = 2 Series<br>74 TTL gates                              | toff             | 0    | 40     | 0     | 50     | 0          | 60  | ns   |

<sup>†</sup> All typical values are at  $T_A = 25^{\circ}C$  and nominal supply voltages.

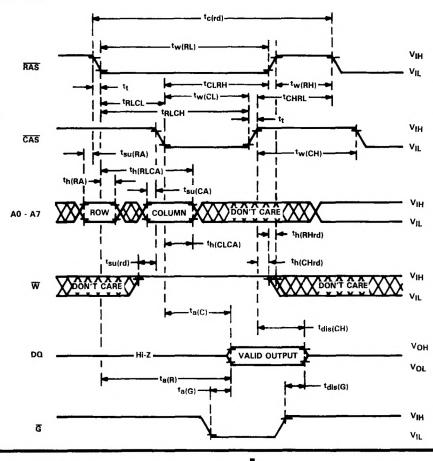

## timing requirements over recommended supply voltage range and operating free-air temperature range

|                       |                                                                                              | ALT.             | TMS | 4116-15 | TMS4116-20 |          | TMS4116-25 |        | UNIT |

|-----------------------|----------------------------------------------------------------------------------------------|------------------|-----|---------|------------|----------|------------|--------|------|

|                       | an unan in commenter for                                                                     | SYMBOL           | MIN | MAX     | MIN        | MAX      | MIN        | MAX    | UNIT |

| tc(P)                 | Page-mode cycle time                                                                         | tPC              | 170 |         | T .        |          | T          |        | ns   |

| tc(rd)                | Read cycle time                                                                              | tRC              | 375 |         | 375        |          | 410        |        | ns   |

| t <sub>c(W)</sub>     | Write cycle time                                                                             | twc              | 375 |         | 375        |          | 410        |        | ns   |

| tc(rdW)               | Read-modify-write cycle time                                                                 | tRWC             | 375 |         | 375        |          | 515        |        | ns   |

| tw(CH)                | Pulse duration, CAS high (precharge time)                                                    | tCP              | 60  |         | 80         |          | 100        |        | ns   |

| tw(CL)                | Pulse duration, CAS low                                                                      | tCAS             | 100 | 10,000  | 135        | 10,000   | 165        | 10,000 | ns   |

| 1                     | Pulse duration, RAS high (precharge time)                                                    | tRP              | 100 |         | 120        |          | 150        |        | ns   |

| tw(RH)                | Pulse duration, RAS low                                                                      |                  |     | 10.000  | 200        | 10,000   | 250        | 10,000 |      |

| tw(RL)                | Write pulse duration                                                                         | TRAS             | 45  | 10,000  | 55         | 10,000   | 75         | 10,000 | ns   |

| tw(W)                 | Transition times (rise and fall) for                                                         | twp              | 45  |         | 00         |          | /5         |        | ns   |

| tt                    | RAS and CAS                                                                                  | ţ                | 3   | 35      | 3          | 50       | 3          | 50     | ns   |

| tsu(CA)               | Column-address setup time                                                                    | tASC             | -10 |         | -10        |          | -10        |        | ns   |

| t <sub>su(RA)</sub>   | Row-address setup time                                                                       | tASR             | 0   |         | 0          | 2        | 0          |        | ns   |

| tsu(D)                | Data setup time                                                                              | tDS              | 0   |         | 0          | <u> </u> | 0          |        | ns   |

| tsu(rd)               | Read-command setup time                                                                      | tRCS             | 0   | -       | 0          |          | 0          |        | ns   |

| <sup>t</sup> su(WCH)  | Write-command setup time before CAS high                                                     | tCWL             | 60  |         | 80         |          | 100        |        | ns   |

| t <sub>su</sub> (WRH) | Write-command setup time<br>before RAS high                                                  | tRWL             | 60  |         | 80         |          | 100        |        | ns   |

| th(CLCA)              | Column-address hold time<br>after CAS low                                                    | tCAH             | 45  |         | 55         |          | 75         | 1      | ns   |

| th(RA)                | Row-address hold time                                                                        | <sup>t</sup> RAH | 20  |         | 25         |          | 35         | -      | ns   |

| th(RLCA)              | Column-address hold time<br>after RAS low                                                    | tAR              | 95  |         | 120        |          | 160        |        | ns   |

| th(CLD)               | Data hold time after CAS low                                                                 | <sup>t</sup> DHC | 45  |         | 55         |          | 75         |        | ns   |

| th(RLD)               | Data hold time after RAS low                                                                 | TDHR             | 95  |         | 120        |          | 160        |        | ns   |

| th(WLD)               | Data hold time after W low                                                                   | tDHW             | 45  |         | 55         |          | 75         |        | ns   |

| th(rd)                | Read-command hold time                                                                       | tRCH             | 0   |         | 0          |          | 0          |        | ns   |

| th(CLW)               | Write-command hold time<br>after CAS low                                                     | tWCH             | 45  |         | 55         |          | 75         |        | ns   |

| <sup>t</sup> h(RLW)   | Write-command hold time<br>after RAS low                                                     | tWCR             | 95  |         | 120        |          | 160        |        | ns   |

| TRLCH                 | Delay time, RAS low to CAS high                                                              | tCSH             | 150 |         | 200        |          | 250        |        | ns   |

| CHRL                  | Delay time, CAS high to RAS low                                                              | tCRP             | -20 |         | -20        |          | -20        |        | ns   |

| tCLRH                 | Delay time, CAS low to RAS high                                                              | tRSH             | 100 |         | 135        |          | 165        |        | ns   |

| tCLWL                 | Delay time, CAS low to W low<br>(read-modify-write-cycle only)                               | tCWD             | 70  |         | 95         |          | 125        |        | ns   |

| <sup>t</sup> RLCL     | Delay time, RAS low to CAS low<br>(maximum value specified only<br>to guarantee access time) | <sup>t</sup> RCD | 20  | 50      | 25         | 65       | 35         | 85     | ns   |

| TRLWL                 | Delay time, RAS low to W low<br>(read-modify-write-cycle only)                               | tRWD             | 120 |         | 160        |          | 200        |        | ns   |

| tWLCL                 | Delay time, W low to CAS low<br>(early write cycle)                                          | twcs             | -20 |         | -20        |          | -20        |        | ns   |

| trf                   | Refresh time interval                                                                        | tREF             |     | 2       |            | 2        |            | 2      | ms   |

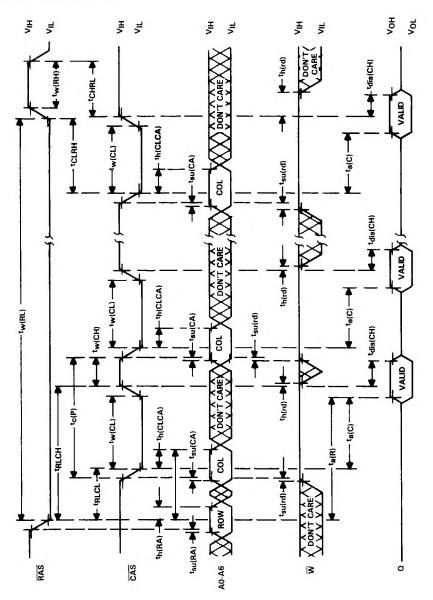

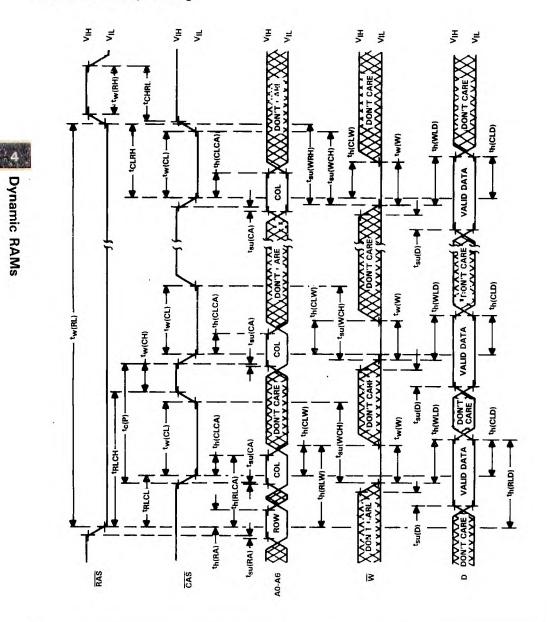

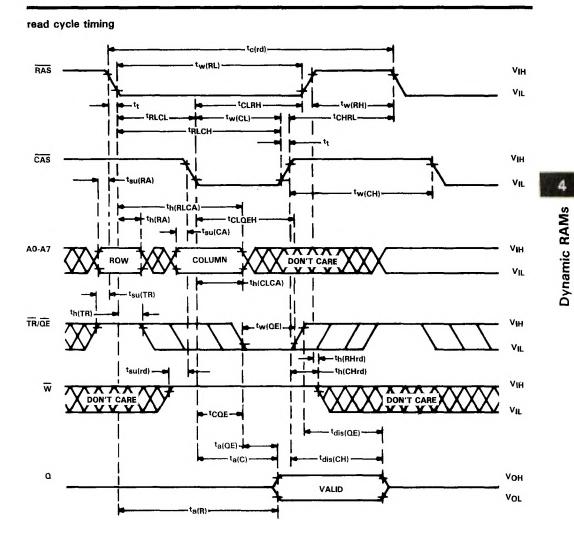

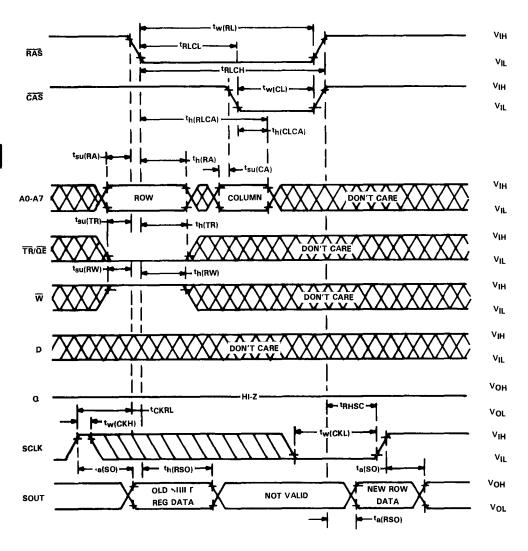

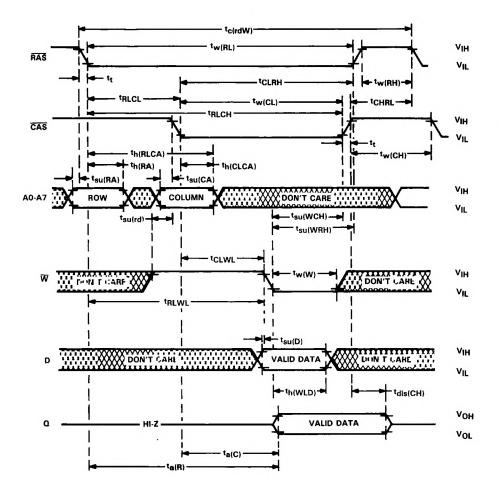

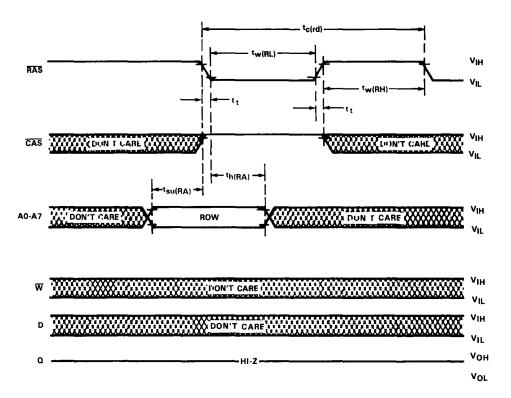

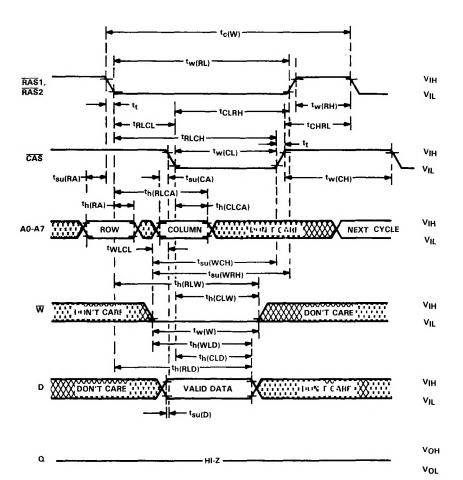

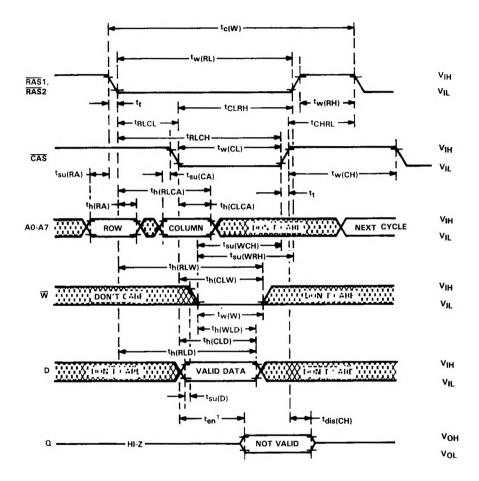

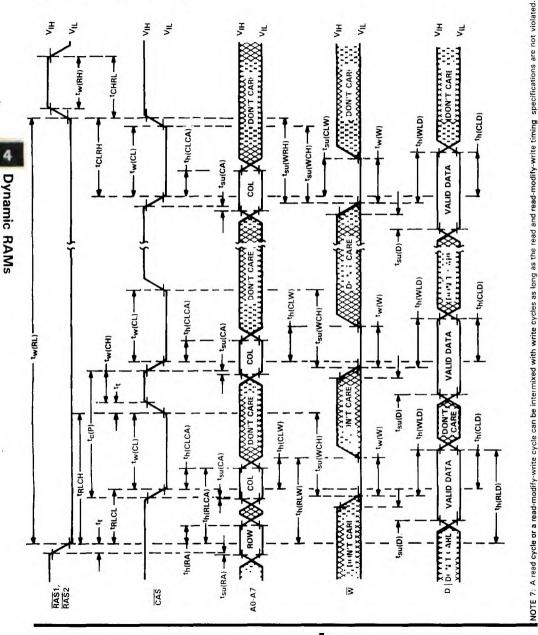

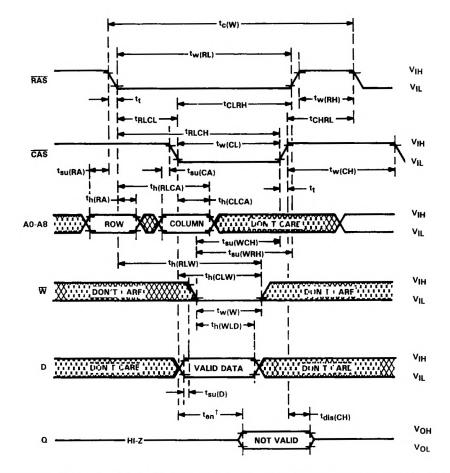

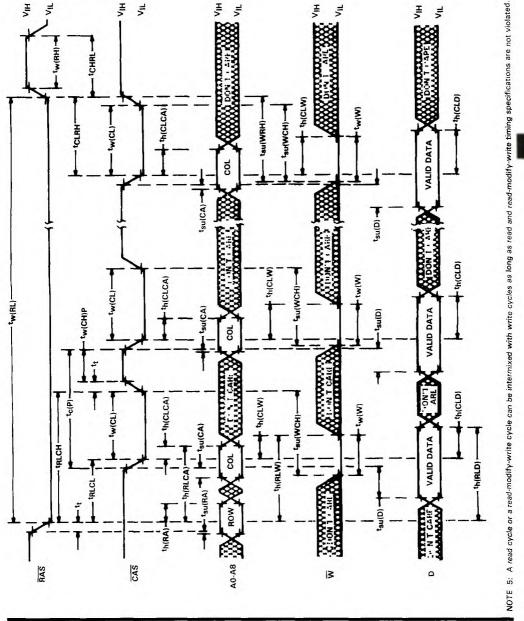

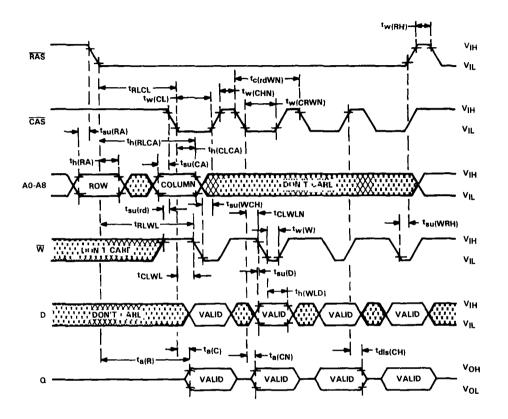

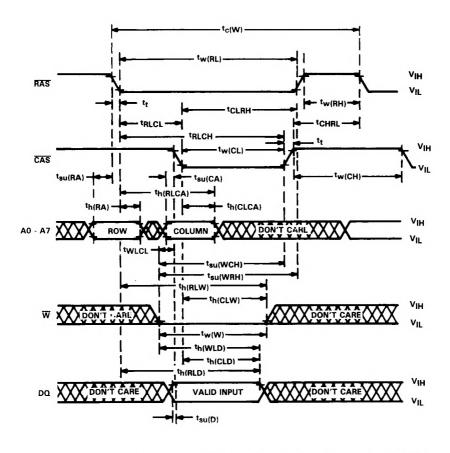

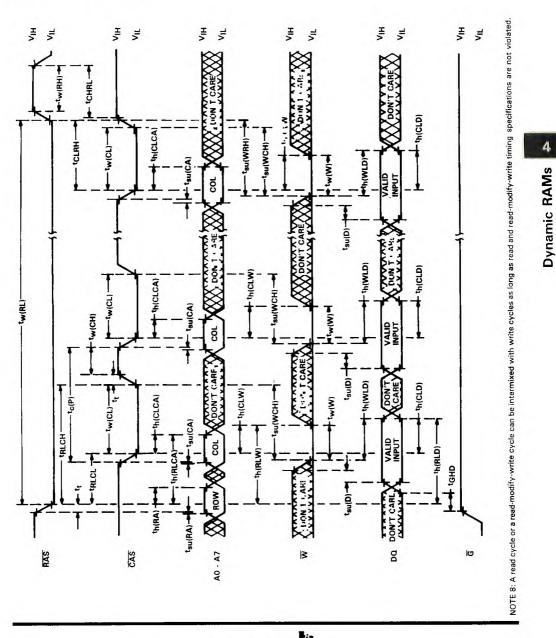

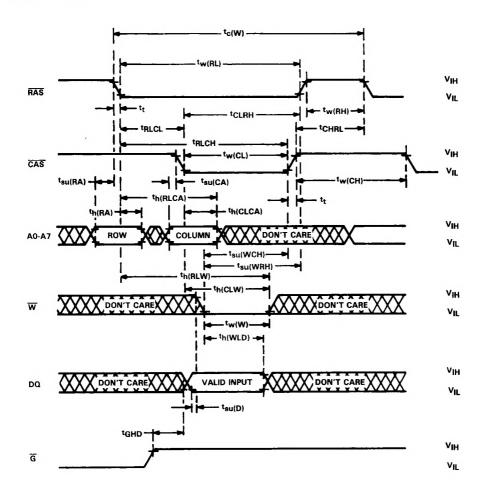

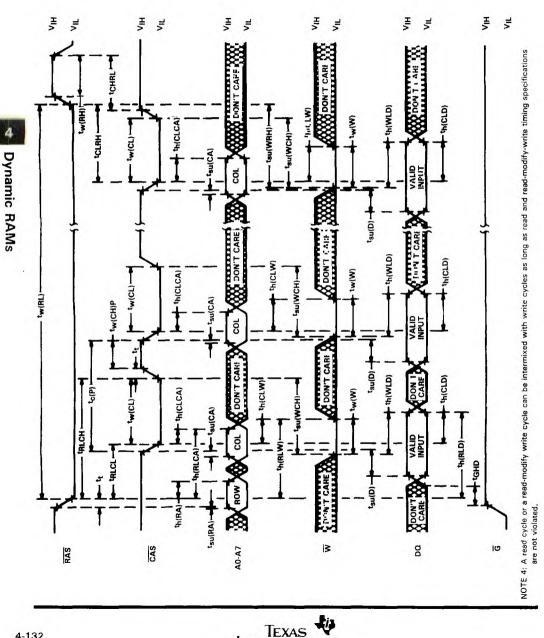

read cycle timing

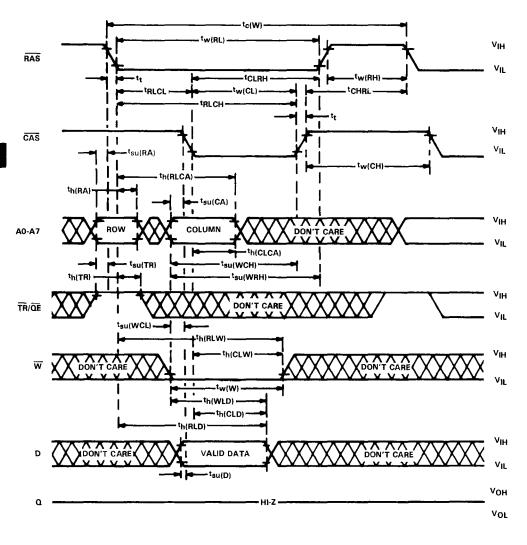

early write cycle timing

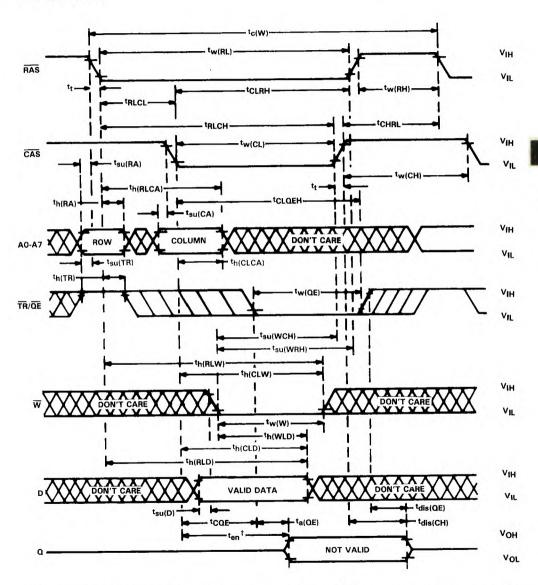

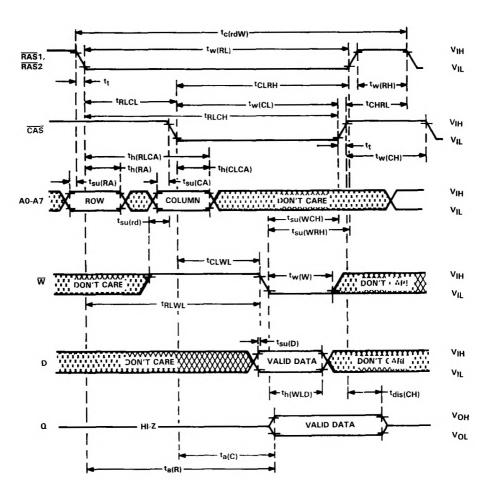

write cycle timing

<sup>†</sup> The enable time (t<sub>en</sub>) for a write cycle is equal in duration to the access time from  $\overline{CAS}$  (t<sub>a(C)</sub>) in a read cycle; but the same active levels at the output are invalid.

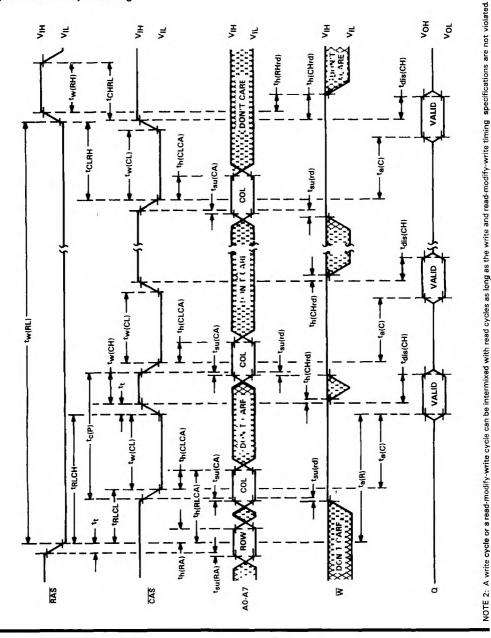

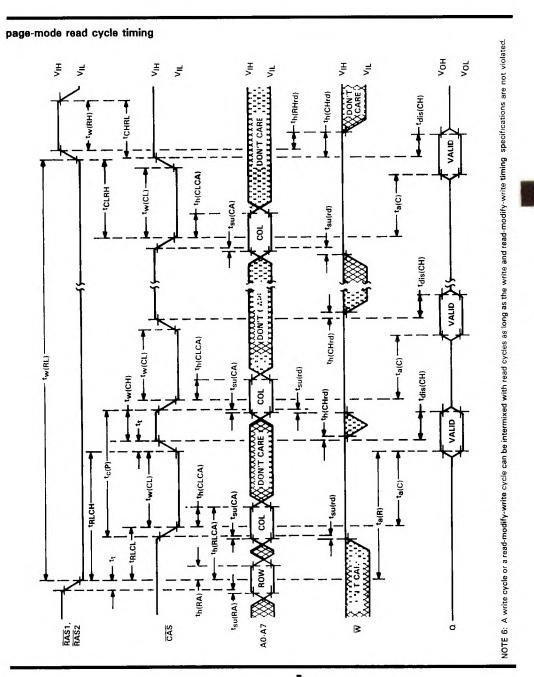

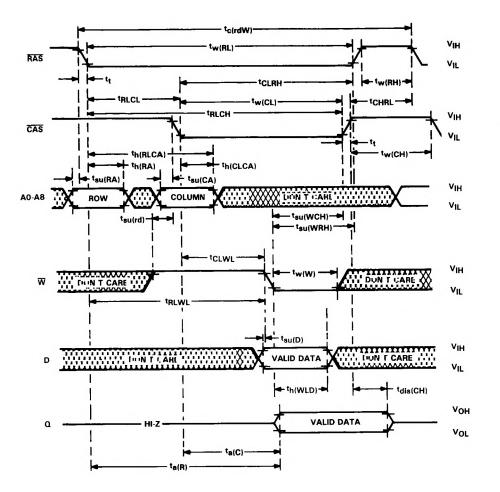

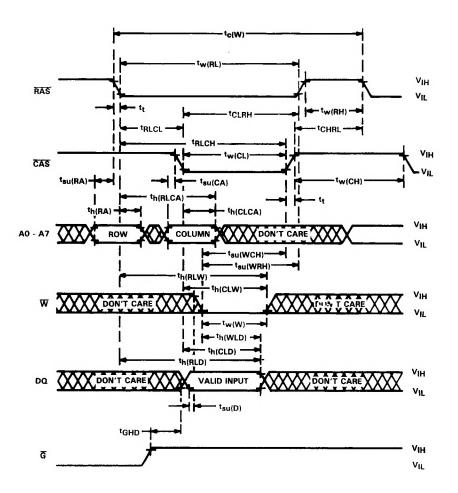

page-mode read cycle timing

İP

TEXAS

INSTRUMENTS POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001 Dynamic RAMs

4

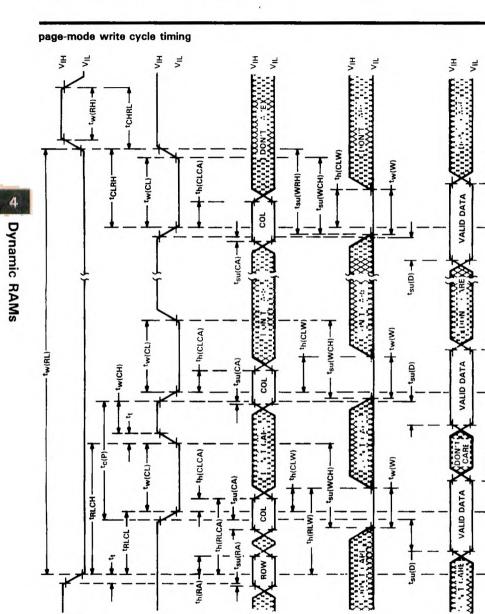

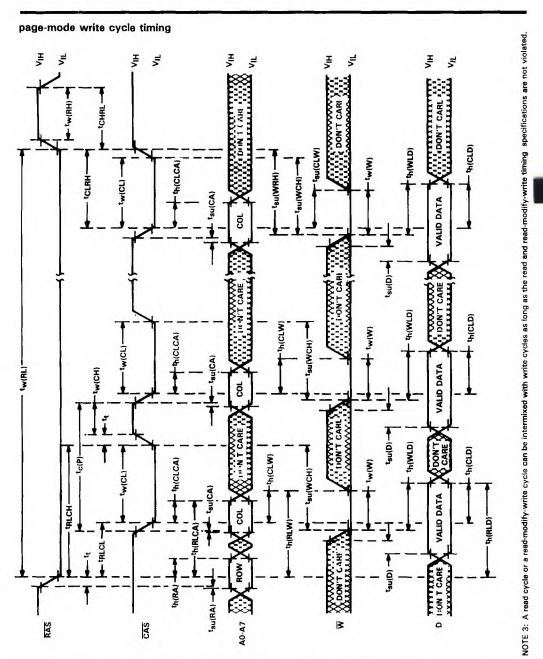

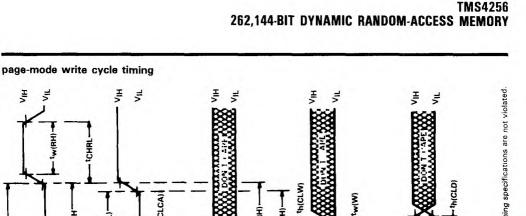

page-mode write cycle timing

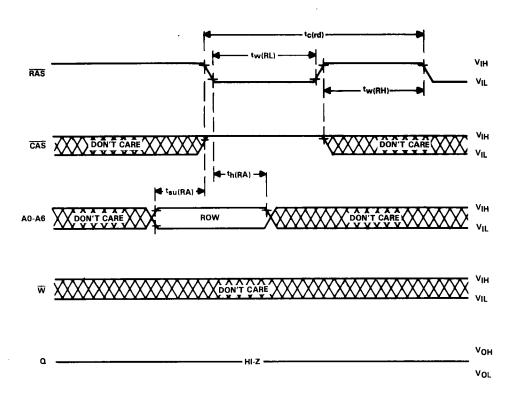

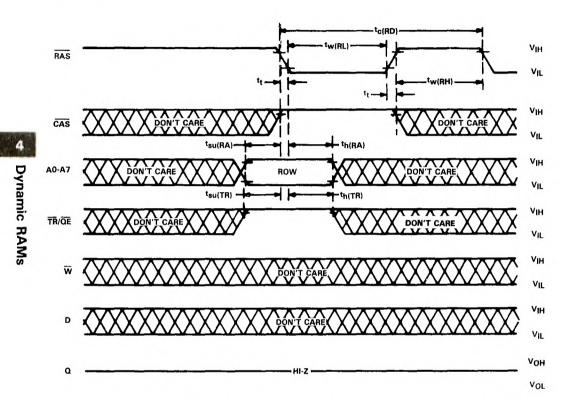

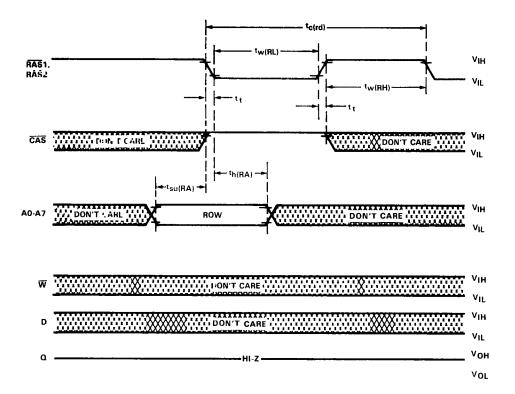

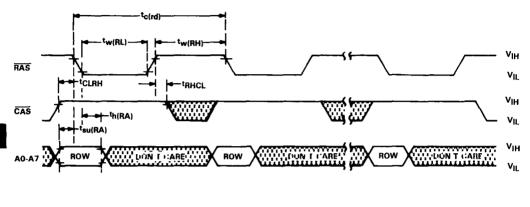

RAS-only refresh timing

4-16

ED NOVEMBER 1985

JULY

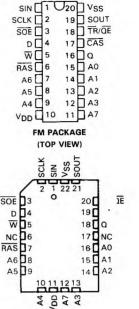

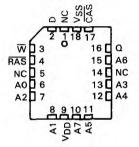

N PACKAGE

- Dual Accessibility One Port Sequential (TOP VIEW) Access, One Port Random Access Four Cascaded 64-Bit Serial Shift Registers for Sequential Access Applications Designed for Both Video and Non-Video Applications Fast Serial Port . . . Can Be Configured for Video Data Rates in Excess of 150 MHz TR/QE as Output Enable Allows Direct Connection of D. Q and Address Lines to **Simplify System Design Random Access Port Looks Exactly Like a** TMS4164 Separate Serial In and Serial Out to Allow . Simultaneous Shift In and Out SOE 3 65.536 × 1 Organization Supported by TI's TMS34061 Video System

- Controller (VSC)

- Maximum Access Time from RAS Less Than 150 ns

- Minimum Cycle Time (Read or Write) Less Than 240 ns

- Long Refresh Period . . . 4 ms

- Low Refresh Overhead Time . . . As Low As 1.7% of Total Refresh Period

- All Inputs, Outputs, Clocks Fully TTL Compatible

- 3-State Unlatched Outputs for Both Random and Serial Access

- Common I/O Capability with "Early Write" Feature

- Page-Mode Operation for Faster Access

- Low Power Dissipation (TMS4161-15) -Operating . . . 250 mW (Typical) -Standby . . . 80 mW (Typical)

- New SMOS (Scaled-MOS) N-Channel Technology

- SOE Simplifies Multiplexing of Serial Data Streams

- Available with MIL-STD-883B Processing and L(0°C to 70°C), E(-40°C to 85°C), or S(-55°C to 100°C) Temperature Ranges

**PRODUCTION DATA** documents contain information current as of publication date. Products conform to specifications per the terms of Taxas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

|       | PIN NOMENO                | CLATURE |                      |

|-------|---------------------------|---------|----------------------|

| A0-A7 | Address Inputs            | SIN     | Serial Data In       |

| CAS   | Column-Address Strobe     | SOE     | Serial Output Enable |

| D     | Random-Access             | SOUT    | Serial Data Out      |

|       | Data In                   | TR/QE   | Register Transfer/   |

| NC    | No Connection             |         | Q Output Enable      |

| a     | Random-Access             | VDD     | 5-V Supply           |

|       | Data Out                  | VSS     | Ground               |

| RAS   | <b>Row-Address Strobe</b> | W       | Write Enable         |

| SCLK  | Serial Data Clock         |         |                      |

Copyright © 1985, Texas Instruments Incorporated

4-17

#### description

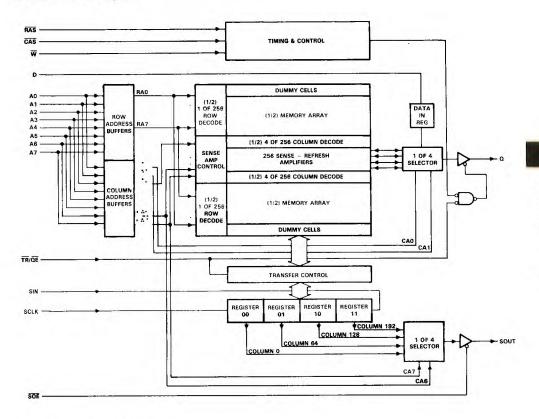

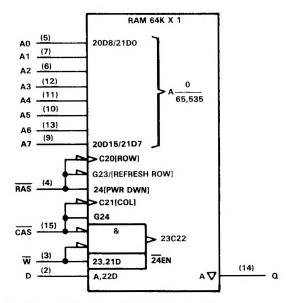

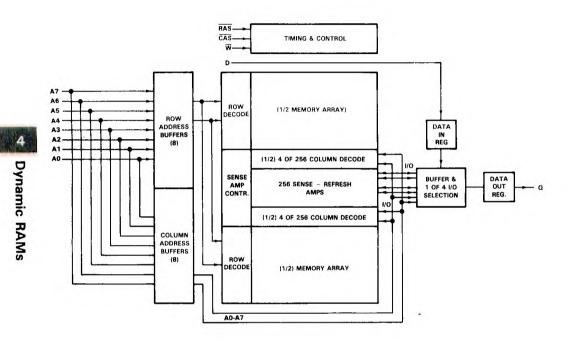

The TMS4161 is a high-speed, dual-access 65,536-bit dynamic random-access memory. The randomaccess port makes the memory look like it is organized as 65,536 words of one bit each like the TMS4164. The sequential access port is interfaced to an internal 256-bit dynamic shift register organized as four cascaded 64-bit shift registers which makes the memory look like it is organized as up to 256 words of up to 256 bits each which are accessed serially. One, two, three, or four 64-bit shift registers can be sequentially read out after a transfer cycle depending on a two-bit code applied to the two most significant column address inputs. The TMS4161 employs state-of-the-art SMOS (Scaled-MOS) N-channel doublelevel polysilicon gate technology for very high performance combined with low cost and improved reliability.

The TMS4161 features full asynchronous dual access capability except when transferring data between the shift register and the memory array.

Refresh period is extended to 4 milliseconds, and during this period each of the 256 rows must be strobed with RAS in order to retain data. CAS can remain high during the refresh sequence to conserve power. Note that the transfer of a row of data from the memory array to the shift register also refreshes that row.

All inputs and outputs, including clocks, are compatible with Series 74 TTL. All address lines and data in are latched on chip to simplify system design. Data out is unlatched to allow greater system flexibility.

The TMS4161 is offered in 20-pin plastic dual-in-line and 22-pin plastic chip carrier packages. It is guaranteed for operation from 0 °C to 70 °C. The dual-in-line package is designed for insertion in mounting-hole rows on 7,62-mm (300-mil) centers.

#### random access address space to sequential address space mapping

The TMS4161 is designed with each row divided into four, 64-column sections (see functional block diagram). The first column section to be shifted out is selected by the two most significant column address bits. If the two bits represent binary 00, then one to four registers can be shifted out in order. If the two bits represent binary 01, then only 1 to 3 (the most significant) registers can be shifted out in order. If the two bits represent 10, then one to two of the most significant registers can be shifted out in order. Finally, if the two bits represent 11 only the most significant register can be shifted out. All registers are shifted out with the least significant bit (bit 0) first and the most significant bit (bit 63) last. Note that if the two column address bits equal 00 during the last register transfer cycle (TR/ $\overline{OE}$  at logic level "O" as RAS falls) a total of 256 bits can be sequentially read out.

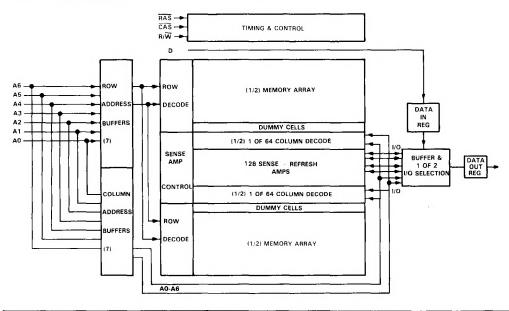

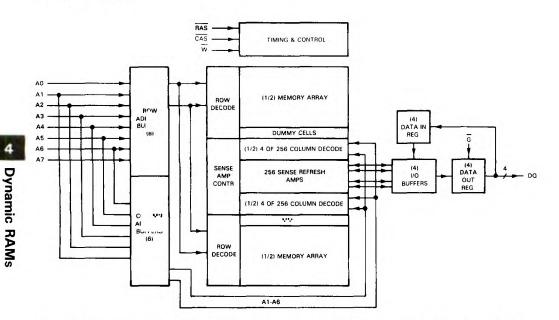

functional block diagram

#### random-access operation

#### TR/QE

The TR/OE pin has two functions. First, it selects either register transfer or random-access operation as RAS falls, and second, if this is a random-access operation, it functions as an output enable after CAS falls.

To use the TMS4161 in the random-access mode,  $\overline{TR}/\overline{QE}$  must be high as  $\overline{RAS}$  falls. Holding  $\overline{TR}/\overline{QE}$  high as  $\overline{RAS}$  falls keeps the 256 elements of the shift registers disconnected from the corresponding 256 bit lines of the memory array. If data is to be shifted, the shift registers must be disconnected from the bit lines. Holding  $\overline{TR}/\overline{QE}$  low as  $\overline{RAS}$  falls enables the 256 switches that connect the shift registers to the bit lines and indicates that a transfer will occur between the shift registers and one of the memory rows.

During random-access operation, once  $\overline{CAS}$  has been pulled low,  $\overline{TR}/\overline{QE}$  controls when the data will appear at the Q output (if this is a read cycle). Whenever  $\overline{TR}/\overline{QE}$  is held high during random-access operation, the Q output will be in the high-impedance state. This feature removes the possibility of an overlap between data on the address lines and data appearing on the Q output making it possible to connect the address lines to the Q and D lines (Use of this organization prohibits the use of the early write cycle.).

4

**Dynamic RAMs**

#### address (A0 through A7)

Sixteen address bits are required to decode 1 of 65,536 storage cell locations. Eight row-address bits are set up on pins A0 through A7 and latched onto the chip by the row-address strobe ( $\overrightarrow{RAS}$ ). Then the eight column-address bits are set up on pins A0 through A7 and latched onto the chip by the column-address strobe ( $\overrightarrow{CAS}$ ). All addresses must be stable on or before the falling edges of  $\overrightarrow{RAS}$  and  $\overrightarrow{CAS}$ .  $\overrightarrow{H}$   $\overrightarrow{H}$   $\overrightarrow{H}$   $\overrightarrow{H}$  similar to a chip enable in that it activates the sense amplifiers as well as the row decoder.  $\overrightarrow{CAS}$  is used as a chip select activating the column decoder and the input and output buffers.

#### write enable (W)

The read or write mode is selected through the write-enable (W) input. A logic high on the  $\overline{W}$  input selects the read mode and a logic low selects the write mode. The write-enable terminal can be driven from standard TTL circuits without a pull-up resistor. The data input is disabled when the read mode is selected. When  $\overline{W}$  goes low prior to  $\overline{CAS}$ , data out will remain in the high-impedance state for the entire cycle permitting common I/O operation.

#### data in (D)

Data is written during a write or read-modify-write cycle. The falling edge of  $\overline{CAS}$  or  $\overline{W}$  strobes data into the on-chip data latch. This latch can be driven from standard TTL circuits without a pull-up resistor. In an early write cycle,  $\overline{W}$  is brought low prior to  $\overline{CAS}$  and the data is strobed in by  $\overline{CAS}$  with setup and hold times referenced to this signal. In a delayed write or read-modify-write cycle,  $\overline{CAS}$  will already be low, thus the data will be strobed in by  $\overline{W}$  with setup and hold times referenced to this signal.

#### data out (Q)

The three-state output buffer provides direct TTL compatibility (no pull-up resistor required) with a fan out of two Series 74 TTL loads. Data c. 1  $\cdot$  the same polarity as data in. The output is in the high-impedance (floating) state as long as  $\overline{CAS}$  or  $\overline{TR}$  .1 s held high. Data will not appear on the output until after both  $\overline{CAS}$  and  $\overline{TR}/\overline{QE}$  have been brought low. In a read cycle, the guaranteed maximum output enable access time is valid only if tCQE is greater than tCQE MAX, and tRLCL is greater than tRLCL MAX. Likewise, ta(C) MAX is valid at 1. if tRLCL is greater than \*RI CL MAX. Once the output is valid, it will remain valid while  $\overline{CAS}$  or  $\overline{TR}$  at going high will return the output to a high-impedance state. In an early write cycle, the output is always in a high-impedance state. In a register transfer cycle, the output will follow the sequence for the read cycle. In a register transfer cycle, the output will always be in a high-impedance state.

#### refresh

A refresh operation must be performed at least every four milliseconds to retain data. Since the output buffer is in high-impedance state unless CAS is applied, the RAS-only refresh service nce avoids any output during refresh. Strobing each of the 256 row addresses (A0 through A7) with the causes all bits in each row to be refreshed. CAS can remain high (inactive) for this refresh sequence to conserve power.

#### page mode

Page-mode operation allows effectively faster memory access by keeping the same row address and strobing successive column addresses onto the chip. Thus, the time required to setup and strobe sequential row addresses for the same page is eliminated. To extend beyond the 256 column locations on a single RAM,

the row address and RAS are applied to multiple 64K RAMs. CAS is then decoded to select the proper RAM.

#### power up

After power up, the power supply must remain at its steady-state value for 1 ms. In addition,  $\overline{RAS}$  must remain high for 100  $\mu$ s immediately prior to initialization. Initialization consists of performing eight  $\overline{RAS}$  cycles before proper device operation is achieved.

#### sequential-access operation

#### TR/QE

Memory transfer operations involving parallel use of the shift register are first indicated by bringing  $\overline{TR}/\overline{QE}$  low before  $\overline{RAS}$  falls low. This enables the switches connecting the 256 elements of the shift register to the 256 bit lines of the memory array. The  $\overline{W}$  line determines whether the data will be transferred from or to the shift registers.

#### write enable (W)

In the sequential access mode,  $\overline{W}$  determines whether a transfer will occur from the shift registers to the memory array, or from the memory array to the shift registers. To transfer from the shift registers to the memory array,  $\overline{W}$  is held low as  $\overline{RAS}$  falls, and, to transfer from the memory array to the shift registers,  $\overline{W}$  is held high as  $\overline{RAS}$  falls. Thus, reads and writes are always with respect to the memory array. The write setup and hold times are referenced to the falling edge of  $\overline{RAS}$  for this mode of operation.

#### row address (A0 through A7)

Eight address bits are required to select one of the 256 possible rows involved in the transfer of data to or from the shift registers. A0-A7,  $\overline{W}$ , and  $\overline{TR}/\overline{QE}$  are latched on the falling edge of  $\overline{RAS}$ .

#### register column address (A7, A6)

To select one of the four shift registers (transfer from memory to register only), the appropriate 2-bit column address (A7, A6) must be valid when  $\overline{CAS}$  falls. However, the  $\overline{CAS}$  and register address signals need not be supplied every transfer cycle, only when it is desired to change or select a new register.

#### SCLK

Data is shifted in and out on the rising edge of SCLK. This makes it possible to view the shift registers as though it were made of 256 rising edge D flip-flops connected D to Q. The TMS4161 is designed to work with a wide range duty cycle clock to simplify system design. Note that data will appear at the SOUT pin not only on the rising edge of SCLK but also after an access time of  $t_a(RSO)$  from RAS high during a parallel load of the shift registers.

#### SIN and SOUT

Data is shifted in through the SIN pin and is shifted out through the SOUT pin. The TMS4161 is designed such that it requires 3 ns hold time on SIN as SCLK rises. SOUT is guaranteed not to change for at least 8 ns after SLCK rises. These features make it possible to easily connect TMS4161s together, to allow SOUT to be connected to SIN, and to give external circuitry a full SLCK cycle time to allow manipulation of the serial data. When loading data into the shift register from the serial input in preparation for a shift register to memory transfer operation, the serial clock must be clocked an even number of times. To guarantee proper serial clock sequence after power up, a transfer cycle must be initiated before a serial data stream is applied at SIN.

#### SOE

The serial output enable pin controls the impedance of the serial output, allowing  $1 \cdots p$  lexing of more than one bank of TMS4161 memories into the same external video circuitry. When  $\cdots$  I is at a logic low level, SOUT will be enabled and the proper data read out. When  $\overline{SOE}$  is at a logic high level, SOUT will be disabled and be in the high-impedance state.

#### refresh

The shift registers are also dynamic storage elements. The data held in the registers will be lost unless SCLK goes high to shift the data one bit position, a transfer write operation is invoked, or the data is reloaded from the memory array. See specifications for maximum register data retention times. Important: If the shift register has remained idle for a time period which exceeds the maximum SCLK high or SCLK low time, the dynamic clock circuits will also lose charge. Under these conditions, the shift register clocks must be re-enabled by performing any transfer cycle before data can be shifted into or out of the shift register.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Voltage range on any pin except VDD and data out (see Note 1)                        |

|--------------------------------------------------------------------------------------|

| Voltage range on V <sub>DD</sub> supply and data out with respect to V <sub>SS</sub> |

| Short circuit output current                                                         |

| Power dissipation                                                                    |

| Operating free-air temperature range                                                 |

| Storage temperature range                                                            |

<sup>†</sup> Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values in this data sheet are with respect to VSS.

#### recommended operating conditions

|     | •                                           | MIN  | NOM | MAX     | UNIT |

|-----|---------------------------------------------|------|-----|---------|------|

| VDD | Supply voltage                              | 4.5  | 5   | 5.5     | V    |

| Vss | Supply voltage                              |      | 0   |         | V    |

| VIH | High-level input voltage                    | 2.4  |     | VDD+0.3 | V    |

| VIL | Low-level input voltage (see Notes 2 and 3) | -0.6 |     |         | V    |

| TA  | Operating free-air temperature              | 0    |     | 70      | °C   |

NOTES: 2. The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used in this data sheet for logic voltage levels only.

Due to input protection circuitry, the applied voltage may begin to clamp at -0.6 V; test conditions must comprehend this occurrence.

4. See application report entitled "TMS4164A and TMS4416 Input Protection Diode" on page 9-5.

4

|                   |                                                          | TEST CONDITIONS                                                                                                                                                          | TMS4161-15 |      |     | TMS4161-20 |                  |     | UNIT |

|-------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-----|------------|------------------|-----|------|

|                   | PARAMETER                                                | TEST CONDITIONS                                                                                                                                                          | MIN        | TYPT | MAX | MIN        | TYP <sup>†</sup> | MAX | UNIT |

| Vон               | High-level output<br>voltage (Q, SOUT)                   | 1 <sub>OH</sub> = -5 mA                                                                                                                                                  | 2.4        |      |     | 2.4        |                  |     | v    |

| Vol               | Low-level output<br>voltage (Q, SOUT)                    | I <sub>OL</sub> = 4.2 mA                                                                                                                                                 |            |      | 0.4 |            |                  | 0.4 | v    |

| ų                 | Input current (leakage)                                  | $V_I = 0 V$ to 5.8 V,<br>$V_{DD} = 5 V$ ,<br>All other pins = 0 V                                                                                                        |            |      | ±10 |            |                  | ±10 | μА   |

| ю                 | Output current (leakage)<br>(Q, SOUT)                    | $V_{O} = 0.4 V \text{ to } 5.5 V,$<br>$V_{DD} = 5 V$                                                                                                                     |            |      | ±10 |            |                  | ±10 | μA   |

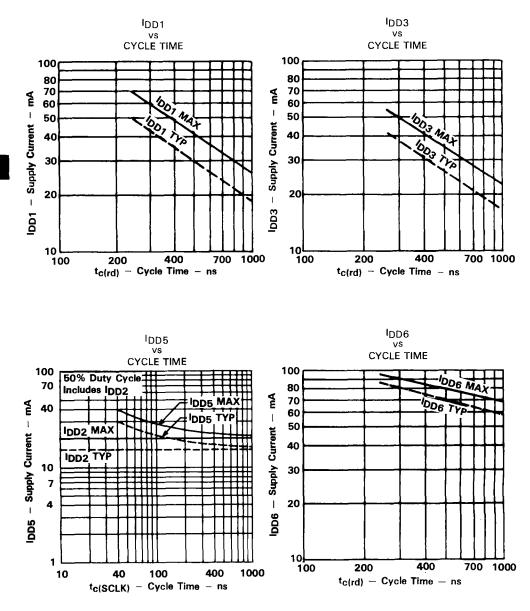

| IDD 1             | Average operating current<br>during read or write cycle  | 1     = minimum cycle time, <sup>+</sup> F     low after RAS falls, <sup>‡</sup> SCLK and SIN low,       SOE high,       No load on Q and SOUT                           |            | 50   | 70  |            | 50               | 70  | mA   |

| IDD2 <sup>§</sup> | Standby current                                          | After 1 RAS cycle,<br>RAS and CAS high,<br>SCLK and SIN low,<br>SOE high,                                                                                                |            | 16   | 20  |            | 16               | 20  | mA   |

| IDD3              | Average refresh current                                  | No load on Q and SOUT<br>= minimum cycle time,<br>nigh, RAS cycling,<br>SCLK and SIN low,<br>SOE high,<br>TR/QE high,<br>No load on Q and SOUT                           |            | 42   | 55  |            | 37               | 50  | mA   |

| <sup>I</sup> DD4  | Average page-mode current                                | t <sub>C(P)</sub> = minimum cycle time,<br>RAS low, CAS cycling,<br>TR/QE low after RAS falls,<br>SCLK and SIN low,<br>SOE high,<br>No load on Q and SOUT                |            | 45   | 55  |            | 40               | 50  | mA   |

| IDD5              | Average shift register<br>current (includes IDD2)        | RAS and CAS high,<br>No load on Q and SOUT,<br>t <sub>c</sub> (SCLK) = t <sub>c</sub> (SCLK) min                                                                         |            | 30   | 40  |            | 30               | 40  | m/   |

| IDD6              | Worst case average<br>DRAM and shift<br>register current | $\begin{array}{l} t_{C(rd)} = \mbox{minimum cycle time,} \\ t_{C(SCLK)} = \mbox{minimum cycle time,} \\ TR/QE low after RAS falls, \\ No load on Q and SOUT \end{array}$ |            | 85   | 95  |            | 80               | 90  | m/   |

electrical characteristics over full range of recommended operating conditions (unless otherwise noted)

NOTE 5: Additional information on  $I_{DD1}-I_{DD6}$  on page 4-40. <sup>†</sup> All typical values are at  $T_A=25\,^{\circ}\text{C}$  and nominal supply voltages. <sup>‡</sup> See appropriate timing diagram. <sup>§</sup>  $V_{JL}>-0.6$  V.

capacitance over recommended supply voltage and operating free-air temperature range, f = 1 MHz

|          | PARAMETER                                  | TYP | MAX | UNIT |

|----------|--------------------------------------------|-----|-----|------|

| Ci(A)    | Input capacitance, address inputs          | 4   | 5   |      |

| Ci(D)    | Input capacitance, data input              | 4   | 5   |      |

| Ci(RC)   | Input capacitance, strobe inputs           | 8   | 10  |      |

| Ci(W)    | Input capacitance, write enable input      | 8   | 10  |      |

| Ci(CK)   | Input capacitance, serial clock            | 8   | 10  |      |

| Ci(SI)   | Input capacitance, serial in               | 4   | 5   | pF   |

| Ci(SOE)  | Input capacitance, serial output enable    | 4   | 5   |      |

| Ci(TR)   | Input capacitance, register transfer input | 4   | 5   | 1    |

| Co(Q)    | Output capacitance, random-access data     | 5   | 7   |      |

| Co(SOUT) | Output capacitance, serial out             | 5   | 7   |      |

<sup>†</sup> All typical values are at  $T_A = 25 \,^{\circ}C$  and nominal supply voltages.

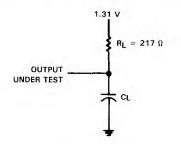

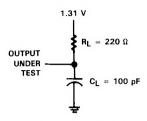

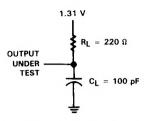

## switching characteristics over recommended supply voltage range and operating free-air temperature range (see Figure 1)

|                                   | PARAMETER                                       | TEST CONDITIONS             | ALT.             | TMS4161-15 | TMS4161-20 |    |  |

|-----------------------------------|-------------------------------------------------|-----------------------------|------------------|------------|------------|----|--|

|                                   |                                                 | TEST CONDITIONS             | SYMBOL           | MIN MAX    | MIN MAX    |    |  |

| ta(C)                             | Access time from CAS                            | $C_L = 100 \text{ pF}$      | <sup>t</sup> CAC | 100        | 135        |    |  |

| ta(QE)                            | Access time of Q from<br>TR/QE low              | $C_L = 100 \text{ pF}$      |                  | 40         | 50         |    |  |

| t <sub>a(R)</sub>                 | Access time from RAS                            | tRLCL = MAX,<br>CL = 100 pF | <sup>t</sup> RAC | 150        | 200        |    |  |

| t <sub>a</sub> (RSO)              | SOUT access time from                           | C <sub>L</sub> = 30 pF      |                  | 65         | 85         |    |  |

| t <sub>a</sub> (SOE)              | Access time from                                | C <sub>L</sub> = 30 pF      |                  | 20         | . 25       | ns |  |

| ta(SO)                            | Access time from SCLK                           | CL = 30 pF                  |                  | 45         | 50         |    |  |

| <sup>t</sup> dis(CH) <sup>‡</sup> | Q output disable time from CAS high             | C <sub>L</sub> = 100 pF     | tOFF             | 40         | 40         |    |  |

| <sup>t</sup> dis(QE) <sup>‡</sup> | Q output disable time<br>from TR/QE high        | C <sub>L</sub> = 100 pF     |                  | 30         | 40         |    |  |

| tdis(SOE) <sup>‡</sup>            | Serial output disable time<br>from • • • • nigh | $C_L = 30 \text{ pF}$       |                  | 20         | 25         |    |  |

<sup>†</sup>Figure 1 shows the load circuit.

<sup>+</sup>The maximum values for t<sub>dis(CH)</sub>, t<sub>dis(QE)</sub>, and t<sub>dis(SOE)</sub> define the time at which the output achieves the open circuit condition and are not referenced to V<sub>OH</sub> or V<sub>OL</sub>.

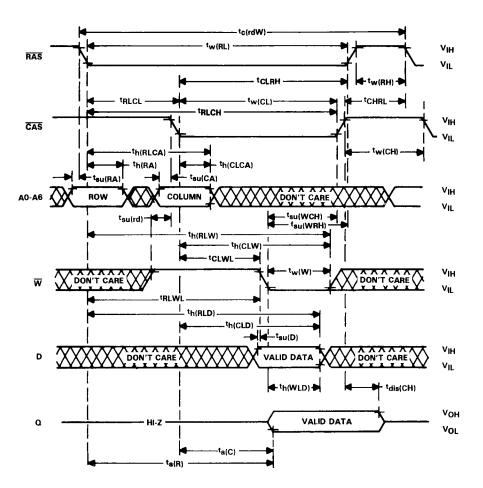

|                       |                                                                                              | ALT.             | 199.41 | 161-15  | 1₩161-20 |             |      |

|-----------------------|----------------------------------------------------------------------------------------------|------------------|--------|---------|----------|-------------|------|

|                       | A second second second second second                                                         | SYMBOL           | MIN    | MAX     | Mille    | MAX         | UNIT |

| t <sub>c(P)</sub>     | Page-mode cycle time                                                                         | tPC              | 160    |         | 225      |             | ns   |

| tc(rd)                | Read cycle time <sup>†</sup>                                                                 | <b>t</b> RC      | 240    |         | 315      | 1.00        | ns   |

| t <sub>c(W)</sub>     | Write cycle time                                                                             | tWC              | 240    |         | 315      |             | ns   |

| tc(TW)                | Transfer write cycle time <sup>‡</sup>                                                       |                  | 240    | 1.1     | 315      |             | ns   |

| tc(Trd)               | Transfer read cycle time                                                                     |                  | 240    | 199     | 315      |             | ns   |

| tc(rdW)               | Read-write/read-modify-write cycle time                                                      | tRWC             | 265    | 1.23    | 330      | 1.1.1.1.1.1 | ns   |

| tc(SCLK)              | Serial-clock cycle time                                                                      | tSCC             | 45     | 50,000  | 50       | 50,000      | ns   |

| tw(CH)                | Pulse duration, CAS high (precharge time§                                                    | tCP              | 50     |         | 80       |             | ns   |

| tw(CL)                | Pulse duration, CAS low¶                                                                     | tCAS             | 100    | 10,000  | 135      | 10,000      | ns   |

| tw(RH)                | Pulse duration, RAS high (precharge time)                                                    | tRP              | 80     |         | 105      |             | ns   |

| tw(RL)                | Pulse duration, RAS low#                                                                     | tRAS             | 150    | 10,000  | 200      | 10,000      | ns   |

| tw(W)                 | Write pulse duration                                                                         | tWP              | 45     |         | 45       |             | ns   |

| tw(CKL)               | Pulse duration, SCLK low                                                                     |                  | 10     |         | 10       | (a. 2 a f   | ns   |

| tw(CKH)               | Pulse duration, SCLK high                                                                    |                  | 12     |         | 12       |             | ns   |

| tw(QE)                | TR/QE pulse duration low time (read cycle)                                                   |                  | 40     |         | 40       |             | ns   |

| tt                    | Transition times (rise and fall)<br>RAS, CAS, and SCLK                                       | tŢ               | 3      | 50      | 3        | 50          | ns   |

| tsu(CA)               | Column-address setup time                                                                    | tASC             | 0      | 1       | 0        | 100         | ns   |

| t <sub>su(RA)</sub>   | Row-address setup time                                                                       | tASR             | 0      |         | 0        |             | ns   |

| t <sub>su(RW)</sub>   | $\overline{W}$ setup time before $\overline{RAS}$ low with $\overline{TR}/\overline{QE}$ low |                  | 0      |         | 0        |             | ns   |

| t <sub>su(D)</sub>    | Data setup time                                                                              | tDS              | 0      |         | 0        |             | ns   |

| tsu(rd)               | Read-command setup time                                                                      | tRCS             | 0      |         | 0        |             | ns   |

| tsu(WCL)              | Early write-command setup time before CAS low                                                | twcs             | - 5    |         | - 5      |             | ns   |

| t <sub>su</sub> (WCH) | Write-command setup time before CAS high                                                     | tCWL             | 40     |         | 60       | 1.1         | ns   |

| t <sub>su</sub> (WRH) | Write-command setup time before RAS high                                                     | tRWL             | 40     |         | 60       | 1.1.1       | ns   |

| tsu(TR)               | TR/QE setup time before RAS low                                                              |                  | 0      |         | 0        |             | ns   |

| t <sub>su</sub> (SI)  | Serial-data setup time before SCLK high                                                      |                  | 6      |         | 6        |             | ns   |

| th(SI)                | Serial-data-in hold time after SCLK high                                                     |                  | 3      |         | 3        | (           | ns   |

| th(CLCA)              | Column-address hold time after CAS low                                                       | tCAH             | 45     |         | 55       |             | ns   |

| th(RA)                | Row-address hold time                                                                        | <sup>t</sup> RAH | 20     |         | 25       |             | ns   |

| th(RW)                | W hold time after RAS low with TR/QE low                                                     |                  | 20     |         | 20       |             | ns   |

| th(RLCA)              | Column-address hold time after RAS low                                                       | tAR              | 95     |         | 120      | 1.2.17      | ns   |

| th(CLD)               | Data hold time after CAS low                                                                 | tDH              | 60     | 0.000   | 80       |             | ns   |

| th(RLD)               | Data hold time after RAS low                                                                 | tDHR             | 110    | 1.23    | 145      |             | ns   |

| th(WLD)               | Data hold time after W low                                                                   | tDH              | 45     |         | 55       |             | ns   |

| th(CHrd)              | Read-command hold time after CAS high                                                        | tRCH             | 0      | 1.1.1.1 | 0        |             | ns   |

(Continued next page.)

NOTE 6: Timing measurements are made at the 10% and 90% points of input and clock transitions. In addition, VIL max and VIH min must be met at the 10% and 90% points.

<sup>†</sup>All cycle times assume  $t_t = 5$  ns except  $t_c(SCLK)$  which assumes  $t_t = 3$  ns.

\*Multiple transfer write cycles require separation by either a 500 ns RAS-precharge interval or any other active RAS-cycle. §Page-mode only.

In a read-modify-write cycle, t<sub>CLWL</sub> and t<sub>su(WCH)</sub> must be observed. Depending on the user's transition times, this may require additional CAS low time (t<sub>W(CL)</sub>). This applies to page-mode read-modify-write also.

#In a read-modify-write cycle, tRLWL and t<sub>SU(WRH)</sub> must be observed. Depending on the user's transition times, this may require additional RAS low time (tw(RL)).

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ALT.             | TMS4161-15 |        | TMS4161-15 TMS4161-20 |        | UNIT |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|--------|-----------------------|--------|------|

|                    | and the second se | SYMBOL           | MIN        | MAX    | MIN                   | MAX    | UNIT |

| th(RHrd)           | Read-command hold time after RAS high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | tRRH             | 5          |        | 5                     |        | ns   |

| th(CLW)            | Write-command hold time after CAS low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | tWCH             | 60         |        | 80                    |        | ns   |

| th(RLW)            | Write-command hold time after RAS low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | tWCR             | 110        |        | 145                   |        | ns   |

| th(RSO)            | Serial-data-out hold time after<br>RAS low with TR/QE low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  | 30         |        | 30                    |        | ns   |

| th(SO)             | Serial-data-out hold time after SCLK high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  | 8          |        | 8                     |        | ns   |

| th(TR)             | TR/QE hold time after RAS low (transfer)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  | 20         |        | 20                    |        | ns   |

| TRLCH              | Delay time, RAS low to CAS high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | tCSH             | 150        |        | 200                   |        | ns   |

| <sup>t</sup> CHRL  | Delay time, CAS high to RAS low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | tCRP             | 0          |        | 0                     |        | ns   |

| <sup>t</sup> CLQEH | Delay time, CAS low to QE high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  | 100        |        | 135                   |        | лѕ   |

| <sup>t</sup> CLRH  | Delay time, CAS low to RAS high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | tRSH             | 100        |        | 135                   |        | ns   |

| tCLWL              | Delay time, CAS low to W low<br>(read-modify-write cycle only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | tCWD             | 65         |        | 75                    |        | ns   |

| <sup>t</sup> CQE   | Delay time, ow to QE low<br>(maximum value specified only<br>to guarantee t <sub>a(QE)</sub> access time)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |            | 60     |                       | 85     | ns   |

| TRHSC              | Delay time, RAS high to SCLK high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  | 80         | 50,000 | 80                    | 50,000 | ns   |

| <sup>t</sup> RLCL  | Delay time, RAS low to CAS low (maximum value specified only to guarantee access time)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | tRCD             | 25         | 50     | 30                    | 65     | ns   |

| <sup>t</sup> RLWL  | Delay time, RAS low to W low<br>(read-modify-write cycle only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <sup>t</sup> RWD | 135        |        | 150                   |        | ns   |

| <sup>t</sup> CKRL  | Delay time, SCLK high before<br>RAS low with TR/QE low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  | 10         | 50,000 | 10                    | 50,000 | ns   |

| trf(MA)            | Refresh time interval, memory array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | tREF1            |            | 4      |                       | 4      | ms   |

| trf(SR)            | Refresh time interval, shift register \$\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | tREF2            |            | 50,000 |                       | 50,000 | ns   |

timing requirements over recommended supply voltage range and operating free-air temperature range (concluded)

NOTE 6: Timing measurements are made at the 10% and 90% points of input and clock transitions. In addition, V<sub>IL</sub> max and V<sub>IH</sub> min must be met at the 10% and 90% points.

SCLK may be high or low during t<sub>W(RL)</sub>, but there can not be any positive edge transitions on SCLK for a minimum of 10 ns prior to RAS going low with TR/QE low (i.e., before a transfer cycle).

☆See "refresh" on page 4-22.

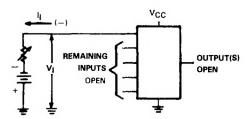

### PARAMETER MEASUREMENT INFORMATION

FIGURE 1. LOAD CIRCUIT

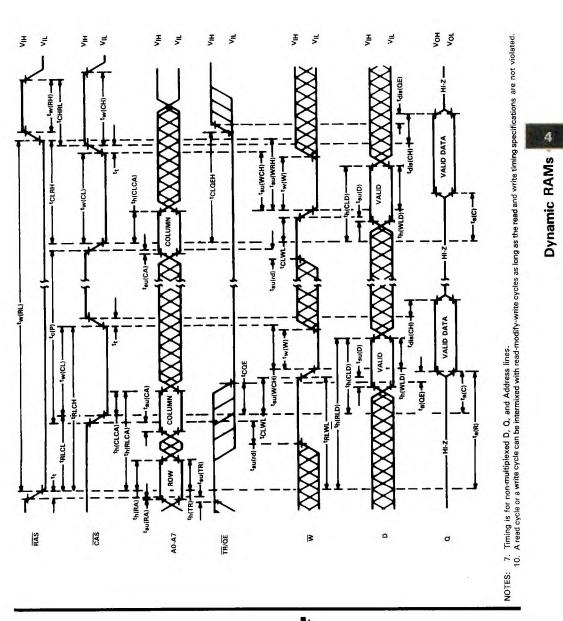

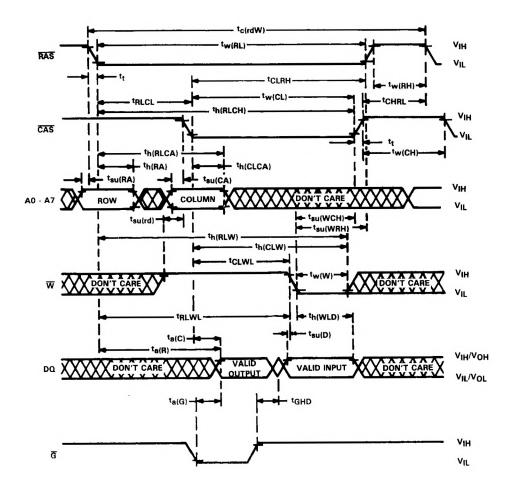

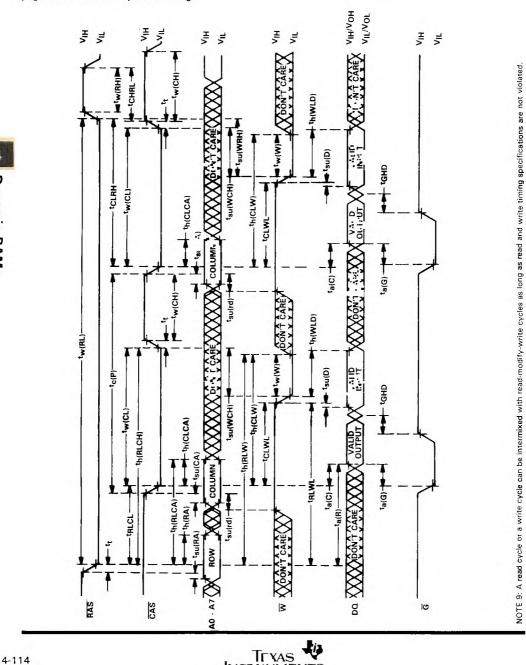

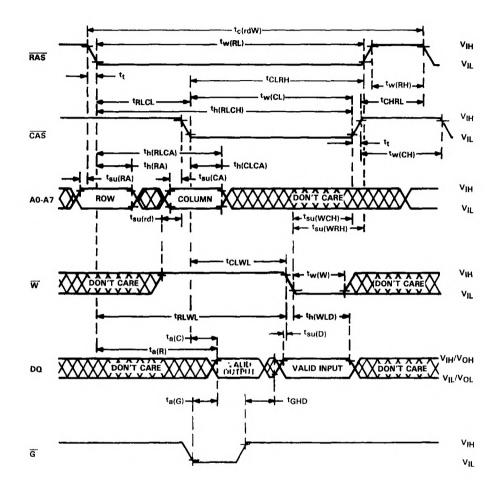

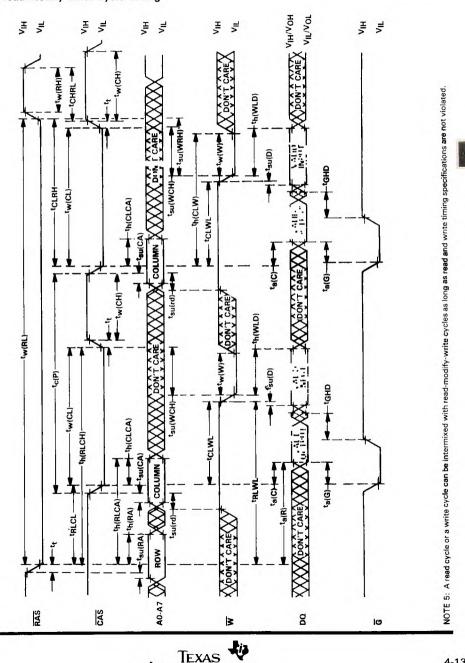

early write cycle timing

Dynamic RAMs

write cycle timing

<sup>†</sup>The enable time (t<sub>en</sub>) for a write cycle is equal in duration to the access time from CAS (t<sub>a(C)</sub>) in a read cycle; but the active levels at the output are invalid.

4

**Dynamic RAMs**

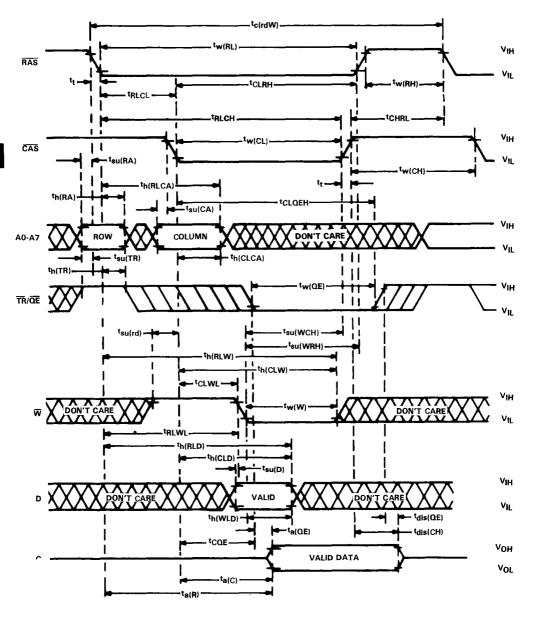

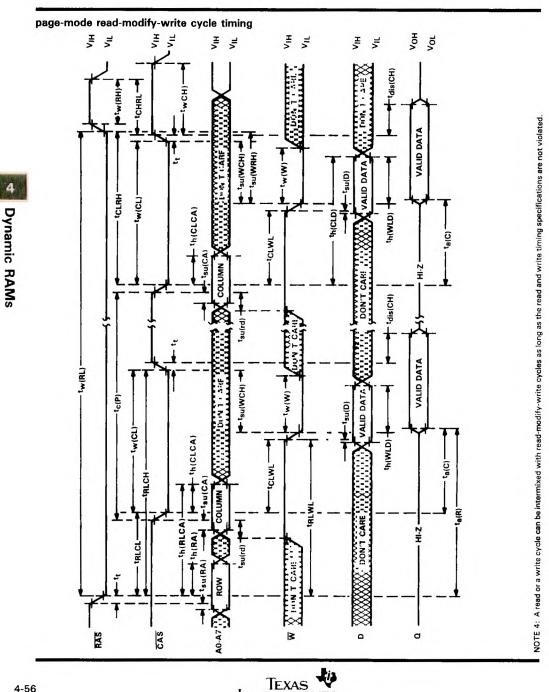

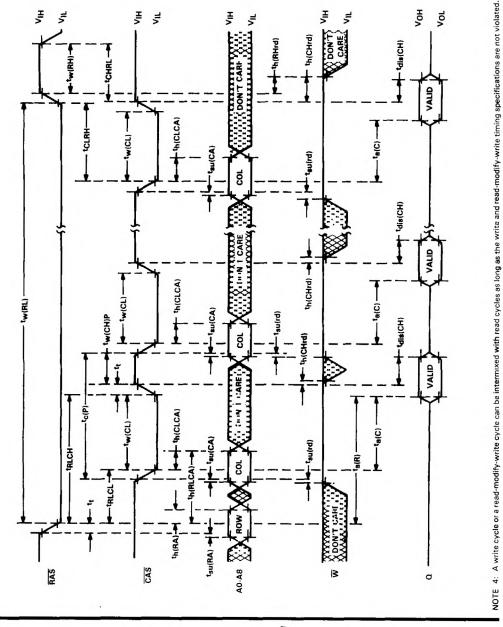

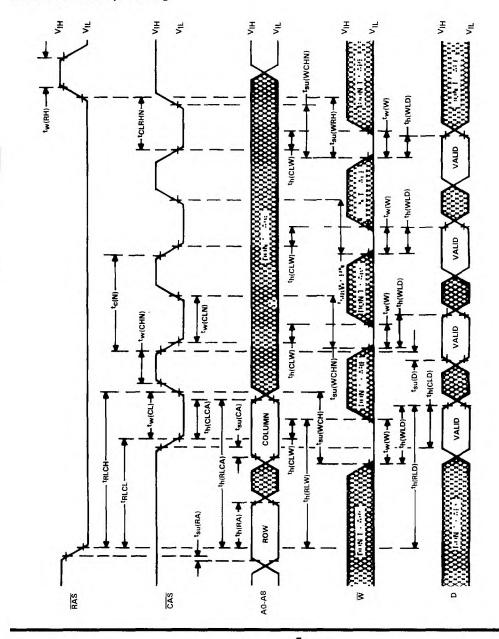

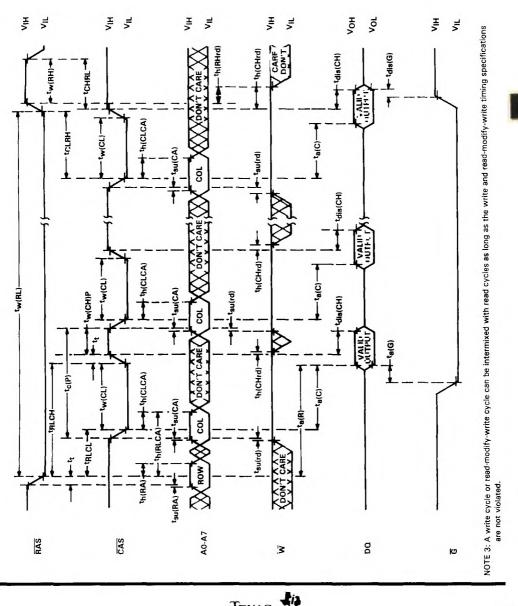

read-write/read-modify-write cycle timing

4

TEXAS TEXAS INSTRUMENTS POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001

4-31

4

**Dynamic RAMs**

th(RA)

CAS

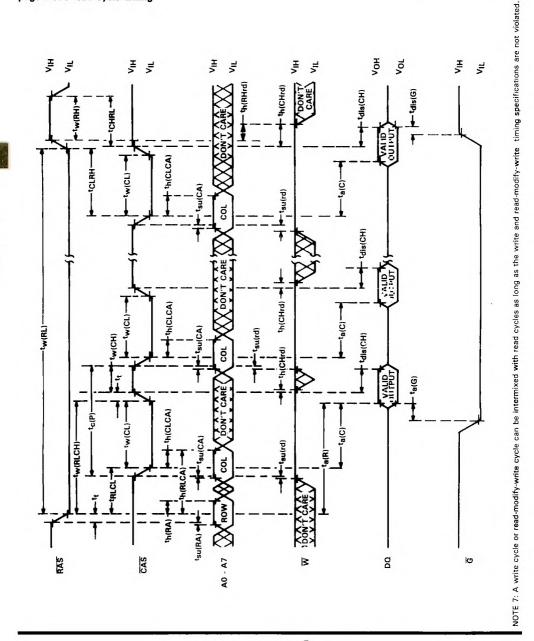

A read cycle or a read-modify-write cycle can be intermixed with write cycles as long as the read and read-modify-write timing specifications are not violated. Timing is for non-multiplexed D, Q, and Address lines. ~ 0 NOTES:

th(CLD)

th(CLD)

th(CLD)

DQ1-DQ8

th(RLD)

13

A0-A7

RAS

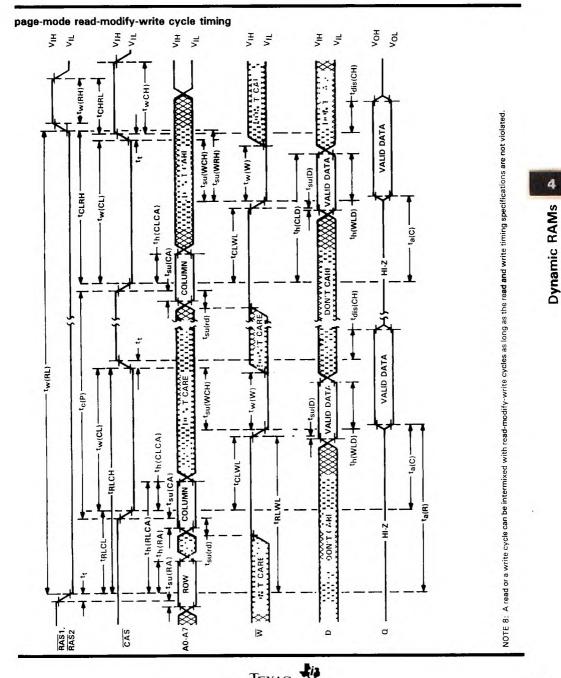

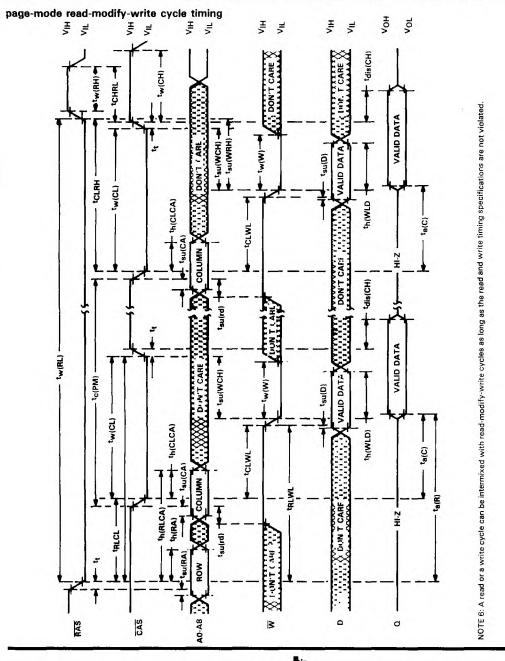

page-mode read-modify-write cycle timing

.

TEXAS VI INSTRUMENTS POST OFFICE BOX 1443 • HOUSTON. TEXAS 77001

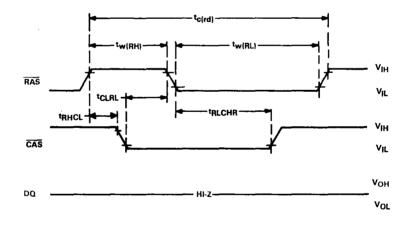

**RAS**-only refresh timing

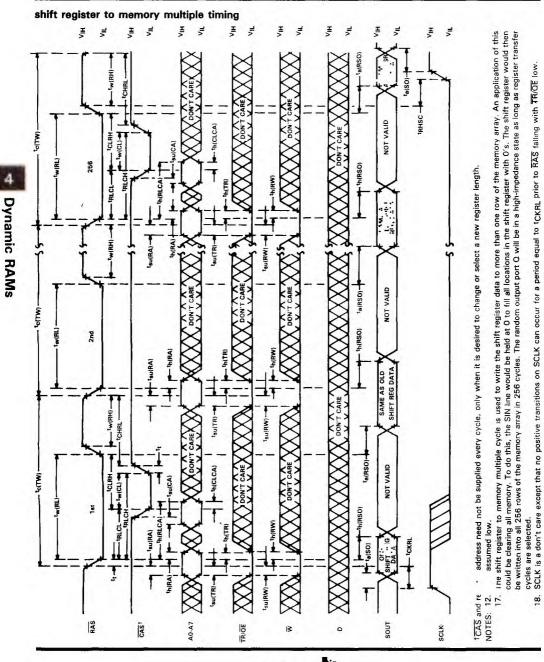

#### shift register to memory timing

- - 12. \*\* rows.

- 13. SCLK may be high or low during tw(RL).

4

**Dynamic RAMs**

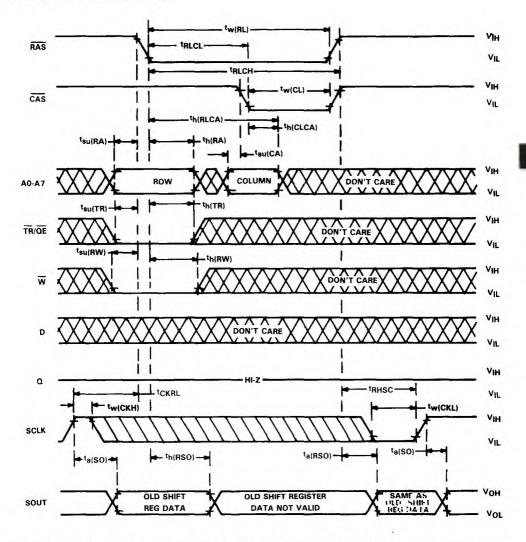

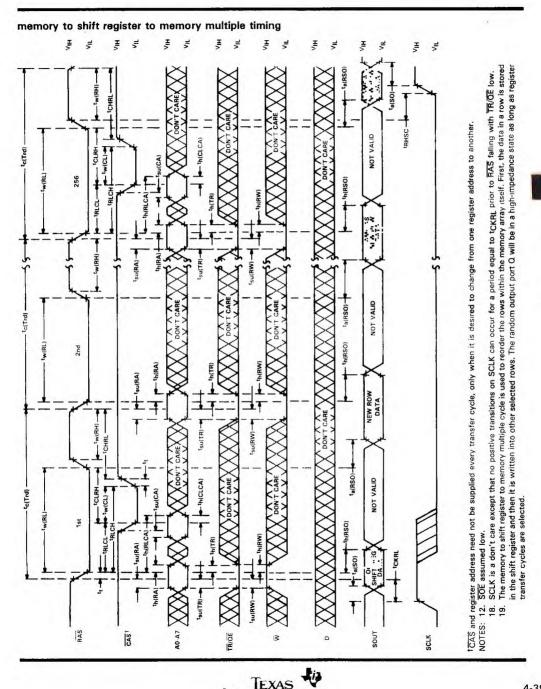

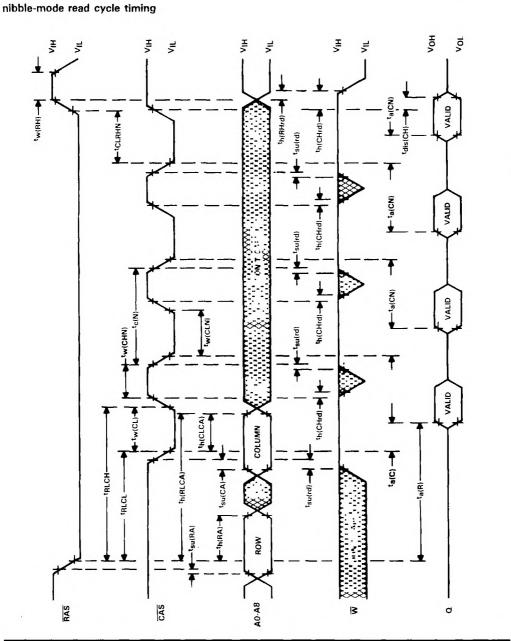

memory to shift register timing

NOTES: 12.  $\overline{\text{SOE}}$  assumed low.

13. SCLK may be high or low during tw(RL).

14. The memory to shift register cycle is used to load the shift register in parallel from the memory array. Every one of the 256 locations in the shift register are written into from the 256 columns of the selected row. Note that the data that is loaded into the shift register may be either shifted out or written back into another row.

4

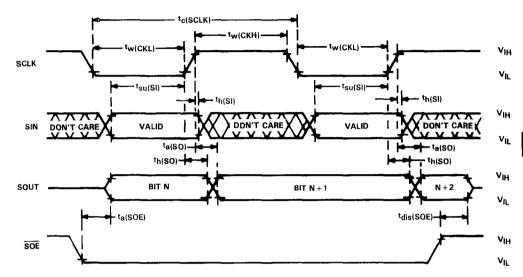

### serial data shift timing

- NOTES: 15. When loading data into the shift register from the serial input in preparation for a shift register to memory transfer operation, the serial clock must be clocked an even number of times.

- 16. While shifting data through the serial shift register, the state of TR/QE is a don't care as long as TR/QE is held high when RAS goes low and t<sub>su(TR)</sub> and t<sub>h(TR)</sub> timings are observed. This requirement avoids the initiation of a register-to-memory or memory-to-register data transfer operation. The serial data transfer cycle is used to shift data in and/or out of the shift register.

### TMS4161 65,536-BIT MULTIPORT VIDEO RAM

TEXAS W INSTRUMENTS POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001

# TMS4161 65,536-BIT MULTIPORT VIDEO RAM

INSTRUMENTS POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001 4-39

4

**Dynamic RAMs**

# TMS4161 65,536-BIT MULTIPORT VIDEO RAM