## 1982/83

Data Book

**Zilog** Pioneering the Microworld

Copyright 1981, 1982 by Zılog, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Zilog. The information contained herein is subject to change

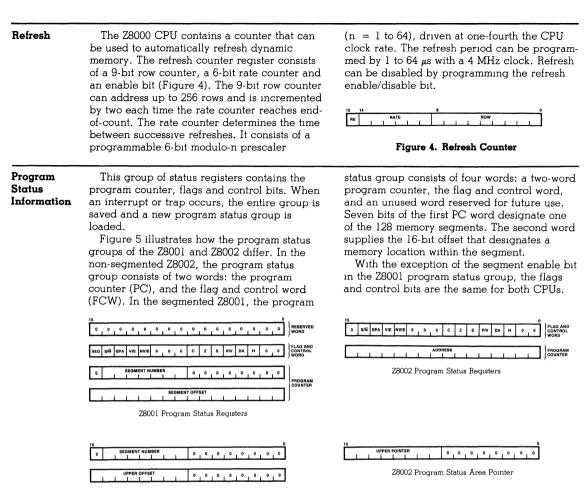

The information contained herein is subject to change without notice. Zilog assumes no responsibility for the use of any circuitry other than circuitry embodied in a Zilog product. No other circuit patient licenses are implied

## **Microcomputers in Every Form**

Zilog offers microcomputers in every form: from components and development systems to board-level products and complete generalpurpose microcomputer systems. This edition of the *Zilog Data Book* describes Zilog components, development systems, and microcomputer boards. You'll also find a section on the in-depth training courses now offered about most Zilog products.

Zilog components, the basic building blocks for our other microcomputer products, include the 8-bit Z80<sup>®</sup> Microprocessor and its family of intelligent peripherals, the Z8<sup>TM</sup> Family of Single-Chip Microcomputers, and the 16-bit Z8000<sup>TM</sup> Microprocessor and its family of intelligent peripherals.

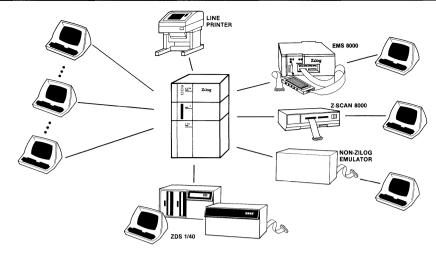

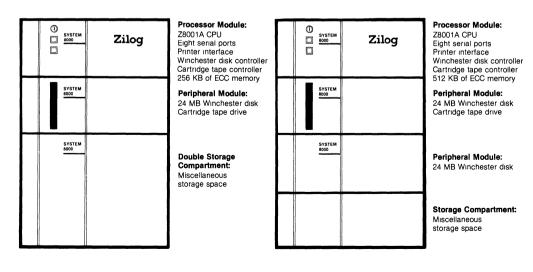

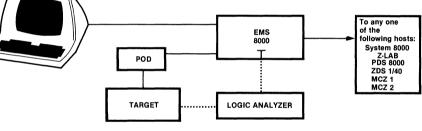

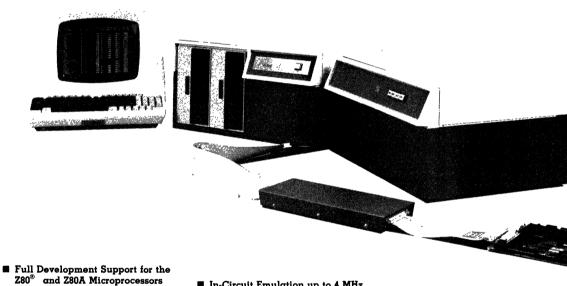

Zilog offers a wide variety of development environments, ranging from the inexpensive Z8 and Z8000 Development Modules to the more elaborate PDS 8000 and ZDS-1 Development Systems to the ultra-sophisticated multi-user Z-LAB 8000 Development System. In addition, EMS 8000 and Z-SCAN 8000 both provide in-circuit emulation for the Z8001 and Z8002 Microprocessors.

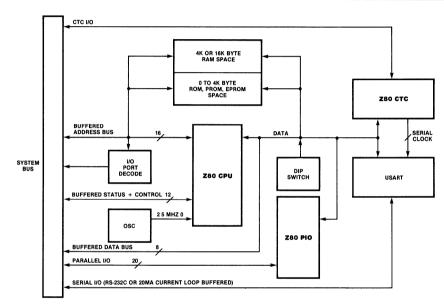

Our Z80 MCB Board Family offers a complete solution for prototype and production designs in which you don't want to design a microcomputer from scratch. This well-established family includes a Z80 CPU board, several types of memory boards, and boards for all types of digital and analog I/O. A complete set of card cages, enclosures, and other accessories makes this family easy to use.

ļ

## **Table of Contents**

| Z80 Family         Z8400 CPU Central Processing Unit         Z8300 CPU Central Processing Unit         Z8410 DMA Direct Memory Access         Z8420 PIO Parallel Input/Output         Z8430 CTC Counter/Timer Circuit         Z8440/1/2 SIO Serial Input/Output Controller         Z8470 DART Dual Asynchronous Receiver/Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5<br>27<br>49<br>67<br>81<br>93                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Z8000       Family         Z8001/2       CPU Central Processing Unit         Z8003/4       VMPU Virtual Memory Processing Unit         Z8010       Z-MMU Memory Management Unit         Z8015       PMMU Paged Memory Management Unit         Z8016       DTC Direct Memory Access Transfer Controller         Z8030       Z-SCC Serial Communications Controller         Z8031       Z-ASCC Asynchronous Serial Communications Controller         Z8038       Z-FIO FIFO Input/Output Interface Unit         Z8068       Z-FIO FIFO Input/Output Interface Unit         Z8068       Z-BEP Burst Error Processor         Z8068       Z-DCP Data Ciphering Processor         Z8070       Floating Point Package         Z8090       Z-UPC Universal Peripheral Controller | 125<br>153<br>155<br>171<br>173<br>175<br>197<br>217<br>241<br>273<br>281<br>295<br>311 |

| Universal Peripherals<br>Z8530 SCC Serial Communications Controller<br>Z8531 ASCC Asynchronous Serial Communications Controller<br>Z8536 CIO Counter/Timer and Parallel I/O Unit<br>Z8538 FIO—See Z8038 Z-FIO<br>Z8581 Clock Generator and Controller<br>Z8590 UPC Universal Peripheral Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 337<br>359<br>379<br>241<br>403                                                         |

| <b>28 Family</b><br>Z8601/2/3 MCU Microcomputer<br>Z8611/2/3 MCU Microcomputer<br>Z8671 MCU Microcomputer with BASIC/Debug Interpreter<br>Z8681 MCU Microcomputer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 431<br>449<br>467                                                                       |

| Additional Information<br>Zilog Z-BUS Component Interconnect<br>Z-BUS Backplane Interconnect<br>Advanced Architectural Features of the Z8000 CPU<br>An Introduction to the Z8010 MMU<br>High Reliability Microcircuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 493<br>497<br>511                                                                       |

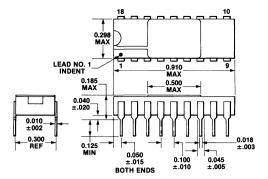

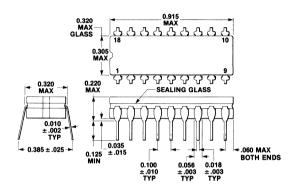

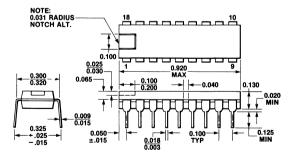

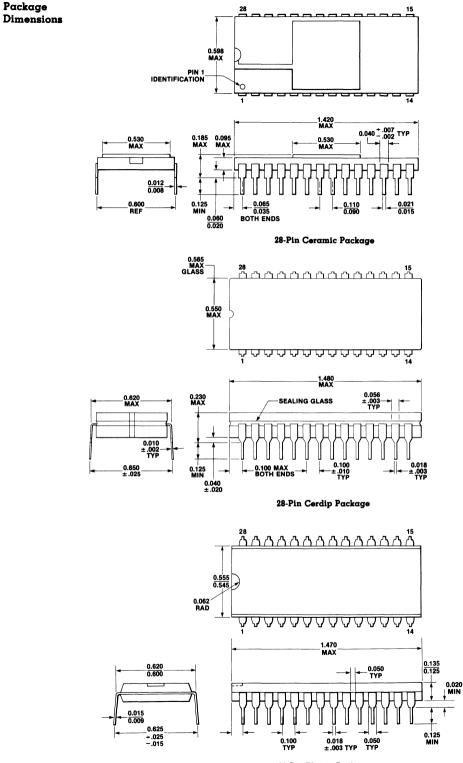

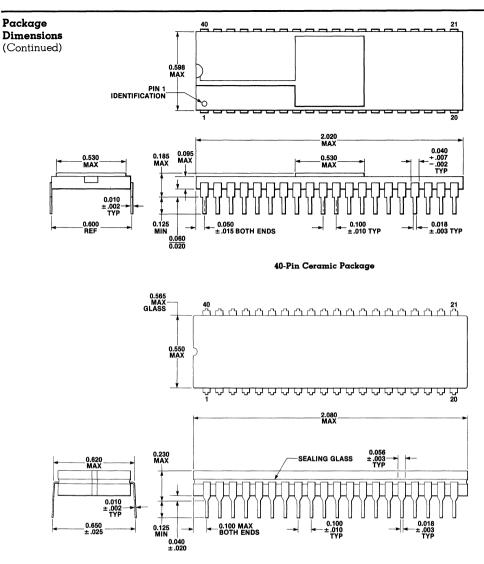

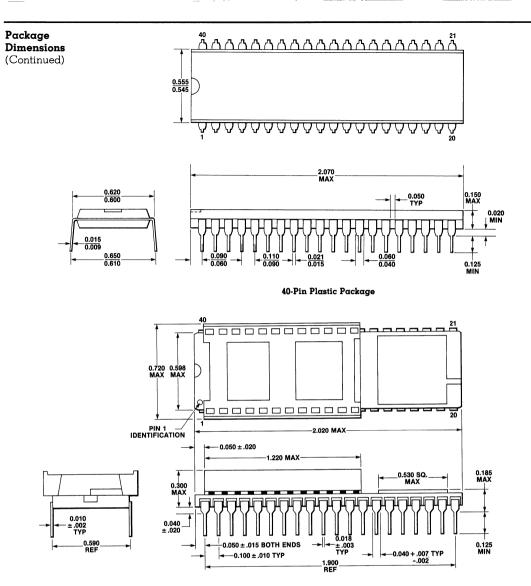

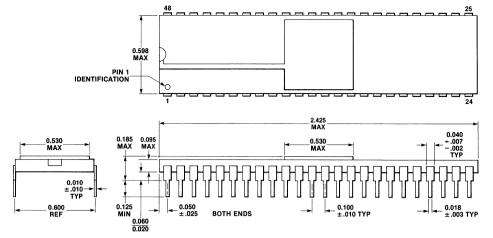

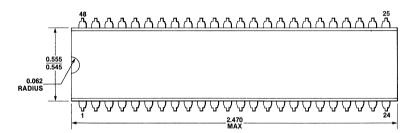

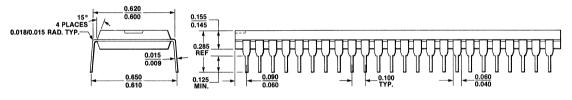

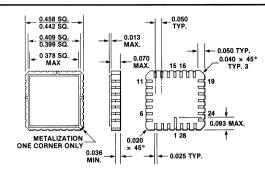

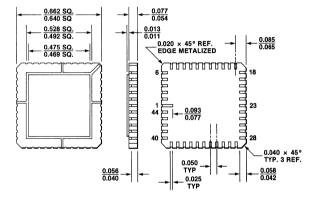

| Package Dimensions<br>Package Summary<br>18-Pin Packages<br>28-Pin Packages<br>40-Pin Packages<br>48-Pin Packages<br>28- and 44-Pin Leadless Packages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 536<br>537<br>538<br>540                                                                |

## Table of Contents (Continued)

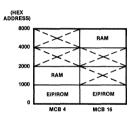

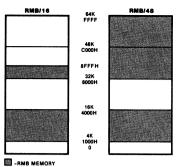

| Z80 Microcomputer Board Products         Z80 MCB Single Board Computer         Z80 RMB RAM Memory Board         Z80 AIO/AIB Analog Input/Output and Analog Input Boards         Z80 IOB Input/Output Board         Z80 Sill Serial Interface Board         Z80 PPB PROM Programming Board         Z80 MDC Memory and Disk Controller Board         Z80 MDC Memory and Disk Controller Board         Z80 Dual Processor Upgrade Package                                                                                                      |                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

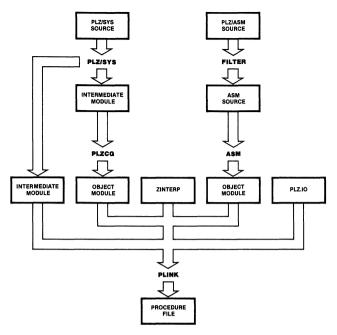

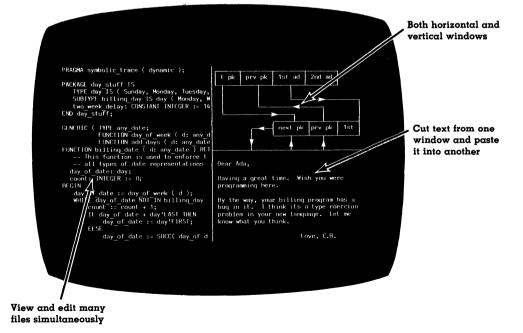

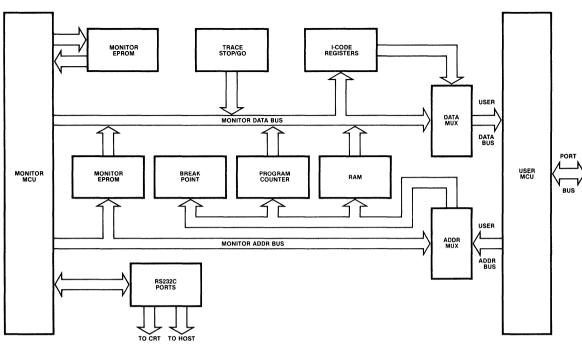

| Zilog Development Products         System 8000 Z-LAB         EMS 8000 Emulator Subsystem         Z-SCAN 8000         Z8000 Development Module         Z8000 Cross-Software Package         Z8000 Software Development Package         Z8000 PLZ/SYS Compiler         ZRTS Zilog Real-Time Software         PDS 8000 Development System         ZDS 1/40 Z80 Development System         Z80 PLZ Compiler         RIO Electric Blackboard         Z8 Development Module         Z8 Development Module         Z8 Software Development Package | 577<br>591<br>593<br>597<br>601<br>603<br>605<br>615<br>619<br>621<br>623 |

## **Functional Index**

## Single-Chip Microcomputers

| Z8601 | Z8 8-Bit with 2K ROM                                                   | 431 |

|-------|------------------------------------------------------------------------|-----|

| Z8602 | Z8 8-Bit with Memory Interface, 64-Pin, 2K External ROM                | 431 |

| Z8603 | Z8 Prototyping Device with EPROM Interface, Protopack, 2K External ROM | 431 |

| Z8611 | Z8 8-Bit, with 4K ROM                                                  | 449 |

| Z8612 | Z8 with Memory Interface, 64-Pin 4K External ROM                       | 449 |

| Z8613 | Z8 Prototyping Device with EPROM Interface, Protopack, 4K External ROM | 449 |

| Z8671 | 8-Bit BASIC/Debug Interpreter                                          | 467 |

| Z8681 | 8-Bit with No On-Chip ROM                                              | 469 |

### 8-Bit Microprocessors

| Z8300 | Z80L Low-Power Central Processing Unit              | 27  |

|-------|-----------------------------------------------------|-----|

| Z8400 | Z80 CPU Central Processing Unit                     |     |

| Z8410 | Z80 DMA Direct Memory Access Controller             | 49  |

|       | Z80 PIO Parallel Input/Output Controller            |     |

| Z8430 | Z80 CTC Counter/Timer Circuit                       | 81  |

| Z8440 | Z80 SIO Dual Channel Serial Input/Output Controller | 93  |

| Z8441 | Z80 SIO Dual Channel Serial Input/Output Controller | 93  |

| Z8442 | Z80 SIO Dual Channel Serial Input/Output Controller | 93  |

| Z8470 | Z80 DART Dual Asynchronous Receiver/Transmitter     | 109 |

| Z8581 | Clock Generator and Controller                      | 403 |

#### 16-Bit Microprocessors

| Advanced Architectural Features of the Z8000 CPU           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

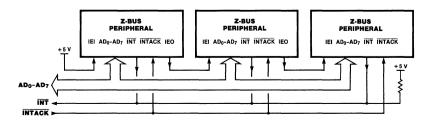

| Zilog Z-BUS Component Interconnect                         | 475                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

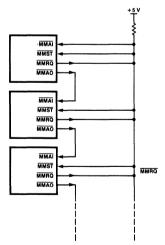

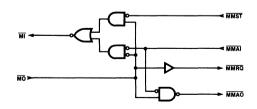

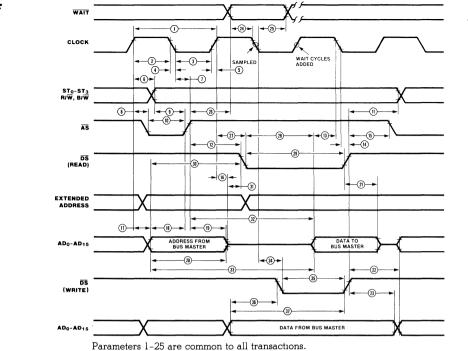

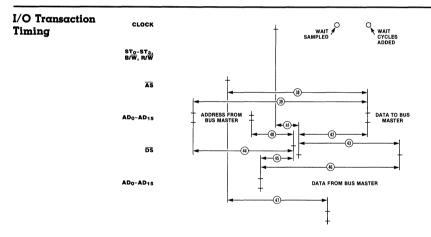

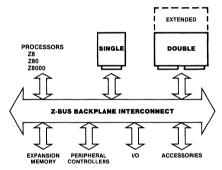

| Z-BUS Backplane Interconnect                               | 493                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Z8000 Z-MMU Memory Management Unit                         | 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

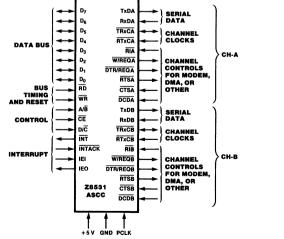

| Z8000 Z-SCC Serial Communications Controller               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

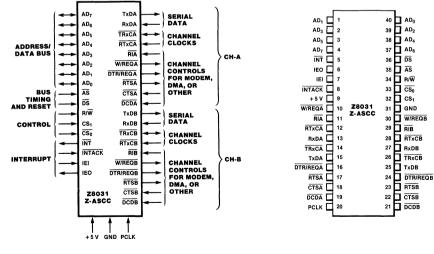

| Z8000 Z-ASCC Asynchronous Serial Communications Controller | 197                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Z8000 Z-CIO Counter/Timer and Parallel I/O Unit            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Z8000 Z-FIO FIFO Input/Output Interface Unit               | 241                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Z8000 Z-BEP Burst Error Processor                          | 281                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Z8000 Z-DCP Data Ciphering Processor                       | 295                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Z8000 Floating Point Package                               | 311                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Z8000 Z-UPC Universal Peripheral Controller                | 313                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Clock Generator and Controller                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                            | Introduction to the Z8010 MMU<br>Zilog Z-BUS Component Interconnect<br>Z-BUS Backplane Interconnect<br>Z8000 CPU Central Processing Unit<br>Z8000 VMPU Virtual Memory Processing Unit<br>Z8000 Z-MMU Memory Management Unit<br>Z8000 DTC Direct Memory Access Transfer Controller<br>Z8000 Z-SCC Serial Communications Controller<br>Z8000 Z-ASCC Asynchronous Serial Communications Controller<br>Z8000 Z-CIO Counter/Timer and Parallel I/O Unit<br>Z8000 Z-FIO FIFO Input/Output Interface Unit<br>Z8000 Z-BEP Burst Error Processor<br>Z8000 Z-DCP Data Ciphering Processor<br>Z8000 Z-UPC Universal Peripheral Controller |

## Microprocessor Peripherals

## Serial Communications Controllers

| Z8030 | Z8000 Z-SCC Serial Communications Controller               | 175 |

|-------|------------------------------------------------------------|-----|

| Z8031 | Z8000 Z-ASCC Asynchronous Serial Communications Controller | 197 |

| Z8440 | Z80 SIO Dual Channel Serial Input/Output Controller        | 93  |

| Z8441 | Z80 SIO Dual Channel Serial Input/Output Controller        | 93  |

| Z8442 | Z80 SIO Dual Channel Serial Input/Output Controller        | 93  |

| Z8470 | Z80 DART Dual Asynchronous Receiver/Transmitter            |     |

| Z8530 | SCC Serial Communications Controller                       |     |

| Z8531 | ASCC Asynchronous Serial Communications Controller         | 359 |

## Functional Index (Continued)

## Microprocessor Peripherals (Continued)

| Parallel I/O and Counter/Timers        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|

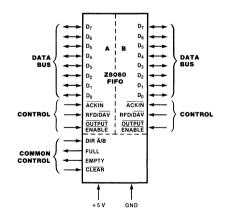

| Z8038<br>Z8060                         | Z8000 Z-CIO Counter/Timer and Parallel I/O Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 241<br>273               |  |

| Universa                               | al Peripheral Controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |  |

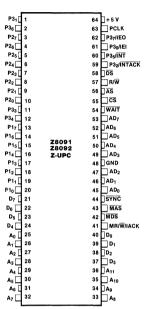

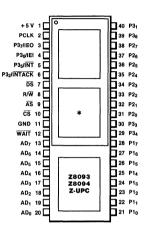

| Z8091/3<br>Z8092/4<br>Z8590<br>Z8591/3 | Z8000 Z-UPC Universal Peripheral Controller         Z8000 Z-UPC External ROM-Based Universal Peripheral Controller         Z8000 Z-UPC External RAM-Based Universal Peripheral Controller         UPC Universal Peripheral Controller         UPC External ROM-Based Universal Peripheral Controller         UPC External RAM-Based Universal Peripheral Controller | 313<br>313<br>407<br>407 |  |

### **Clock Products**

| Z8581 Clock Generator and Controller | 403 |

|--------------------------------------|-----|

|--------------------------------------|-----|

#### **Board Products**

| Dual Processor Upgrade Package for Z80 Systems          | 571 |

|---------------------------------------------------------|-----|

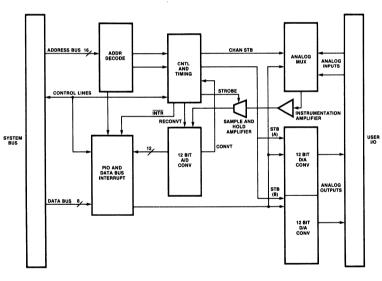

| Z80 AIO/AIB Analog Input/Output and Analog Input Boards |     |

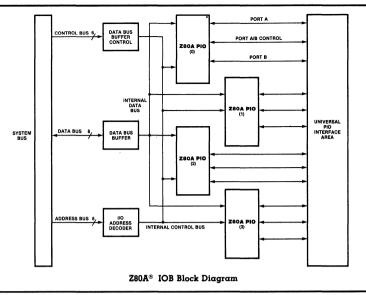

| Z80 IOB Input/Output Board                              | 557 |

| Z80 MCB Single Board Computer                           | 547 |

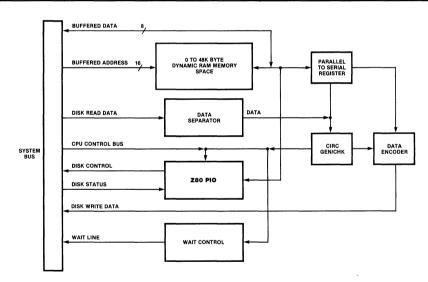

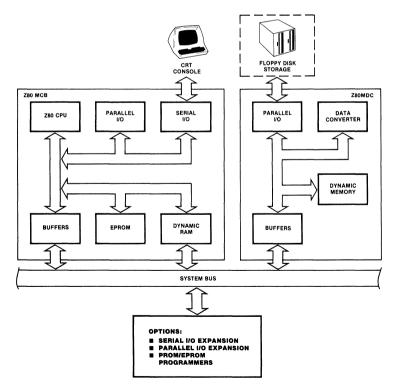

| Z80 MDC Memory and Disk Controller Board                | 567 |

| Z80 PLZ/SYS Compiler for the Z80                        | 619 |

| Z80 PMB PROM Memory Board                               | 565 |

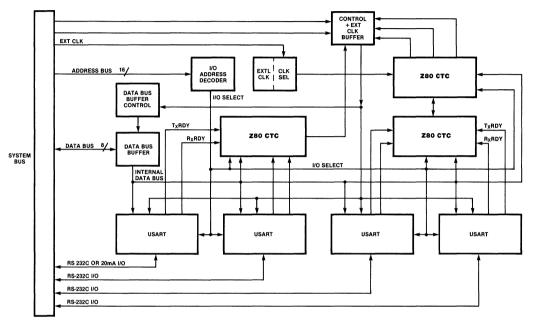

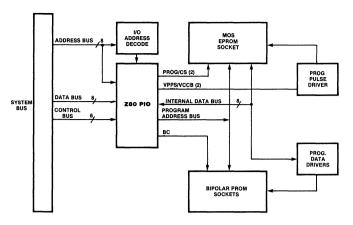

| Z80 PPB PROM Programmer Board                           | 563 |

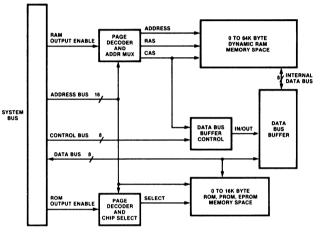

| Z80 RMB RAM Memory Board                                | 551 |

| Z80 SIB Serial Interface Board                          | 559 |

## **Development Products**

| 591 |

|-----|

| 611 |

| 621 |

| 577 |

| 615 |

| 607 |

| 593 |

| 623 |

| 627 |

| 619 |

| 601 |

| 597 |

| 605 |

| 603 |

|     |

## **Part Number Index**

#### Description

| Part Number | Description                                                                              |     |

|-------------|------------------------------------------------------------------------------------------|-----|

| 05-0067-00  | System 8000 Z-LAB Multi-User Development System, Model 20, 50 Hz                         | 577 |

| 05-0069-00  | System 8000 Z-LAB Multi-User Development System, Model 30, 50 Hz                         | 577 |

| 05-0103-00  | Z-SCAN 8000 In-Circuit Emulator                                                          |     |

| 05-0122-00  | EMS 8000 In-Circuit Emulator Subsystem                                                   | 591 |

| 05-6003-XX  | Z80 RMB RAM Memory Board                                                                 |     |

| 05-6006-03  | Z80 IOB Input/Output Board                                                               | 557 |

| 05-6007-01  | Z80 SIB Serial Interface Board                                                           | 559 |

| 05-6009-XX  | Z80 MCB Single Board Computer                                                            | 547 |

| 05-6011-XX  | Z80 MDC Memory and Disk Controller Board                                                 | 567 |

| 05-6013-05  | ZDS 1/40 Z80 In-Circuit Emulator and Development System                                  | 615 |

| 05-6015-01  | Z80 PPB PROM Programmer Board                                                            | 563 |

| 05-6023-01  | Z80 PMB PROM Memory Board                                                                |     |

| 05-6075-01  | Z80 AIO/AIB Analog Input/Output and Analog Input Boards                                  | 553 |

| 05-6101-01  | Z8002 Development Module                                                                 | 597 |

| 05-6102-01  | PDS 8000 Single-User Development System                                                  | 611 |

| 05-6158-01  | Z8 Development Module                                                                    | 623 |

| 05-6168-01  | Z8001 Development Module                                                                 | 597 |

| 05-6219-00  | Dual Processor Upgrade Package for Z80 Systems                                           | 571 |

| 06-0086-01  | Z8000 Cross-Software Package, C Cross-Compiler and Assembler for Z8001 and Z8002,        |     |

|             | DEC 11/70 with UNIX*                                                                     |     |

| 07-3028-00  | RIO Electric Blackboard, CRT Editor for ZDS Systems                                      |     |

| 07-3029-00  | RIO Electric Blackboard, CRT Editor for PDS Systems                                      |     |

| 07-3301-01  | Z80 PLZ/SYS Compiler for use with PDS 8000/05 and PDS 8000/15                            |     |

| 07-3302-01  | Z80 PLZ/SYS Compiler for use with ZDS-1 Series                                           | 605 |

| 07-3306-02  | Z8000 Software Development Package, Cross-Assembler for Z80-Based Hard Disk Systems with |     |

|             | Optional Floppy Drives                                                                   |     |

| 07-3309-01  | Z8000 Software Development Package, Cross-Assembler for PDS 800/5                        |     |

| 07-3310-01  | Z8000 Software Development Package, Cross-Assembler for ZDS-1 Series                     | 603 |

| 07-3361-01  | Z8 Software Development Package, Cross-Assembler for use with PDS 8000/5 and             |     |

|             | PDS 8000/15                                                                              |     |

| 07-3362-01  | Z8 Software Development Package for use with ZDS-1 Series                                |     |

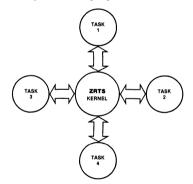

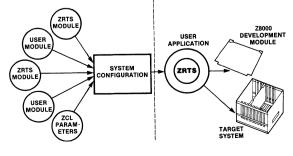

| Z8000       | ZRTS Z8000 Real-Time, Multitasking Software Tools                                        |     |

| Z8001       | 16-Bit, Segmented Central Processing Unit                                                |     |

| Z8002       | 16-Bit, Non-Segmented Central Processing Unit                                            |     |

| Z8010       | Z8001/3 Z-MMU Memory Management Unit                                                     |     |

| Z8015       | Z8000 PMMU Paged Memory Management Unit                                                  |     |

| Z8016       | Z8000 DTC Direct Memory Access Transfer Controller                                       |     |

| Z8030       | Z8000 Z-SCC Serial Communications Controller                                             |     |

| Z8031       | Z8000 Z-ASCC Asynchronous Serial Communications Controller                               | 197 |

## Part Number Index (Continued)

| Part Number    | Description                                                                                                                                                           |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Z8036          | Z8000 Z-CIO Counter/Timer and Parallel I/O Unit                                                                                                                       |

| Z8038          | Z8000 Z-FIO FIFO Input/Output Interface Unit                                                                                                                          |

| Z8060          | Z8000 FIFO Buffer Unit and Z-FIO Expander                                                                                                                             |

| Z8065          | Z8000 Z-BEP Burst Error Processor                                                                                                                                     |

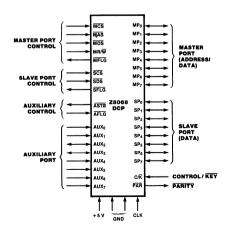

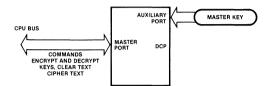

| Z8068          | Z8000 Z-DCP Data Ciphering Processor                                                                                                                                  |

| Z8070          | Z8000 Floating Point Unit                                                                                                                                             |

| Z8090          | Z8000 Z-UPC Universal Peripheral Controller                                                                                                                           |

| Z8091/3        | Z8000 Z-UPC Universal Peripheral Controller, External ROM-Based                                                                                                       |

| Z8092/4        | Z8000 Z-UPC Universal Peripheral Controller, External RAM-Based                                                                                                       |

| Z8300          | Z80L CPU Low-Power Z80 Central Processing Unit                                                                                                                        |

| Z8400          | Z80 CPU Z80 Central Processing Unit                                                                                                                                   |

| Z8410          | Z80 DMA Dual Port, Direct Memory Access Controller                                                                                                                    |

| Z8420          | Z80 PIO Dual Port, Parallel Input/Output Controller                                                                                                                   |

| Z8430          | Z80 CTC Four Channel Counter/Timer Circuit                                                                                                                            |

| Z8440<br>Z8441 | Z80 SIO/0 Dual Channel Synchronous/Asynchronous Serial I/O Controller       93         Z80 SIO/1 Dual Channel Synchronous/Asynchronous Serial I/O Controller       93 |

| Z8441<br>Z8442 | 1                                                                                                                                                                     |

| Z8470          | Z80 SIO/2 Dual Channel Synchronous/Asynchronous Serial I/O Controller       93         Z80 DART Dual Channel Asynchronous Serial I/O Controller       109             |

| Z8530*         | SCC Serial Communications Controller                                                                                                                                  |

| Z8531          | ASCC Asynchronous Serial Communications Controller                                                                                                                    |

| Z8536          | CIO Counter/Timer and Parallel I/O Unit                                                                                                                               |

| Z8581          | Clock Generator and Controller                                                                                                                                        |

| Z8590          | UPC Universal Peripheral Controller                                                                                                                                   |

| Z8591          | UPC Universal Peripheral Controller with External ROM                                                                                                                 |

| Z8592          | UPC Universal Peripheral Controller with External RAM                                                                                                                 |

| Z8593          | UPC Universal Peripheral Controller with External ROM, Protopack                                                                                                      |

| Z8594          | UPC Universal Peripheral Controller with External RAM, Protopack                                                                                                      |

| Z8601          | Z8 8-Bit, Single-Chip Microcomputer with 2K ROM                                                                                                                       |

| Z8602          | Z8 8-Bit Microcomputer with Memory Interface, 64-Pin, 2K External ROM                                                                                                 |

| Z8603          | Z8 Prototyping Device with EPROM Interface, Protopack, 2K External ROM                                                                                                |

| Z8611          | Z8 8-Bit, Single-Chip Microcomputer with 4K ROM                                                                                                                       |

| Z8612          | Z8 8-Bit Microcomputer with Memory Interface, 64-Pin, 4K External ROM                                                                                                 |

| Z8613          | Z8 Prototyping Device with EPROM Interface, Protopack, 4K External ROM                                                                                                |

| Z8671          | Z8 8-Bit, Single-Chip BASIC/Debug Interpreter                                                                                                                         |

| Z8681          | Z8 8-Bit, Single-Chip Microcomputer with No On-Chip ROM                                                                                                               |

\*All 85XX components are compatible with processors other than Zilog's Z8001, Z8002, Z8003, and Z8004. For further information refer to the individual product specifications

## Zilog Z80<sup>®</sup> Family

## Sets the Industry Standard for 8 Bits

#### June 1982

Zilog remains an industry leader, thanks to continuing innovation in microcomputer concepts and integrated design as exemplified in the Z80 Family microcomputer products.

At Zilog, innovation means using proven, sophisticated mainframe and minicomputer concepts and translating them into the latest LSI technologies. Integration means more than designing an evergreater number of functions onto a single chip. Zilog integrates technologies—LSI design enhanced by advances in computer-based system architecture and system design technologies.

Zilog offers microprocessor solutions to computing problems: from components and development systems to OEM board-level products and general-purpose microcomputer systems.

This guide to the Z80 Family of state-of-the-art microprocessors and intelligent peripheral controllers demonstrates Zilog's continued support for the Z80 microprocessor and the other members of the Z80 product family—a family first introduced in 1976 that continues to enjoy growing customer support while family chips are upgraded to newer and ever-higher standards.

The **Z8400 Z80 CPU Central Processing Unit** rapidly established itself as the most sophisticated, most powerful, and most versatile 8-bit microprocessor in the world. It offers many more features and functions than its competitor.

In addition to being source-code compatible with the 8080A microprocessor, the Z80 offers more instructions than the 8080A (158 vs. 78) and numerous other features that simplify hardware requirements and reduce programming effort while increasing throughput. The dual-register set of the Z80 CPU allows high-speed context switching and more efficient interrupt processing. Two index registers give additional memory-addressing flexibility and simplify the task of programming. Interfacing to dynamic memory is simplified by on-chip, programmable refresh logic. Block moves plus string- and bit-manipulation instructions reduce programming effort, program size, and execution time.

Now the **Z8300 Z80L CPU** extends the range of Z80 applications. This low-power version retains all Z80 CPU functions while providing dramatic power savings and increased reliability.

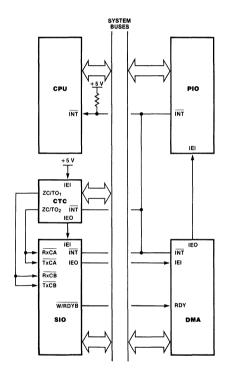

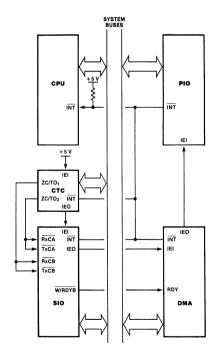

The four traditional functions of a microcomputer system (parallel I/O, serial I/O, counting/timing, and direct memory access) are easily implemented by the Z80 CPU and the following well-proven family of Z80 peripheral devices: Z80 PIO, Z80 SIO, Z80 DART, Z80 CTC, and Z80 DMA.

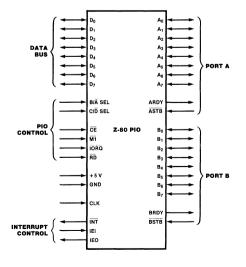

The easily programmed, dualchannel **Z8420 Z80 PIO Parallel Input/Output Controller** offers two 8-bit I/O ports with individual handshake and pattern recognition logic. Both I/O ports operate in either a byte or a bit mode. In addition, this device can be programmed to generate interrupts for various status conditions.

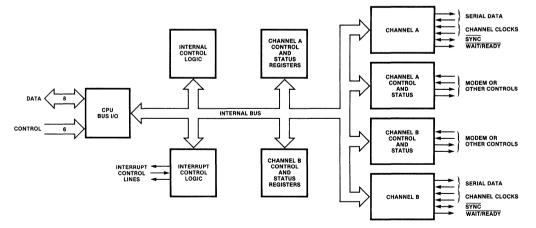

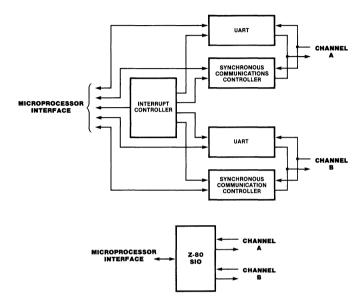

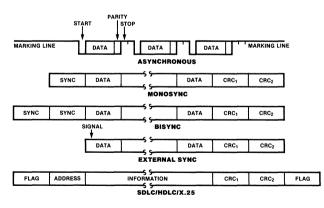

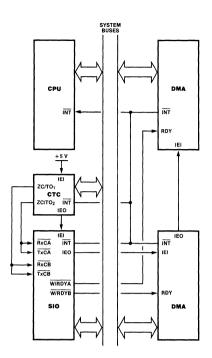

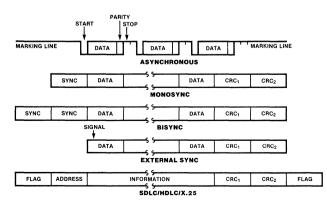

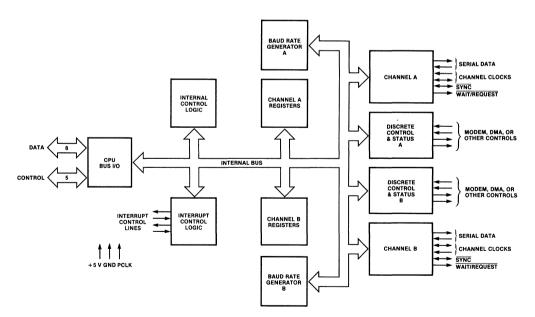

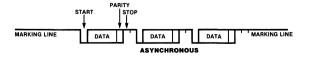

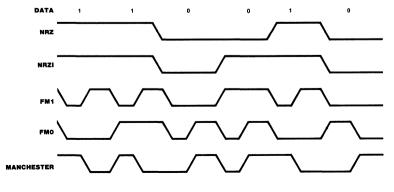

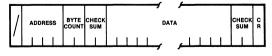

All common data communications protocols, asynchronous as well as synchronous, are remarkably well handled by the **Z8440 Z80 SIO Serial Input/Output Controller**. This dual-channel receiver/transmitter device offers on-chip parity and CRC generation/checking. FIFO buffering and flag- and frame-detection generation logic are also offered.

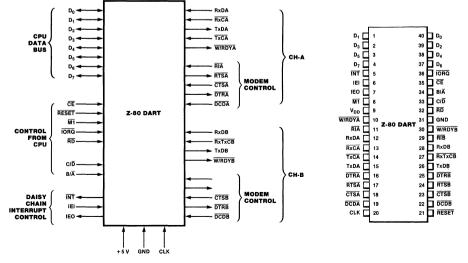

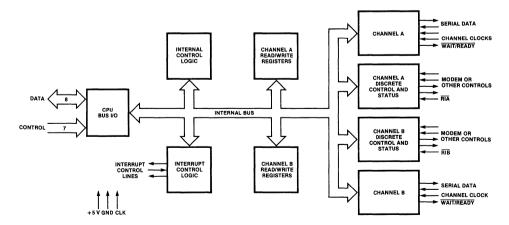

If asynchronous-only applications are required, the costeffective **Z8470 Z80 DART Dual Asynchronous Receiver/Transmitter** can be used in place of the Z80 SIO. The Z80 DART offers all Z80 SIO asynchronous features in two channels.

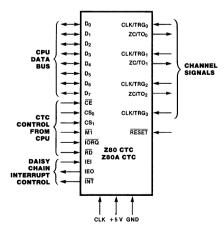

Timing and event-counting functions are the forte of the **Z8430 Z80 CTC Counter/Timer Controller.** The CTC provides four counters, each with individually programmable prescalers. The CTC is a convenient source of programmable clock rates for the SIO.

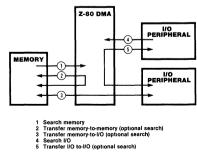

With the **Z8410 Z80 DMA Direct Memory Access Controller**. data can be transferred directly between any two ports (typically, I/O and memory). The DMA transfers, searches, or search/transfers date in Byte-by-Byte, Burst, or Continuous modes. This device can achieve an impressive 2M bits per second data rate in the Search mode.

## Z8400 Z80°CPU Central Processing Unit

## **Product Specification**

Zilog

#### June 1982

- Features The instruction set contains 158 instructions. The 78 instructions of the 8080A are included as a subset; 8080A software compatibility is maintained.

- Six MHz, 4 MHz and 2.5 MHz clocks for the Z80B, Z80A, and Z80 CPU result in rapid instruction execution with consequent high data throughput.

- The extensive instruction set includes string, bit, byte, and word operations. Block searches and block transfers together with indexed and relative addressing result in the most powerful data handling capabilities in the microcomputer industry.

- The Z80 microprocessors and associated family of peripheral controllers are linked by a vectored interrupt system. This system

may be daisy-chained to allow implementation of a priority interrupt scheme. Little, if any, additional logic is required for daisy-chaining.

- Duplicate sets of both general-purpose and flag registers are provided, easing the design and operation of system software through single-context switching, background-foreground programming, and single-level interrupt processing. In addition, two 16-bit index registers facilitate program processing of tables and arrays.

- There are three modes of high speed interrupt processing: 8080 compatible, non-Z80 peripheral device, and Z80 Family peripheral with or without daisy chain.

- On-chip dynamic memory refresh counter.

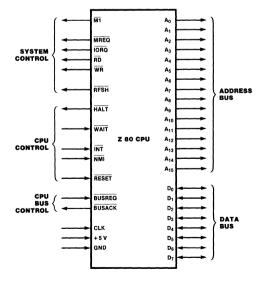

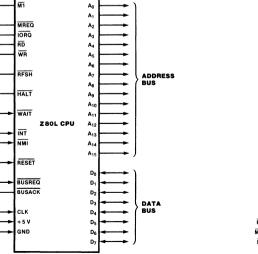

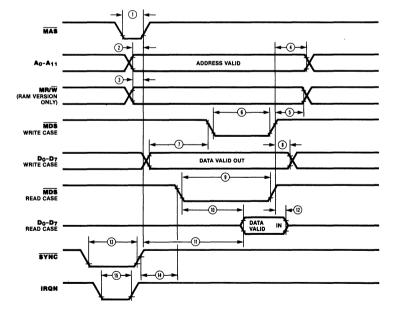

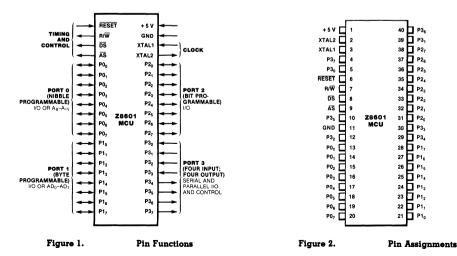

Figure 1. Pin Functions

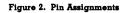

Figure 2. Pin Assignments

#### General Description

The Z80, Z80A, and Z80B CPUs are thirdgeneration single-chip microprocessors with exceptional computational power. They offer higher system throughput and more efficient memory utilization than comparable secondand third-generation microprocessors. The internal registers contain 208 bits of read/write memory that are accessible to the programmer. These registers include two sets of six generalpurpose registers which may be used individually as either 8-bit registers or as 16-bit register pairs. In addition, there are two sets of accumulator and flag registers. A group of "Exchange" instructions makes either set of main or alternate registers accessible to the programmer. The alternate set allows operation in foreground-background mode or it may be

reserved for very fast interrupt response.

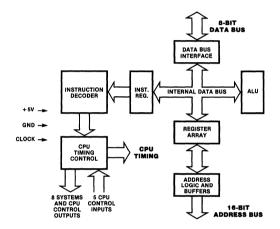

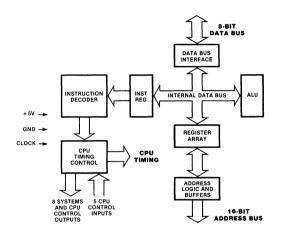

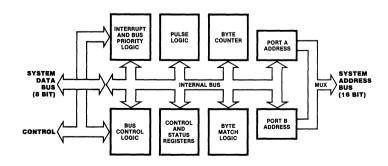

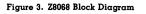

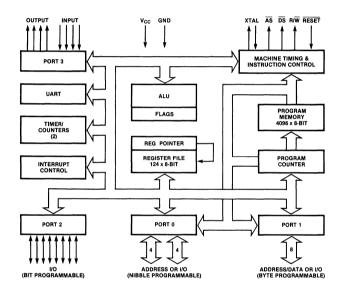

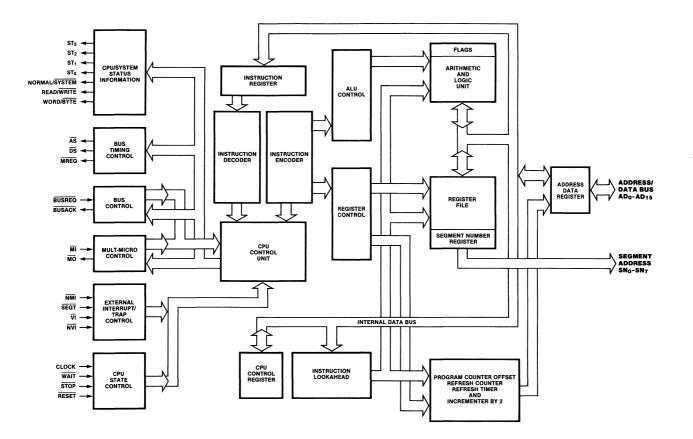

The Z80 also contains a Stack Pointer, Program Counter, two index registers, a Refresh register (counter), and an Interrupt register. The CPU is easy to incorporate into a system since it requires only a single + 5 V power source. All output signals are fully decoded and timed to control standard memory or peripheral circuits, and it is supported by an extensive family of peripheral controllers. The internal block diagram (Figure 3) shows the primary functions of the Z80 processors. Subsequent text provides more detail on the Z80 I/O controller family, registers, instruction set, interrupts and daisy chaining, and CPU timing.

Figure 3. Z80 CPU Block Diagram

| Z80 Micro-<br>processor<br>Family | The Zilog Z80 microprocessor is the central<br>element of a comprehensive microprocessor<br>product family. This family works together in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | each of which has an 8-bit prescaler. Each<br>of the four channels may be configured to<br>operate in either counter or timer mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                                 | <ul> <li>most applications with minimum requirements for additional logic, facilitating the design of efficient and cost-effective microcomputer-based systems.</li> <li>Zilog has designed five components to provide extensive support for the Z80 micro-processor. These are:</li> <li>The PIO (Parallel Input/Output) operates in both data-byte I/O transfer mode (with handshaking) and in bit mode (without handshaking). The PIO may be configured to interface with standard parallel peripheral devices such as printers, tape punches, and keyboards.</li> <li>The CTC (Counter/Timer Circuit) features four programmable 8-bit counter/timers,</li> </ul> | <ul> <li>The DMA (Direct Memory Access) controller provides dual port data transfer operations and the ability to terminate data transfer as a result of a pattern match.</li> <li>The SIO (Serial Input/Output) controller offers two channels. It is capable of operating in a variety of programmable modes for both synchronous and asynchronous communication, including Bi-Sync and SDLC.</li> <li>The DART (Dual Asynchronous Receiver/Transmitter) device provides low cost asynchronous serial communication. It has two channels and a full modem control interface.</li> </ul> |

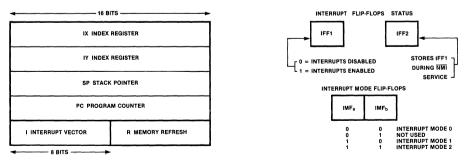

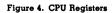

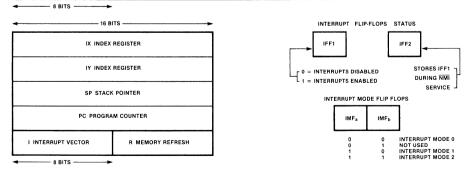

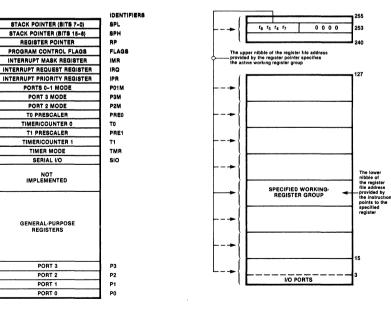

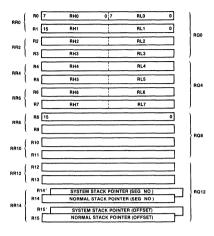

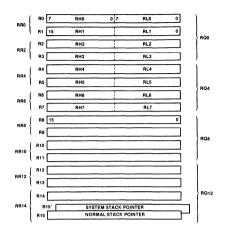

| Z80 CPU<br>Registers              | Figure 4 shows three groups of registers<br>within the Z80 CPU. The first group consists of<br>duplicate sets of 8-bit registers: a principal set<br>and an alternate set (designated by ' [prime],<br>e.g., A'). Both sets consist of the Accumula-<br>tor Register, the Flag Register, and six<br>general-purpose registers. Transfer of data<br>between these duplicate sets of registers is<br>accomplished by use of "Exchange" instruc-<br>tions. The result is faster response to interrupts<br>and easy, efficient implementation of such ver-<br>satile programming techniques as background-                                                                | foreground data processing. The second set of<br>registers consists of six registers with assigned<br>functions. These are the I (Interrupt Register),<br>the R (Refresh Register), the IX and IY (Index<br>Registers), the SP (Stack Pointer), and the PC<br>(Program Counter). The third group consists o<br>two interrupt status flip-flops, plus an addi-<br>tional pair of flip-flops which assists in identi-<br>fying the interrupt mode at any particular<br>time. Table 1 provides further information on<br>these registers.                                                    |

| MAIN | REGISTER | SET |

|------|----------|-----|

|------|----------|-----|

ALTERNATE REGISTER SET

| A ACCUMULATOR     | F FLAG REGISTER   | A' ACCUMULATOR     | F' FLAG REGISTER   |

|-------------------|-------------------|--------------------|--------------------|

| B GENERAL PURPOSE | C GENERAL PURPOSE | B' GENERAL PURPOSE | C' GENERAL PURPOSE |

| D GENERAL PURPOSE | E GENERAL PURPOSE | D' GENERAL PURPOSE | E' GENERAL PURPOSE |

| H GENERAL PURPOSE | L GENERAL PURPOSE | H' GENERAL PURPOSE | L' GENERAL PURPOSE |

| < 8 BITS>         |                   |                    |                    |

| Z80 CPU     | Re                                 | gister             | Size (Bits) | Remarks                                                                                                                                                   |

|-------------|------------------------------------|--------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | A, A'                              | Accumulator        | 8           | Stores an operand or the results of an operation.                                                                                                         |

| (Continued) | F, F'                              | Flags              | 8           | See Instruction Set.                                                                                                                                      |

|             | B, B'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with C.                                                                                                    |

|             | C, C'                              | General Purpose    | 8           | See B, above.                                                                                                                                             |

|             | D, D'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with E.                                                                                                    |

|             | Ε, Ε΄                              | General Purpose    | 8           | See D, above.                                                                                                                                             |

|             | Н, Н'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with L.                                                                                                    |

|             | L, L'                              | General Purpose    | 8           | See H, above.                                                                                                                                             |

|             |                                    |                    |             | Note: The (B,C), (D,E), and (H,L) sets are combined as follows:<br>B — High byte C — Low byte<br>D — High byte E — Low byte<br>H — High byte L — Low byte |

|             | I                                  | Interrupt Register | 8           | Stores upper eight bits of memory address for vectored interrupt processing.                                                                              |

|             | R                                  | Refresh Register   | 8           | Provides user-transparent dynamic memory refresh. Automatically<br>incremented and placed on the address bus during each<br>instruction fetch cycle.      |

|             | IX                                 | Index Register     | 16          | Used for indexed addressing.                                                                                                                              |

|             | IY                                 | Index Register     | 16          | Same as IX, above.                                                                                                                                        |

|             | SP                                 | Stack Pointer      | 16          | Holds address of the top of the stack. See Push or Pop in instruc-<br>tion set.                                                                           |

|             | PC                                 | Program Counter    | 16          | Holds address of next instruction.                                                                                                                        |

|             | IFF <sub>1</sub> -IFF <sub>2</sub> | Interrupt Enable   | Flip-Flops  | Set or reset to indicate interrupt status (see Figure 4).                                                                                                 |

|             | IMFa-IMFb                          | Interrupt Mode     | Flip-Flops  | Reflect Interrupt mode (see Figure 4).                                                                                                                    |

#### Interrupts: General Operation

The CPU accepts two interrupt input signals: NMI and INT. The NMI is a non-maskable interrupt and has the highest priority. INT is a lower priority interrupt and it requires that interrupts be enabled in software in order to operate. INT can be connected to multiple peripheral devices in a wired-OR configuration.

The Z80 has a single response mode for interrupt service for the non-maskable interrupt. The maskable interrupt,  $\overline{INT}$ , has three programmable response modes available. These are:

Mode 0 — compatible with the 8080 microprocessor.

- Mode 1 Peripheral Interrupt service, for use with non-8080/Z80 systems.

- Mode 2 a vectored interrupt scheme, usually daisy-chained, for use with Z80 Family and compatible peripheral devices.

<u>The CPU services interrupts by sampling the</u> <u>NMI and INT signals at the rising edge of the</u> last clock of an instruction. Further interrupt service processing depends upon the type of interrupt that was detected. Details on interrupt responses are shown in the CPU Timing Section.

280® CPU

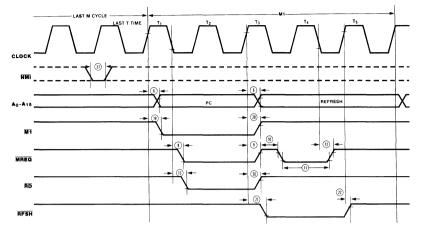

Interrupts: General Operation (Continued) Non-Maskable Interrupt (MMI). The nonmaskable interrupt cannot be disabled by program control and therefore will be accepted at all times by the CPU. MMI is usually reserved for servicing only the highest priority type interrupts, such as that for orderly shutdown after power failure has been detected. <u>After recognition of the NMI signal (providing BUSREQ</u> is not active), the CPU jumps to restart location 0066H. Normally, software starting at this address contains the interrupt service routing.

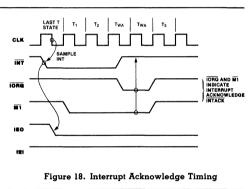

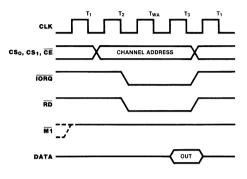

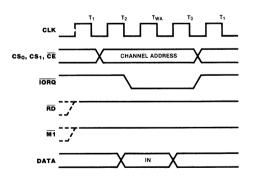

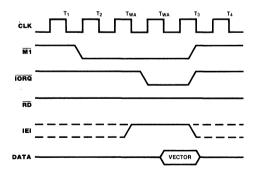

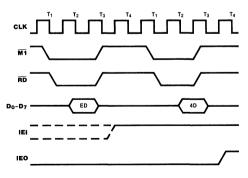

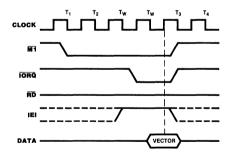

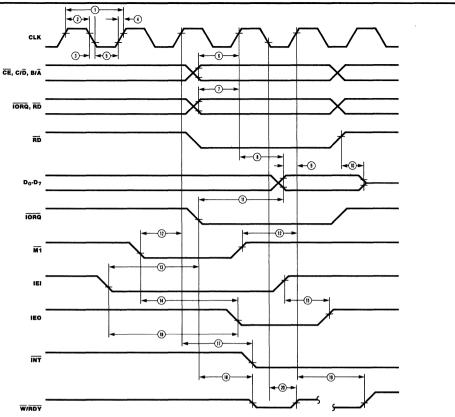

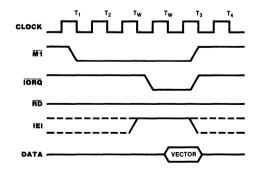

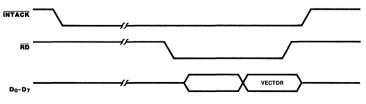

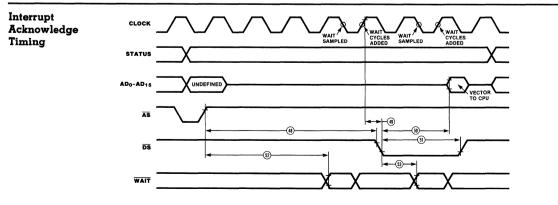

**Maskable Interrupt (ĪNT).** Regardless of the interrupt mode set by the user, the Z80 response to a maskable interrupt input follows a common timing cycle. After the interrupt has been detected by the CPU (provided that interrupts are enabled and BUSREQ is not active) a special interrupt processing cycle begins. This is a special fetch (MI) cycle in which IORQ becomes active rather than MREQ, as in normal MI cycle. In addition, this special MI cycle is automatically extended by two WAIT states, to allow for the time required to acknowledge the interrupt request.

**Mode 0 Interrupt Operation.** This mode is compatible with the 8080 microprocessor interrupt service procedures. The interrupting device places an instruction on the data bus. This is normally a Restart Instruction, which will initiate a call to the selected one of eight restart locations in page zero of memory.

**Mode 1 Interrupt Operation.** Mode 1 operation is very similar to that for the  $\overline{\text{NMI}}$ . The principal difference is that the Mode 1 interrupt has a restart location of 0038H only.

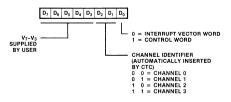

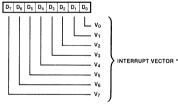

Mode 2 Interrupt Operation. This interrupt mode has been designed to utilize most effectively the capabilities of the Z80 microprocessor and its associated peripheral family. The interrupting peripheral device selects the starting address of the interrupt service routine. It does this by placing an 8-bit vector on the data bus during the interrupt acknowledge cycle. The CPU forms a pointer using this byte as the lower 8-bits and the contents of the I register as the upper 8-bits. This points to an entry in a table of addresses for interrupt service routines. The CPU then jumps to the routine at that address. This flexibility in selecting the interrupt service routine address allows the peripheral device to use several different types of service routines. These routines

may be located at any available location in memory. Since the interrupting device supplies the low-order byte of the 2-byte vector, bit 0 ( $A_0$ ) must be a zero.

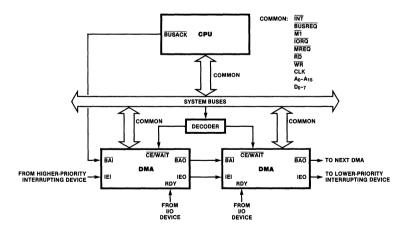

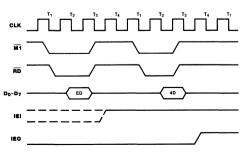

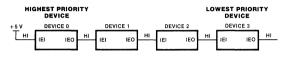

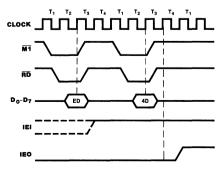

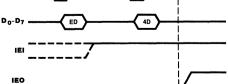

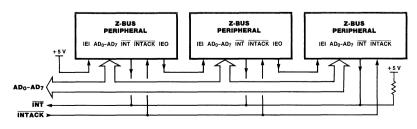

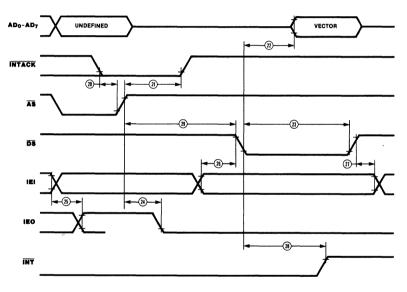

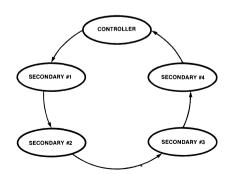

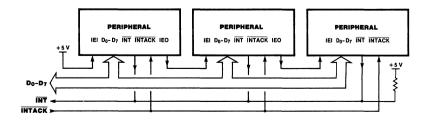

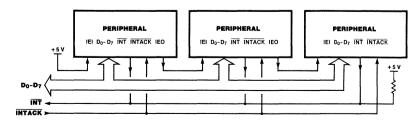

Interrupt Priority (Daisy Chaining and

**Nested Interrupts).** The interrupt priority of each peripheral device is determined by its physical location within a daisy-chain configuration. Each device in the chain has an interrupt enable input line (IEI) and an interrupt enable output line (IEO), which is fed to the next lower priority device. The first device in the daisy chain has its IEI input hardwired to a High level. The first device has highest priority, while each succeeding device has a corresponding lower priority. This arrangement permits the CPU to select the highest priority interrupt from several simultaneously interrupting peripherals.

The interrupting device disables its IEO line to the next lower priority peripheral until it has been serviced. After servicing, its IEO line is raised, allowing lower priority peripherals to demand interrupt servicing.

The Z80 CPU will nest (queue) any pending interrupts or interrupts received while a selected peripheral is being serviced.

**Interrupt Enable/Disable Operation.** Two flip-flops, IFF<sub>1</sub> and IFF<sub>2</sub>, referred to in the register description are used to signal the CPU interrupt status. Operation of the two flip-flops is described in Table 2. For more details, refer to the Z80 CPU Technical Manual and Z80 Assembly Language Manual.

| Action                           | IFF1             | IFF <sub>2</sub> | Comments                                                                              |

|----------------------------------|------------------|------------------|---------------------------------------------------------------------------------------|

| CPU Reset                        | 0                | 0                | Maskable interrupt INT disabled                                                       |

| DI instruction<br>execution      | 0                | 0                | Maskable interrupt<br>INT disabled                                                    |

| EI instruction<br>execution      | 1                | 1                | Maskable interrupt<br>INT enabled                                                     |

| LD A, I instruction<br>execution | •                | •                | $IFF_2 \rightarrow Parity flag$                                                       |

| LD A,R instruction<br>execution  | •                | •                | $IFF_2 \rightarrow Parity flag$                                                       |

| Accept NMI                       | 0                | IFF1             | IFF <sub>1</sub> → IFF <sub>2</sub><br>(Maskable inter-<br>rupt INT disabled)         |

| RETN instruction<br>execution    | IFF <sub>2</sub> | •                | IFF <sub>2</sub> → IFF <sub>1</sub> at<br>completion of an<br>NMI service<br>routine. |

Table 2. State of Flip-Flops

10

| Instruction |  |

|-------------|--|

| Set         |  |

The Z80 microprocessor has one of the most powerful and versatile instruction sets available in any 8-bit microprocessor. It includes such unique operations as a block move for fast, efficient data transfers within memory or between memory and I/O. It also allows operations on any bit in any location in memory.

The following is a summary of the Z80 instruction set and shows the assembly language mnemonic, the operation, the flag status, and gives comments on each instruction. The Z80 CPU Technical Manual (03-0029-01) and Assembly Language Programming Manual (03-0002-01) contain significantly more details for programming use.

The instructions are divided into the following categories:

- □ 8-bit loads

- □ 16-bit loads

- Exchanges, block transfers, and searches

- □ 8-bit arithmetic and logic operations

- □ General-purpose arithmetic and CPU control

- □ 16-bit arithmetic operations

- □ Rotates and shifts

- □ Bit set, reset, and test operations

- 🗆 Jumps

- □ Calls, returns, and restarts

- □ Input and output operations

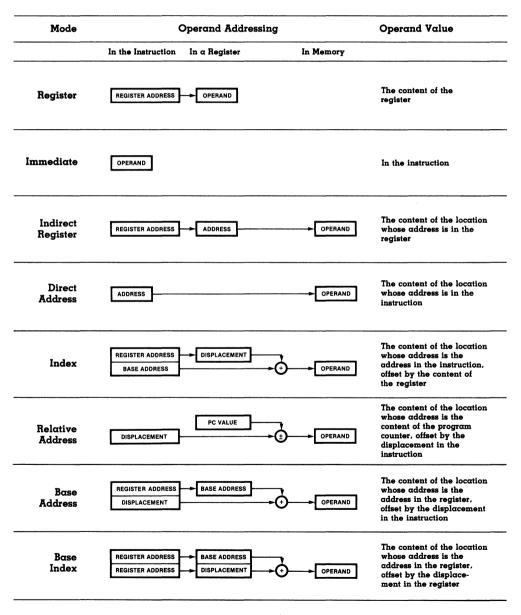

A variety of addressing modes are implemented to permit efficient and fast data transfer between various registers, memory locations, and input/output devices. These addressing modes include:

- □ Immediate

- □ Immediate extended

- □ Modified page zero

- Relative

- □ Extended

- □ Indexed

- □ Register

- Register indirect

- Implied

- 🗆 Bit

| 8-Bit<br>Load | Mnemonic                               | Symbolic<br>Operation                                             | s | z          |             | Flc<br>H | ıgs    | P/V | N | с   | Opcode<br>76 543 210                                                                                                    | Hex            |             | No.of M<br>Cycles |              | Comments                            |

|---------------|----------------------------------------|-------------------------------------------------------------------|---|------------|-------------|----------|--------|-----|---|-----|-------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------------------|--------------|-------------------------------------|

|               | LD r, r'<br>LD r, n                    | $r \leftarrow r'$<br>$r \leftarrow n$                             |   | :          | X<br>X      | :        | X<br>X | :   | : | :   | 01 r r'<br>00 r 110<br>← n →                                                                                            |                | 1<br>2      | 1<br>2            | 4<br>7       | <u>r, r' Reg.</u><br>000 B<br>001 C |

|               | LD r, (HL)<br>LD r, (I <b>X</b> + d)   | $r \leftarrow (HL)$<br>$r \leftarrow (IX + d)$                    | : | :          | X<br>X      | :        | X<br>X | :   | : | :   | $\begin{array}{c} - & n \rightarrow \\ 01 & r & 110 \\ 11 & 011 & 101 \\ 01 & r & 101 \end{array}$                      | DD             | 1<br>3      | 2<br>5            | 7<br>19      | 010 D<br>011 E<br>100 H             |

|               | LD r, (IY + d)                         | $r \leftarrow (IY + d)$                                           | • | •          | x           | •        | x      | •   | • | •   | ← d →<br>11 111 101<br>01 r 110                                                                                         | FD             | 3           | 5                 | 19           | 101 L<br>111 A                      |

|               | LD (HL), r<br>LD (I <b>X</b> +d), r    | $(HL) \leftarrow r$<br>$(IX + d) \leftarrow r$                    | : | :          | X<br>X      | :        | X<br>X | :   | : | :   | ← d →<br>01 110 r<br>11 011 101<br>01 110 r                                                                             | DD             | 1<br>3      | 2<br>5            | 7<br>19      |                                     |

|               | LD (IY+d), r                           | (IY + d) - r                                                      | • | •          | x           | •        | х      | •   | • | •   | + d →<br>11 111 101<br>01 110 r                                                                                         | FD             | 3           | 5                 | 19           |                                     |

|               | LD (HL), n                             | (HL) - n                                                          | • | •          | Х           | •        | х      | •   | • | •   | - d -<br>00 110 110                                                                                                     | 36             | 2           | 3                 | 10           |                                     |

|               | LD (IX + d), n                         | $(IX + d) \leftarrow n$                                           | • | •          | х           | •        | х      | •   | • | •   | → n →<br>11 011 101<br>00 110 110<br>→ d →                                                                              | DD<br>36       | 4           | 5                 | 19           |                                     |

| :             | LD (I <b>Y</b> + d), n                 | (IY + d) - n                                                      | • | •          | x           | •        | x      | •   | • | • ` | ← n →<br>11 111 101<br>00 110 110<br>← d →                                                                              |                | 4           | 5                 | 19           |                                     |

|               | LD A, (BC)<br>LD A, (DE)<br>LD A, (nn) | $A \leftarrow (BC)$<br>$A \leftarrow (DE)$<br>$A \leftarrow (nn)$ | : | :          | X<br>X<br>X | •        | Х      | •   | : | •   | 00 011 010<br>00 111 010                                                                                                | 0A<br>1A<br>3A | 1<br>1<br>3 | 2<br>2<br>4       | 7<br>7<br>13 |                                     |

|               | LD (BC), <b>A</b><br>LD (DE), <b>A</b> | (BC) - A<br>(DE) - A                                              | • | •          | X<br>X      | •        | X<br>X | •   | • | :   | $\begin{array}{c} \leftarrow n \rightarrow \\ \leftarrow n \rightarrow \\ 00 \ 000 \ 010 \\ 00 \ 010 \ 010 \end{array}$ | 02<br>12       | 1           | 2<br>2            | 7<br>7       |                                     |

|               | LD (DE), A<br>LD (nn), A               | $(DE) \leftarrow A$<br>$(nn) \leftarrow A$                        | : |            | x           | •        |        | :   | : |     | $\begin{array}{c} 00 & 010 & 010 \\ 00 & 110 & 010 \\ \leftarrow n \rightarrow \\ \leftarrow n \rightarrow \end{array}$ |                | 3           | 4                 | 13           |                                     |

| :             | LD A, I                                | A - I                                                             | 1 | 1          | X           | 0        | X      | IFF | 0 | •   | 11 101 101<br>01 010 111                                                                                                | ED<br>57       | 2           | 2                 | 9            |                                     |

| :             | LD Å, R                                | A - R                                                             | : | ŧ          | X           | 0        | x      | IFF | 0 | •   | 11 101 101<br>01 011 111                                                                                                | ED<br>5F       | 2           | 2                 | 9            |                                     |

| :             | LD I, <b>A</b>                         | A I                                                               | • | •          | X           | •        | X      | •   | • | •   | 11 101 101                                                                                                              | ED             | 2           | 2                 | 9            |                                     |

| 1             | LD R, A                                | R - A                                                             | • | <b>'</b> • | x           | •        | X      | •   | • | •   |                                                                                                                         | 47<br>ED<br>4F | 2           | 2                 | 9            |                                     |

NOTES r, r' means any of the registers A, B, C, D, E, H, L IFF the content of the interrupt enable flip-flop, (IFF) is copied into the P/V flag

For an explanation of flag notation and symbols for

mnemonic tables, see Symbolic Notation section following tables

| -Bit Load<br>oup | Mnemonic               | Symbolic<br>Operation                                                                                                                                | S        | z    |        | F<br>H | ags    | P/V     | N      | с      | Opcode<br>76 543 210 Hex                                                                                                     | No.of<br>Bytes | No.of M<br>Cycles |         |                 | Comments         |

|------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|--------|--------|--------|---------|--------|--------|------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|---------|-----------------|------------------|

|                  | LD dd, nn              | dd - nn                                                                                                                                              | •        | •    | X      | ٠      | x      | •       | •      | •      | 00 dd0 001<br>← n →                                                                                                          | 3              | 3                 | 10      | <u>dd</u><br>00 | Pair<br>BC       |

|                  | LD IX, nn              | IX — nn                                                                                                                                              | •        | •    | x      | •      | X      | •       | •      | •      | $n \rightarrow 11 011 101 DD$<br>00 100 001 21<br>$n \rightarrow 100 001 21$                                                 | 4              | 4                 | 14      | 01<br>10<br>11  | DE<br>HL<br>SP   |

|                  | LD IY, nn              | IY - nn                                                                                                                                              | •        | •    | x      | •      | X      | •       | •      | •      | $n \rightarrow n$<br>11 111 101 FD<br>00 100 001 21<br>$n \rightarrow n$                                                     | 4              | 4                 | 14      |                 |                  |

|                  | LD HL, (nn)            | $H \leftarrow (nn+1)$<br>L $\leftarrow (nn)$                                                                                                         | •        | •    | x      | •      | x      | •       | •      | •      | 00 101 010 2A                                                                                                                | 3              | 5                 | 16      |                 |                  |