# SONY

# **CXA1645P/M**

#### **RGB** Encoder

#### **Description**

The CXA1645P/M is an encoder IC that converts analog RGB signals to a composite video signal. This IC has various pulse generators necessary for encoding. Composite video outputs and Y/C outputs for the S terminal are obtained by inputting composite sync, subcarrier and analog RGB signals.

It is best suited to image processing of personal computers and video games.

#### **Features**

- Single 5V power supply

- · Compatible with both NTSC and PAL systems

- Built-in 75 drivers (RGB output, composite video output, Y output, C output)

- Both sine wave and pulse can be input as a subcarrier

- Built-in band pass filter for the C signal and delay line for the Y signal

- Built-in R-Y and B-Y modulator circuits

- Built-in PAL alternate circuit

- · Burst flag generator circuit

- · Half H killer circuit

# 24 pin DIP (Plastic) 24 pin SOP (Plastic)

#### **Applications**

Image processing of video games and personal computers

#### Structure

Bipolar silicon monolithic IC

#### **Absolute Maximum Ratings**

| <ul> <li>Supply voltage</li> </ul>        | Vcc   | 14            | V  |

|-------------------------------------------|-------|---------------|----|

| <ul> <li>Operating temperature</li> </ul> | Topr  | -20 to +75    | °C |

| <ul> <li>Storage temperature</li> </ul>   | Tstg  | -65 to +150   | °C |

| <ul> <li>Allowable power</li> </ul>       | $P_D$ | CXA1645P 1250 | mW |

| dissipation                               |       | CXA1645M 780  | mW |

#### **Recommended Operating Condition**

Supply voltage  $Vcc1, 2 5.0 \pm 0.25$  V

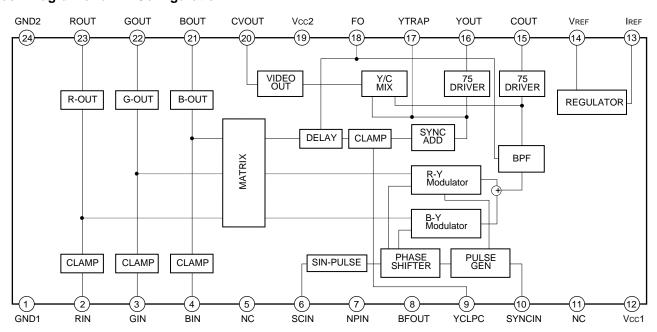

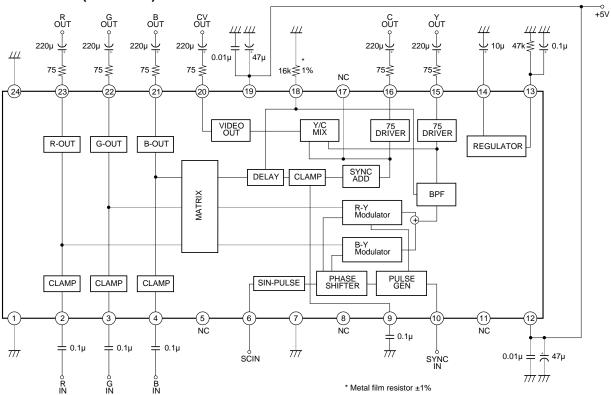

#### **Block Diagram and Pin Configuration**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

# **Pin Description**

# \*Externally applied voltage

| Pin<br>No. | Symbol            | Pin Voltage                            | Equivalent Circuit                | Description                                                                                                                                                        |

|------------|-------------------|----------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | GND1              | 0V*                                    |                                   | Ground for all circuits other than RGB, composite video and Y/C output circuits. The leads to GND2 should be as short and wide as possible.                        |

| 2 3 4      | RIN<br>GIN<br>BIN | Black level<br>when<br>clamped<br>2.0V | 2<br>3<br>4<br>Vcc1               | Analog RGB signal inputs. Input 100%, =1Vp-p (max.). To minimize clamp error, input at as low impedance as possible.  ICLP turns ON only in the burst flag period. |

| 5          | NC                |                                        |                                   | NO CONNECTION                                                                                                                                                      |

| 6          | SCIN              | _                                      | 20P 20k<br>129 20k<br>100<br>GND1 | Subcarrier input. Input 0.4 to 0.5 Vp-p sine wave or pulse. Refer to Notes on Operation, Nos. 3 and 5.                                                             |

| 7          | NPIN              | 1.7V                                   | 7 W 68k 68k 68k GND1              | Pin for switching between NTSC and PAL modes NTSC: Vcc, PAL: GND                                                                                                   |

| 8          | BFOUT             | H : 3.6V<br>L : 3.2V                   | 8 W 25 25                         | BF pulse monitoring output. Incapable of driving a $75\Omega$ load.                                                                                                |

| Pin<br>No. | Symbol     | Pin Voltage | Equivalent Circuit             | Description                                                                                                                        |

|------------|------------|-------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 9          | YCLPC      | 2.5V        | 9<br>129<br>5µ<br>1.6V<br>GND1 | Pin to determine the Y signal clamp time constant. Connect to GND via a 0.1µF capacitor.                                           |

| 10         | SYNC<br>IN | 2.2V        | Vcc1  40k  40k  2.2V  GND1     | Composite sync signal input. Input TTL-level voltages. L ( 0.8V): SYNC period H ( 2.0V)                                            |

| 12         | Vcc1       | 5.0V*       |                                | Power supply for all circuits other than RGB, composite video and Y/C output circuits. Refer to Notes on Operation. Nos. 4 and 10. |

| 13         | IREF       | 2.0V        | Vcc1  13  50  GND1             | Pin to determine the internal reference current. Connect to GND via a $47 \text{k}\Omega$ resistor.                                |

| 14         | VREF       | 4.0V        | Vcc1                           | Internal reference voltage. Connect a decoupling capacitor of approximately 10µF. Refer to Notes on Operation, Nos. 4 and 7.       |

| Pin<br>No. | Symbol | Pin Voltage         | Equivalent Circuit                            | Description                                                                                                                                                                                                                                                                                                                                                                          |

|------------|--------|---------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15         | COUT   | 2.2V                | Vcc2<br>Vcc1<br>600μ<br>15<br>20k × 5<br>GND2 | Chroma signal output. Capable of driving a $75\Omega$ load. Refer to Notes on Operation, Nos. 6 and 9.                                                                                                                                                                                                                                                                               |

| 16         | YOUT   | Black level<br>1.3V | Vcc2<br>Vcc1<br>600μ<br>20k<br>800μ<br>GND2   | Y signal output. Capable of driving a 75 load.  Refer to Notes on Operation, Nos. 6 and 9.                                                                                                                                                                                                                                                                                           |

| 17         | YTRAP  | Black level<br>1.6V | 8.5k 8.5k 0.5P GND1 Input resistance 1.5k     | Pin for reducing cross color caused by the subcarrier frequency component of the Y signal. When the CVOUT pin is in use, connect a capacitor or a capacitor and an inductor in series between YTRAP and GND. Decide capacitance and inductance, giving consideration to cross color and the required resolution.  No influence on the YOUT pin.  Refer to Notes on Operation, No. 8. |

| 18         | FO     | 2.0V                | Vcc1                                          | Internal filter fo adjustment pin. Connect to GND via the following resistor according to the NTSC or PAL mode. NTSC: 20kΩ (±1%) PAL : 16kΩ (±1%)                                                                                                                                                                                                                                    |

| Pin<br>No.     | Symbol               | Pin Voltage         | Equivalent Circuit                         | Description                                                                                                                                                                                    |

|----------------|----------------------|---------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19             | Vcc2                 | 5.0V*               |                                            | Power supply for RGB, composite video and Y/C output circuits. Decouple this pin with a large capacitor of 10µF or above as a high current flows.  Refer to Notes on Operation, Nos. 4 and 10. |

|                |                      |                     |                                            | record to ractes on operation, racs. 4 and 10.                                                                                                                                                 |

| 20             | CVOUT                | Black level<br>1.2V | Vcc2<br>Vcc1<br>600μ<br>20k<br>20k<br>6ND2 | Composite video signal output. Capable of driving a $75\Omega$ load. Refer to Notes on Operation, Nos. 6 and 9.                                                                                |

| 21<br>22<br>23 | BOUT<br>GOUT<br>ROUT | Black level<br>1.7V | 21 Vcc2 Vcc1 22 Vcc1 23 200µ GND1 GND2     | Analog RGB signal outputs. Capable of driving a 75Ω load.  Refer to Notes on Operation, Nos. 6 and 9.                                                                                          |

| 24             | GND2                 | 0V*                 |                                            | Ground for RGB, composite video and Y/C output circuits. The leads to GND1 should be as short and wide as possible.                                                                            |

### **Electrical Characteristics** (Ta = +25°C, Vcc = 5V, See the Electrical Characteristics Measurement Circuit.)

|                                      |            | S1                | S2   | S3   | S4         | S5   |                          |                                                                                                           |       |      |       |      |  |

|--------------------------------------|------------|-------------------|------|------|------------|------|--------------------------|-----------------------------------------------------------------------------------------------------------|-------|------|-------|------|--|

| Item                                 | Symbol     | RIN<br>GIN<br>BIN | SCIN | NPIN | SYNC<br>IN | FO   | Measure<br>ment<br>Point | Measurement<br>Conditions                                                                                 | Min.  | Тур. | Max.  | Unit |  |

| Current consumption 1                | Icc1       | 2V                | SG4  | 5V   | SG5        | 20k  | Icc1                     | No input signal,<br>SG5: CSYNC<br>TTL level,<br>SG4: SIN wave                                             |       | 31   |       | mA   |  |

| Current consumption 2                | Icc2       | _,                |      |      |            | 2011 | lcc2                     | 3.58MHz<br>0.5Vp-p<br>Fig. 1                                                                              |       | 12   |       | mA   |  |

| (R, G, BOUT)                         |            |                   | •    |      |            |      |                          |                                                                                                           |       |      |       |      |  |

|                                      | Vo (R)     | SG1               |      |      |            |      | D                        | SG1 to SG3:<br>DC direct<br>coupling 2.5Vpc,                                                              |       |      |       |      |  |

| RGB output voltage                   | Vo (G)     | SG2               |      |      | 2V         |      | E                        | 1.0Vp-p<br>f=200kHz<br>Pin 9=Clamp                                                                        | 0.64  | 0.71 | 0.78  | Vp-p |  |

|                                      | Vo (B)     | SG3               |      |      |            |      | F                        | voltage Fig. 2                                                                                            |       |      |       |      |  |

| DOD 1 1                              | fc (R)     | SG1               |      |      |            |      | D                        | SG1 to SG3:<br>DC direct<br>coupling 2.5Vpc,                                                              |       |      |       |      |  |

| RGB output frequency characteristics | fc (G)     | SG2               |      |      | 2V         |      | Е                        | 1.0Vp-p<br>f=200kHz/5MHz<br>Pin 9=Clamp                                                                   | -3.0  |      |       | dB   |  |

|                                      | fc (B)     | SG3               |      |      |            |      | F                        | voltage Fig. 3                                                                                            |       |      |       |      |  |

| (YOUT & CVOUT)                       |            |                   |      |      |            |      |                          |                                                                                                           |       |      |       |      |  |

| Output sync level                    | Vo (YS1/2) |                   |      |      |            |      |                          | SG1 to SG3:                                                                                               | 0.26  | 0.29 | 0.33  | Vp-p |  |

| R100%: Y level                       | Vo (YR1/2) | SG1               |      |      |            |      |                          | 100% color bar input,                                                                                     | 0.17  | 0.21 | 0.26  | V    |  |

| G100%: Y level                       | Vo (YG1/2) | to                | 0V   | 5V   | SG5        | 20k  |                          | 1.0Vp-p (Max.)                                                                                            | 0.35  | 0.42 | 0.49  | V    |  |

| B100%: Y level                       | Vo (YB1/2) | SG3               |      |      |            |      |                          | SG5: CSYNC<br>TTL level                                                                                   | 0.065 | 0.08 | 0.095 | V    |  |

| White 100%: Y level                  | Vo (YW1/2) |                   |      |      |            |      | B/C                      | Fig. 4                                                                                                    | 0.6   | 0.71 | 0.82  | V    |  |

| Output frequency characteristics     | fc (Y1/2)  | SG1<br>to<br>SG3  | 0V   | 5V   | 2V         | 20k  |                          | SG1 to SG3:<br>DC direct<br>coupling 2.5VDC,<br>1.0Vp-p<br>f=200kHz/5MHz<br>Pin 9=Clamp voltage<br>Fig. 3 | -3.0  |      |       | dB   |  |

<sup>\*</sup> Clamp voltage: voltage appearing at Pin 9 when CSYNC is input.

|                          |                        | S1                | S2   | S3   | S4   | S5  |                          |                                                                                                               |      |      |      |       |

|--------------------------|------------------------|-------------------|------|------|------|-----|--------------------------|---------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Item                     | Symbol                 | RIN<br>GIN<br>BIN | SCIN | NPIN | SYNC | FO  | Measure<br>ment<br>Point | Measurement<br>Conditions                                                                                     | Min. | Тур. | Max. | Unit  |

| (COUT & CVOUT)           |                        | •                 | •    |      | •    |     | •                        |                                                                                                               |      | •    | •    | •     |

| Burst level              | Vo (BN1/2)             |                   |      |      |      |     |                          |                                                                                                               | 0.2  | 0.25 | 0.3  | Vp-p  |

| R chroma ratio           | R/BN1/2                |                   |      |      |      |     |                          | SG1 to SG3:                                                                                                   | 2.84 | 3.16 | 3.48 |       |

| R phase                  | θR1/2                  |                   |      |      |      |     |                          | 100% color bar input,                                                                                         | 94   | 104  | 114  | deg   |

| G chroma ratio           | G/BN1/2                | SG1               |      |      |      |     |                          | 1.0Vp-p (Max.)<br>SG4: SIN wave,                                                                              | 2.65 | 2.95 | 3.25 |       |

| G phase                  | θG1/2                  | to                | SG4  | 5V   | SG5  | 20k |                          | 3.58MHz<br>0.5Vp-p                                                                                            | 231  | 241  | 251  | deg   |

| B chroma ratio           | B/BN1/2                | SG3               |      |      |      |     |                          | SG5: CSYNC<br>TTL level<br>Fig. 5                                                                             | 2.01 | 2.24 | 2.47 |       |

| B phase                  | θΒ1/2                  | 1                 |      |      |      |     |                          |                                                                                                               | 337  | 347  | 357  | deg   |

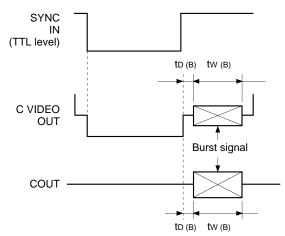

| Burst width              | <b>t</b> w (B) 1/2     |                   |      |      |      |     |                          |                                                                                                               | 2.5  | 2.75 | 3.2  | μs    |

| Burst position           | t <sub>D</sub> (B) 1/2 |                   |      |      |      |     |                          |                                                                                                               | 0.4  | 0.6  | 0.75 | μs    |

| Carrier leak             | VL1/2                  | SG1<br>to<br>SG3  | SG4  | 5V   | SG5  | 20k | A/C                      | SG1 to SG3: No signal, SG4: SIN wave, 3.58MHz 0.5Vp-p SG5: CSYNC TTL level 3.58MHz component measured. Fig. 6 |      |      | 20   | mVp-p |

| PAL burst<br>level ratio | K (BP1/2)              | 004               |      |      |      |     |                          | SG1 to SG3:<br>No signal,<br>SG4: SIN wave,                                                                   | 0.9  | 1.0  | 1.1  |       |

| PAL burst phase          | θPAL1/2                | SG1<br>to<br>SG3  | SG4  | GND  | SG5  | 16k |                          | 4.43MHz<br>0.5Vp-p<br>SG5: CSYNC                                                                              | 125  | 135  | 145  | deg   |

| TAL DUIST PHASE          | θPAL1/2                |                   |      |      |      |     |                          | TTL level Fig. 6                                                                                              | 215  | 225  | 235  | ueg   |

$<sup>^{\</sup>star}$  Clamp voltage: voltage appearing at Pin 9 when CSYNC is input.

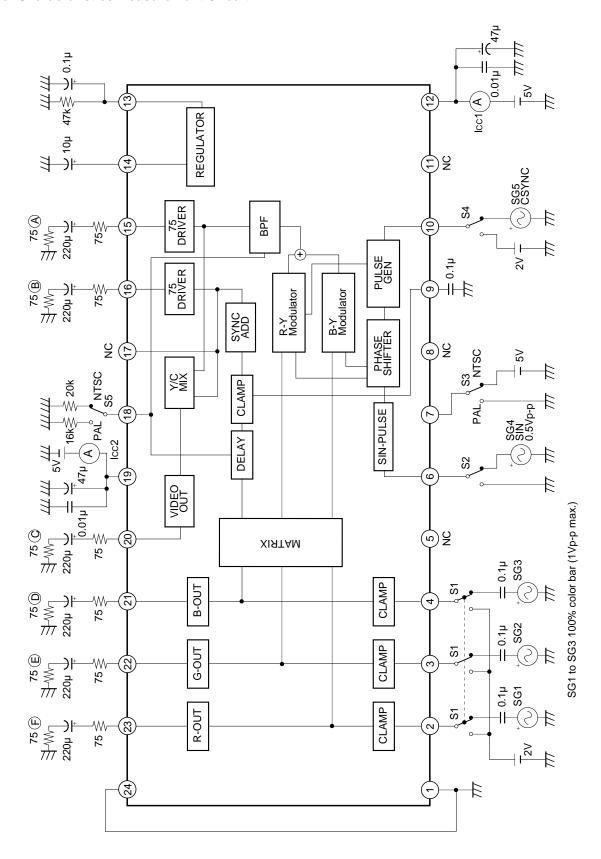

#### **Electrical Characteristics Measurement Circuit**

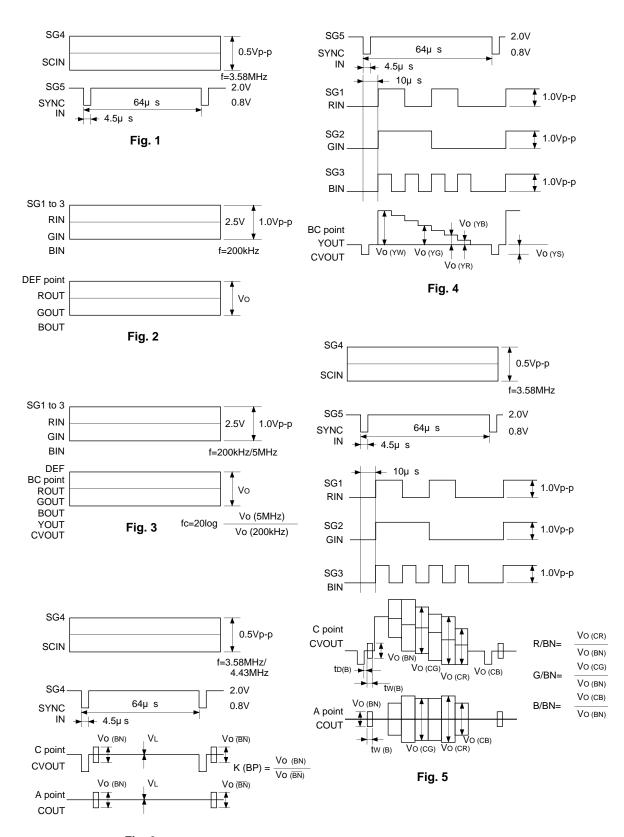

#### **Measuring Signals and Output Waveforms**

Fig. 6

CXA1645P/M

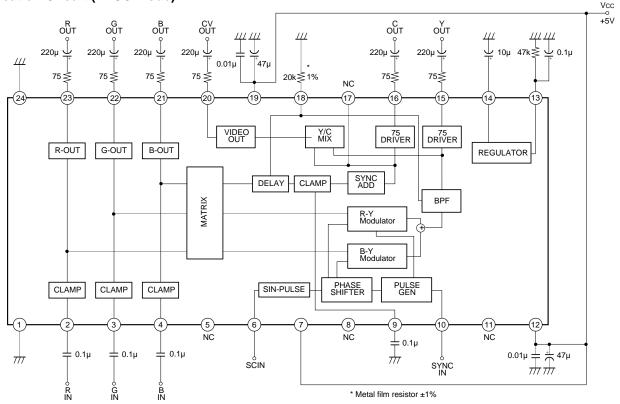

#### **Application Circuit (NTSC mode)**

#### **Application Circuit (PAL mode)**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### **Description of Operation**

Analog RGB signals input from pins 2, 3 and 4 are clamped in the clamping circuit and output from pins 23, 22 and 21, respectively.

The matrix circuit performs operations on each input signal, generating luminance signal Y and color difference signals R-Y and B-Y. The Y signal enters the delay line to adjust delay time with the color signal C. Then, after addition of the CSYNC signal input from pin 10, the Y signal is output from Pin 16.

A subcarrier input from Pin 6 is input to the phase shifter, where its phase is shifted 90°. Then, the subcarrier is input to the modulators and modulated by

the R-Y signal and the B-Y signal. Modulated subcarriers are mixed, sent to the band pass filter to eliminate higher harmonic components and finally output from Pin 15 as the C signal. At the same time, Y and C signals are mixed and output from Pin 20 as the composite video signal.

#### **Burst Signal**

The CXA1645P/M generates burst signals at the timing shown below according to the composite sync signal input.

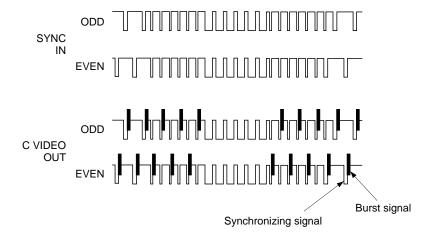

#### H synchronization

#### V synchronization

#### **Notes on Operation**

Be careful of the following when using the CXA1645P/M.

- This IC is designed for image processing of personal computers and video games. When using the IC in other video devices, make thorough investigations on image quality.

- Be sure that analog RGB signals are input at 1.0Vp-p maximum and have low enough impedance. High impedance may affect color saturation, hue, etc. Inputting RGB signals in excess of 1.3Vp-p may disable the clamp operation.

- 3. The SC input (Pin 6) can be either a sine wave or a pulse in the range from 0.4 to 5.0Vp-p. However, when a pulse is input, its phase may be shifted several degrees from that of the sine wave input. In the IC, the SC input is biased to 1/2 Vcc. Accordingly, when a 5.0Vp-p pulse is input and the duty factor deviates from 50%, high- and low-level pulse voltages may exceed Vcc and GND in the IC, which causes subcarrier distortion. In such a case, be very careful that the duty factor keeps to 50%.

- 4. When designing a printed circuit board pattern, pay careful attention to the routing of the Vcc and GND leads. To decouple the Vcc and VREF pins, use tantalum, ceramic or other capacitors with good frequency characteristics. Ground the capacitors by connections shown below as closely to each IC pin as possible. Try to design the leads as short and wide as possible.

Design the pattern so that Vcc (or VREF) is connected to GND via a capacitor at the shortest distance.

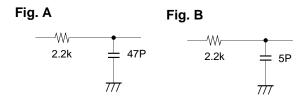

#### 5. SC and SYNC input pulses

Attach a resistor and a capacitor to eliminate high-frequency components of SC (Figure A) and SYNC (Figure B) before input.

Be careful not to input pulses containing high-frequency components. Otherwise, high-frequency components may flow into Vcc, GND and peripheral parts, resulting in malfunctions.

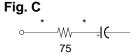

6. Use care when connecting an external resistor to the  $75\Omega$  driver output pin. A capacitance of several dozen picofarads at each pin may start oscillation. To prevent oscillation, design the pattern so that a  $75\Omega$  resistor is mounted near the pin (see Figure C).

\* Make these leads short.

When any of the  $75\Omega$  driver output pins are not in use, leave them unconnected and design the pattern so that no parasitic capacitance is generated on the printed circuit board.

#### 7. VREF pin (Pin 14)

Do not connect this pin to an external load that might cause AC signals to flow, which will cause IC malfunctions. When connecting a DC load, make sure that the current flowing from this pin is kept below 2mA.

SONY

CXA1645P/M

8. YTRAP pin (Pin 17)

There are the following two means of reducing cross color generated by subcarrier frequency components contained in the Y signal.

(1) Install a capacitor of 30 to 68pF between YTRAP and GND. Decide the capacitance by conducting image evaluation, etc., giving consideration to both cross color and resolution. Relations between capacitance and image quality are as follows:

| Capacitance | 30pF ↔ 68pF   |

|-------------|---------------|

| Cross color | Large ↔ Small |

| Resolution  | High ↔ Low    |

(2) Connect a capacitor C and an inductor L in series between YTRAP and GND. When the subcarrier frequency is fo, the values C and L are determined by the equation fo =  $\frac{1}{2\pi\sqrt{LC}}$ . Decide the values in image evaluation, etc., giving consideration to both cross color and resolution. Relations between inductor values and image quality are as follows:

| Inductor value            | Small ↔ Large                                                                          |

|---------------------------|----------------------------------------------------------------------------------------|

| Cross color<br>Resolution | $\begin{array}{c} Large \leftrightarrow Small \\ High \leftrightarrow Low \end{array}$ |

For instance, L=68µH and C=28pF are recommended for NTSC. It is necessary to select an inductor L with a sufficiently small DC resistance. Method (2) is more useful for achieving a higher resoluation than method (1). When an even higher resolution is necessary, use of the S terminal (YOUT and COUT) is recommended.

9. Driving COUT (pin 15), YOUT (Pin 16), CVOUT

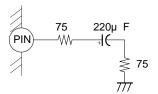

(Pin 20), and B.G.R OUT (pins 21, 22 and 23) outputs. In Pin Description, "Capable of driving a  $75\Omega$  load" means that the pin can drive a capacitor  $+75\Omega+75$  load shown in the figure below. In other words, the pin is capable of driving a  $150\Omega$  load in AC.

Keep in mind that the pin is incapable of driving a 150 load in DC load in DC direct coupling.

10. This IC employs a number of  $75\Omega$  driver pins, so oscillation is likely to occur when the measures described in Nos. 4 and 6 are not thoroughly observed. Be very careful of oscillation in printed circuit board design and carry out thorough investigations in the actual driving condition.

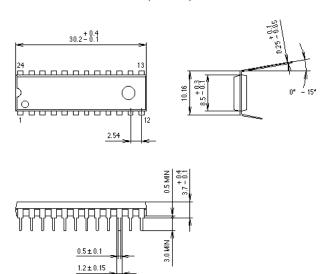

# Package Outline

CXA1645P

Unit: mm

24PIN DIP (PLASTIC) 400mil

| SONY CODE  | DIP-24P-01        |

|------------|-------------------|

| EIAJ CODE  | жD IP024-P-0400-А |

| JEDEC CODE |                   |

| PACKAGE STRUCT   | JRE              |

|------------------|------------------|

| PACKAGE MATERIAL | EPOXY RESIN      |

| LEAD TREATMENT   | SOLDER PLATING   |

| LEAD MATERIAL    | COPPER /42 ALLOY |

| PACKAGE WEIGHT   | 2.0g             |

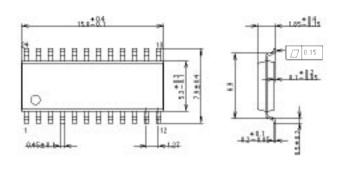

#### CXA1645M

24PIN SOP (PLASTIC)

| SOMY CODE  | 909-84P481        |

|------------|-------------------|

| ENI/CODE   | *50 F054 F-8080-A |

| Jepec cope | -                 |

PACKAGE STRUCTURE

FACKAGEMATERAL FROM RESIN

LEAD TREATMENT SOLDER RATING

LEAD MATERIAL COPPER ALLOWEALLOW

FACKAGE WEIGHT # 3g