2014.06.30 QII53030 Subscribe 💭 Send Feedback

# **Timing Analysis Overview**

Comprehensive static timing analysis involves analysis of register-to-register, I/O, and asynchronous reset paths. Timing analysis with the TimeQuest Timing Analyzer uses data required times, data arrival times, and clock arrival times to verify circuit performance and detect possible timing violations.

The TimeQuest analyzer determines the timing relationships that must be met for the design to correctly function, and checks arrival times against required times to verify timing. This chapter is an overview of the concepts you need to know to analyze your designs with the TimeQuest analyzer.

# **Related Information**

### The Quartus II TimeQuest Timing Analyzer

For more information about the TimeQuest analyzer flow and TimeQuest examples.

# **TimeQuest Terminology and Concepts**

| Term   | Definition                                                                                                                               |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| nodes  | Most basic timing netlist unit. Used to represent ports, pins, and registers.                                                            |

| cells  | Look-up tables (LUT), registers, digital signal processing (DSP) blocks, memory blocks, input/output elements, and so on. <sup>(1)</sup> |

| pins   | Inputs or outputs of cells.                                                                                                              |

| nets   | Connections between pins.                                                                                                                |

| ports  | Top-level module inputs or outputs; for example, device pins.                                                                            |

| clocks | Abstract objects representing clock domains inside or outside of your design.                                                            |

# Table 6-1: TimeQuest Analyzer Terminology

1. For Stratix<sup>®</sup> devices, the LUTs and registers are contained in logic elements (LE) and modeled as cells.

© 2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

# **Timing Netlists and Timing Paths**

The TimeQuest analyzer requires a timing netlist to perform timing analysis on any design. After you generate a timing netlist, the TimeQuest analyzer uses the data to help determine the different design elements in your design and how to analyze timing.

# **The Timing Netlist**

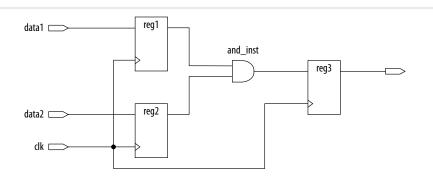

A sample design for which the TimeQuest analyzer generates a timing netlist equivalent.

# Figure 6-1: Sample Design

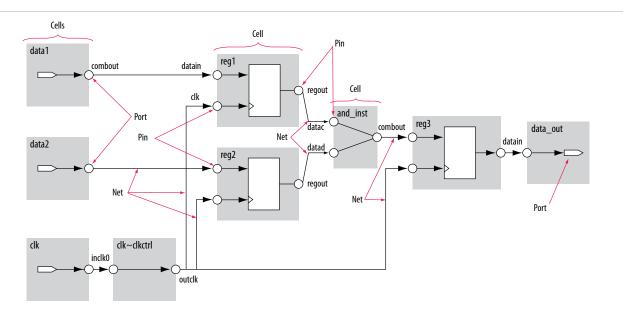

The timing netlist for the sample design shows how different design elements are divided into cells, pins, nets, and ports.

Figure 6-2: The TimeQuest Analyzer Timing Netlist

# **Timing Paths**

Timing paths connect two design nodes, such as the output of a register to the input of another register.

**Altera Corporation**

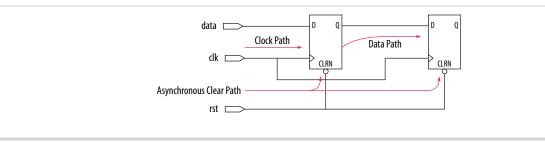

Understanding the types of timing paths is important to timing closure and optimization. The TimeQuest analyzer uses the following commonly analyzed paths:

- Edge paths—connections from ports-to-pins, from pins-to-pins, and from pins-to-ports.

- **Clock paths**—connections from device ports or internally generated clock pins to the clock pin of a register.

- **Data paths**—connections from a port or the data output pin of a sequential element to a port or the data input pin of another sequential element.

- Asynchronous paths—connections from a port or asynchronous pins of another sequential element such as an asynchronous reset or asynchronous clear.

#### Figure 6-3: Path Types Commonly Analyzed by the TimeQuest Analyzer

In addition to identifying various paths in a design, the TimeQuest analyzer analyzes clock characteristics to compute the worst-case requirement between any two registers in a single register-to-register path. You must constrain all clocks in your design before analyzing clock characteristics.

# **Data and Clock Arrival Times**

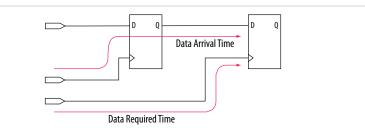

After the TimeQuest analyzer identifies the path type, it can report data and clock arrival times at register pins.

The TimeQuest analyzer calculates data arrival time by adding the launch edge time to the delay from the clock source to the clock pin of the source register, the micro clock-to-output delay ( $\mu t_{CO}$ ) of the source register, and the delay from the source register's data output (Q) to the destination register's data input (D).

The TimeQuest analyzer calculates data required time by adding the latch edge time to the sum of all delays between the clock port and the clock pin of the destination register, including any clock port buffer delays, and subtracts the micro setup time ( $\mu t_{SU}$ ) of the destination register, where the  $\mu t_{SU}$  is the intrinsic setup time of an internal register in the FPGA.

### Figure 6-4: Data Arrival and Data Required Times

The basic calculations for data arrival and data required times including the launch and latch edges.

#### Figure 6-5: Data Arrival and Data Required Time Equations

```

Data Arrival Time=Launch Edge + Source Clock Delay + \mu t_{co} + Register-to-Register DelayData Required Time=Latch Edge + Destination Clock Delay - \mu t_{su}

```

# Launch and Latch Edges

All timing relies on one or more clocks. In addition to analyzing paths, the TimeQuest analyzer determines clock relationships for all register-to-register transfers in your design.

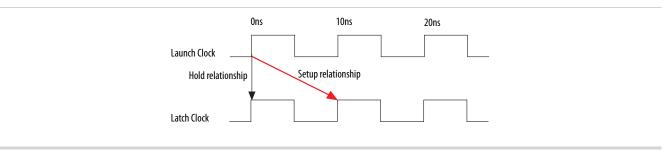

The following figure shows the launch edge, which is the clock edge that sends data out of a register or other sequential element, and acts as a source for the data transfer. A latch edge is the active clock edge that captures data at the data port of a register or other sequential element, acting as a destination for the data transfer. In this example, the launch edge sends the data from register regl at 0 ns, and the register reg2 captures the data when triggered by the latch edge at 10 ns. The data arrives at the destination register before the next latch edge.

#### Figure 6-6: Setup and Hold Relationship for Launch and Latch Edges 10ns Apart

In timing analysis, and with the TimeQuest analyzer specifically, you create clock constraints and assign those constraints to nodes in your design. These clock constraints provide the structure required for repeatable data relationships. The primary relationships between clocks, in the same or different domains, are the setup relationship and the hold relationship.

**Note:** If you do not constrain the clocks in your design, the Quartus II software analyzes in terms of a 1 GHz clock to maximize timing based Fitter effort. To ensure realistic slack values, you must constrain all clocks in your design with real values.

# **Clock Setup Check**

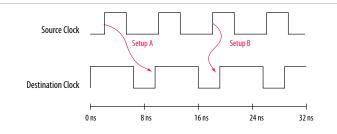

To perform a clock setup check, the TimeQuest analyzer determines a setup relationship by analyzing each launch and latch edge for each register-to-register path.

For each latch edge at the destination register, the TimeQuest analyzer uses the closest previous clock edge at the source register as the launch edge. The following figure shows two setup relationships, setup A and setup B. For the latch edge at 10 ns, the closest clock that acts as a launch edge is at 3 ns and is labeled setup A. For the latch edge at 20 ns, the closest clock that acts as a launch edge is 19 ns and is labeled setup B. TimQuest analyzes the most restrictive setup relationship, in this case setup B; if that relationship meets the design requirement, then setup A meets it by default.

**Altera Corporation**

6-5

#### Figure 6-7: Setup Check

The TimeQuest analyzer reports the result of clock setup checks as slack values. Slack is the margin by which a timing requirement is met or not met. Positive slack indicates the margin by which a requirement is met; negative slack indicates the margin by which a requirement is not met.

#### Figure 6-8: Clock Setup Slack for Internal Register-to-Register Paths

| Clock Setup Slack  | = Data Required Time – Data Arrival Time                                                           |

|--------------------|----------------------------------------------------------------------------------------------------|

| Data Arrival Time  | = Launch Edge + Clock Network Delay to Source Register + $\mu t_{c0}$ + Register-to-Register Delay |

| Data Required Time | = Latch Edge + Clock Network Delay to Destination Register – $\mu t_{SU}$ – Setup Uncertainty      |

The TimeQuest analyzer performs setup checks using the maximum delay when calculating data arrival time, and minimum delay when calculating data required time.

#### Figure 6-9: Clock Setup Slack from Input Port to Internal Register

| Clock Setup Slack  | = Data Required Time – Data Arrival Time                                                        |

|--------------------|-------------------------------------------------------------------------------------------------|

| Data Arrival Time  | = Launch Edge + Clock Network Delay + Input Maximum Delay + Port-to-Register Delay              |

| Data Required Time | $=$ Latch Edge + Clock Network Delay to Destination Register – $\mu t_{su}$ – Setup Uncertainty |

#### Figure 6-10: Clock Setup Slack from Internal Register to Output Port

| Clock Setup Slack  | = Data Required Time – Data Arrival Time                                                       |

|--------------------|------------------------------------------------------------------------------------------------|

| Data Required Time | = Latch Edge + Clock Network Delay to Output Port – Output Maximum Delay                       |

| Data Arrival Time  | = Launch Edge + Clock Network Delay to Source Register + $\mu t_{co}$ + Register-to-Port Delay |

# **Clock Hold Check**

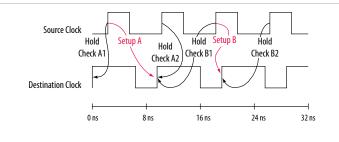

To perform a clock hold check, the TimeQuest analyzer determines a hold relationship for each possible setup relationship that exists for all source and destination register pairs. The TimeQuest analyzer checks all adjacent clock edges from all setup relationships to determine the hold relationships.

**Timing Analysis Overview**

**Altera Corporation**

The TimeQuest analyzer performs two hold checks for each setup relationship. The first hold check determines that the data launched by the current launch edge is not captured by the previous latch edge. The second hold check determines that the data launched by the next launch edge is not captured by the current latch edge. From the possible hold relationships, the TimeQuest analyzer selects the hold relationship that is the most restrictive. The most restrictive hold relationship is the hold relationship with the smallest difference between the latch and launch edges and determines the minimum allowable delay for the register-to-register path. In the following example, the TimeQuest analyzer selects hold check A2 as the most restrictive hold relationship of two setup relationships, setup A and setup B, and their respective hold checks.

#### Figure 6-11: Setup and Hold Check Relationships

### Figure 6-12: Clock Hold Slack for Internal Register-to-Register Paths

Clock Hold Slack = Data Arrival Time – Data Required TimeData Arrival Time= Launch Edge + Clock Network Delay to Source Register +  $\mu t_{co}$  + Register-to-Register DelayData Required Time= Latch Edge + Clock Network Delay to Destination Register +  $\mu t_{\mu}$  + Hold Uncertainty

The TimeQuest analyzer performs hold checks using the minimum delay when calculating data arrival time, and maximum delay when calculating data required time.

#### Figure 6-13: Clock Hold Slack Calculation from Input Port to Internal Register

### Figure 6-14: Clock Hold Slack Calculation from Internal Register to Output Port

Clock Hold Slack = Data Arrival Time – Data Required Time

Data Arrival Time

= Latch Edge + Clock Network Delay to Source Register +  $\mu t_{co}$  + Register-to-Pin Delay

Data Required Time

= Latch Edge + Clock Network Delay – Output Minimum Delay

# **Recovery and Removal Time**

Recovery time is the minimum length of time for the deassertion of an asynchronous control signal relative to the next clock edge.

**Altera Corporation**

For example, signals such as clear and preset must be stable before the next active clock edge. The recovery slack calculation is similar to the clock setup slack calculation, but it applies to asynchronous control signals.

#### Figure 6-15: Recovery Slack Calculation if the Asynchronous Control Signal is Registered

| Recovery Slack Time | = Data Required Time – Data Arrival Time                                                           |

|---------------------|----------------------------------------------------------------------------------------------------|

| Data Required Time  | = Latch Edge + Clock Network Delay to Destination Register – μt <sub>su</sub>                      |

| Data Arrival Time   | = Launch Edge + Clock Network Delay to Source Register + $\mu t_{c0}$ + Register-to-Register Delay |

#### Figure 6-16: Recovery Slack Calculation if the Asynchronous Control Signal is not Registered

| Recovery Slack Time | = Data Required Time – Data Arrival Time                                                                                                               |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Required Time  | = Latch Edge + Clock Network Delay to Destination Register – $\mu t_{su}$                                                                              |

| Data Arrival Time   | $= {\sf Launch}  {\sf Edge} + {\sf Clock}  {\sf Network}  {\sf Delay} + {\sf Input}  {\sf Maximum}  {\sf Delay} + {\sf Port-to-Register}  {\sf Delay}$ |

**Note:** If the asynchronous reset signal is from a device I/O port, you must create an input delay constraint for the asynchronous reset port for the TimeQuest analyzer to perform recovery analysis on the path.

Removal time is the minimum length of time the deassertion of an asynchronous control signal must be stable after the active clock edge. The TimeQuest analyzer removal slack calculation is similar to the clock hold slack calculation, but it applies asynchronous control signals.

#### Figure 6-17: Removal Slack Calcuation if the Asynchronous Control Signal is Registered

| Removal Slack Time | = Data Arrival Time – Data Required Time                                                                                |

|--------------------|-------------------------------------------------------------------------------------------------------------------------|

| Data Arrival Time  | $=$ Launch Edge + Clock Network Delay to Source Register + $\mu t_{c0}$ of Source Register + Register-to-Register Delay |

| Data Required Time | = Latch Edge + Clock Network Delay to Destination Register + $\mu t_{_H}$                                               |

# Figure 6-18: Removal Slack Calculation if the Asynchronous Control Signal is not Registered

| Removal Slack Time | = Data Arrival Time – Data Required Time                                                         |

|--------------------|--------------------------------------------------------------------------------------------------|

| Data Arrival Time  | = Launch Edge + Clock Network Delay + Input Minimum Delay of Pin + Minimum Pin-to-Register Delay |

| Data Required Time | = Latch Edge + Clock Network Delay to Destination Register + $\mu t_{\mu}$                       |

If the asynchronous reset signal is from a device pin, you must assign the **Input Minimum Delay** timing assignment to the asynchronous reset pin for the TimeQuest analyzer to perform removal analysis on the path.

# **Multicycle Paths**

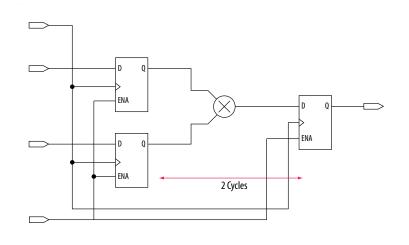

Multicycle paths are data paths that require a non-default setup and/or hold relationship for proper analysis.

**Timing Analysis Overview**

**Altera Corporation**

For example, a register may be required to capture data on every second or third rising clock edge. An example of a multicycle path between the input registers of a multiplier and an output register where the destination latches data on every other clock edge.

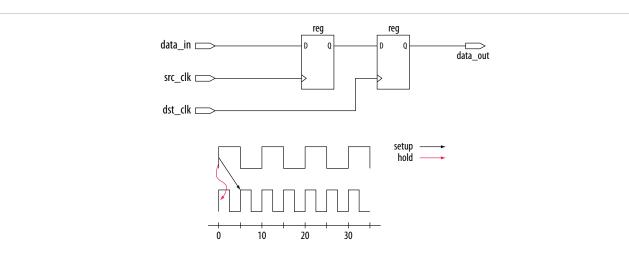

## Figure 6-19: Multicycle Path

A register-to-register path used for the default setup and hold relationship, the respective timing diagrams for the source and destination clocks, and the default setup and hold relationships, when the source clock, src\_clk, has a period of 10 ns and the destination clock, dst\_clk, has a period of 5 ns. The default setup relationship is 5 ns; the default hold relationship is 0 ns.

#### Figure 6-20: Register-to-Register Path and Default Setup and Hold Timing Diagram

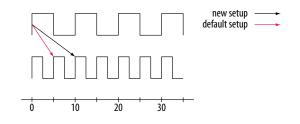

To accommodate the system requirements you can modify the default setup and hold relationships with a multicycle timing exception.

The actual setup relationship after you apply a multicycle timing exception. The exception has a multicycle setup assignment of two to use the second occurring latch edge; in this example, to 10 ns from the default value of 5 ns.

**Timing Analysis Overview**

Send Feedback

6-9

## Figure 6-21: Modified Setup Diagram

#### **Related Information**

#### The Quartus II TimeQuest Timing Analyzer

For more information about creating exceptions with multicycle paths.

# Metastability

Metastability problems can occur when a signal is transferred between circuitry in unrelated or asynchronous clock domains because the designer cannot guarantee that the signal will meet setup and hold time requirements.

To minimize the failures due to metastability, circuit designers typically use a sequence of registers, also known as a synchronization register chain, or synchronizer, in the destination clock domain to resynchronize the data signals to the new clock domain.

The mean time between failures (MTBF) is an estimate of the average time between instances of failure due to metastability.

The TimeQuest analyzer analyzes the potential for metastability in your design and can calculate the MTBF for synchronization register chains. The MTBF of the entire design is then estimated based on the synchronization chains it contains.

In addition to reporting synchronization register chains found in the design, the Quartus II software also protects these registers from optimizations that might negatively impact MTBF, such as register duplication and logic retiming. The Quartus II software can also optimize the MTBF of your design if the MTBF is too low.

#### **Related Information**

**Understanding Metastability in FPGAs**

For more information about metastability, its effects in FPGAs, and how MTBF is calculated.

Managing Metastability with the Quartus II Software

For more information about metastability analysis, reporting, and optimization features in the Quartus II software.

# **Common Clock Path Pessimism Removal**

Common clock path pessimism removal accounts for the minimum and maximum delay variation associated with common clock paths during static timing analysis by adding the difference between the maximum and minimum delay value of the common clock path to the appropriate slack equation.

Minimum and maximum delay variation can occur when two different delay values are used for the same clock path. For example, in a simple setup analysis, the maximum clock path delay to the source register is used to determine the data arrival time. The minimum clock path delay to the destination register is used

to determine the data required time. However, if the clock path to the source register and to the destination register share a common clock path, both the maximum delay and the minimum delay are used to model the common clock path during timing analysis. The use of both the minimum delay and maximum delay results in an overly pessimistic analysis since two different delay values, the maximum and minimum delays, cannot be used to model the same clock path.

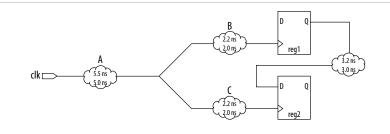

## Figure 6-22: Typical Register to Register Path

Segment A is the common clock path between reg1 and reg2. The minimum delay is 5.0 ns; the maximum delay is 5.5 ns. The difference between the maximum and minimum delay value equals the common clock path pessimism removal value; in this case, the common clock path pessimism is 0.5 ns. The TimeQuest analyzer adds the common clock path pessimism removal value to the appropriate slack equation to determine overall slack. Therefore, if the setup slack for the register-to-register path in the example equals 0.7 ns without common clock path pessimism removal, the slack would be 1.2 ns with common clock path pessimism removal.

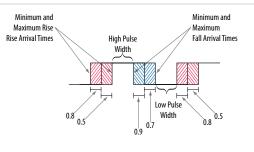

You can also use common clock path pessimism removal to determine the minimum pulse width of a register. A clock signal must meet a register's minimum pulse width requirement to be recognized by the register. A minimum high time defines the minimum pulse width for a positive-edge triggered register. A minimum low time defines the minimum pulse width for a negative-edge triggered register.

Clock pulses that violate the minimum pulse width of a register prevent data from being latched at the data pin of the register. To calculate the slack of the minimum pulse width, the TimeQuest analyzer subtracts the required minimum pulse width time from the actual minimum pulse width time. The TimeQuest analyzer determines the actual minimum pulse width time by the clock requirement you specified for the clock that feeds the clock port of the register. The TimeQuest analyzer determines the required minimum pulse width time by the maximum rise, minimum rise, maximum fall, and minimum fall times.

### Figure 6-23: Required Minimum Pulse Width time for the High and Low Pulse

With common clock path pessimism, the minimum pulse width slack can be increased by the smallest value of either the maximum rise time minus the minimum rise time, or the maximum fall time minus the minimum fall time. In the example, the slack value can be increased by 0.2 ns, which is the smallest value between 0.3 ns (0.8 ns – 0.5 ns) and 0.2 ns (0.9 ns – 0.7 ns).

Altera Corporation

**Timing Analysis Overview**

#### Send Feedback

#### **Related Information**

TimeQuest Timing Analyzer Page (Settings Dialog Box

For more information, refer to the Quartus II Help.

# **Clock-As-Data Analysis**

The majority of FPGA designs contain simple connections between any two nodes known as either a data path or a clock path.

A data path is a connection between the output of a synchronous element to the input of another synchronous element.

A clock is a connection to the clock pin of a synchronous element. However, for more complex FPGA designs, such as designs that use source-synchronous interfaces, this simplified view is no longer sufficient. Clockas-data analysis is performed in circuits with elements such as clock dividers and DDR source-synchronous outputs.

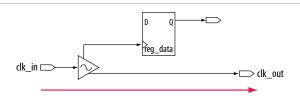

The connection between the input clock port and output clock port can be treated either as a clock path or a data path. A design where the path from port clk\_in to port clk\_out is both a clock and a data path. The clock path is from the port clk\_in to the register reg\_data clock pin. The data path is from port clk\_in to the port clk\_out.

# Figure 6-24: Simplified Source Synchronous Output

With clock-as-data analysis, the TimeQuest analyzer provides a more accurate analysis of the path based on user constraints. For the clock path analysis, any phase shift associated with the phase-locked loop (PLL) is taken into consideration. For the data path analysis, any phase shift associated with the PLL is taken into consideration rather than ignored.

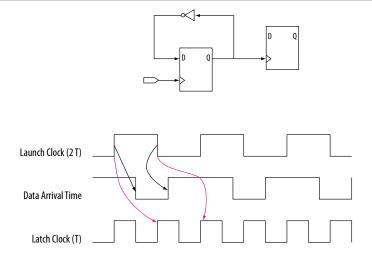

The clock-as-data analysis also applies to internally generated clock dividers. An internally generated clock divider. In this figure, waveforms are for the inverter feedback path, analyzed during timing analysis. The output of the divider register is used to determine the launch time and the clock port of the register is used to determine the launch time and the clock port of the register is used to determine the launch time.

**Timing Analysis Overview**

**Altera Corporation**

# Figure 6-25: Clock Divider

# **Multicorner Analysis**

The TimeQuest analyzer performs multicorner timing analysis to verify your design under a variety of operating conditions—such as voltage, process, and temperature—while performing static timing analysis.

To change the operating conditions or speed grade of the device used for timing analysis, use the set\_operating\_conditions command.

If you specify an operating condition Tcl object, the -model, speed, -temperature, and -voltage options are optional. If you do not specify an operating condition Tcl object, the -model option is required; the -speed, -temperature, and -voltage options are optional.

**Tip:** To obtain a list of available operating conditions for the target device, use the get\_available\_operating\_conditions -all command.

To ensure that no violations occur under various conditions during the device operation, perform static timing analysis under all available operating conditions.

| Table 6-2: 0 | Operating | Conditions | for Slow | and Fast Models |

|--------------|-----------|------------|----------|-----------------|

|              |           |            |          |                 |

| Model | Speed Grade                           | Voltage                                       | Temperature                           |

|-------|---------------------------------------|-----------------------------------------------|---------------------------------------|

| Slow  | Slowest speed grade in device density | V <sub>cc</sub> minimum supply <sup>(1)</sup> | Maximum T <sub>J</sub> <sup>(1)</sup> |

| Fast  | Fastest speed grade in device density | $V_{cc}$ maximum supply <sup>(1)</sup>        | Minimum T <sub>J</sub> <sup>(1)</sup> |

Note :

1. Refer to the DC & Switching Characteristics chapter of the applicable device Handbook for V<sub>cc</sub> and T<sub>J</sub>. values

In your design, you can set the operating conditions for to the slow timing model, with a voltage of 1100 mV, and temperature of 85° C with the following code:

```

set_operating_conditions -model slow -temperature 85 -voltage 1100

```

**Altera Corporation**

You can set the same operating conditions with a Tcl object:

set\_operating\_conditions 3\_slow\_1100mv\_85c

The following block of code shows how to use the set\_operating\_conditions command to generate different reports for various operating conditions.

### Example 6-1: Script Excerpt for Analysis of Various Operating Conditions

```

#Specify initial operating conditions

set_operating_conditions -model slow -speed 3 -grade c -temperature 85 -voltage

1100

#Update the timing netlist with the initial conditions

update_timing_netlist

#Perform reporting

#Change initial operating conditions. Use a temperature of OC

set_operating_conditions -model slow -speed 3 -grade c -temperature 0 -voltage

1100

#Update the timing netlist with the new operating condition

update_timing_netlist

#Perform reporting

#Change initial operating conditions. Use a temperature of 0C and a model of

fast

set_operating_conditions -model fast -speed 3 -grade c -temperature 0 -voltage

1100

#Update the timing netlist with the new operating condition

update_timing_netlist

#Perform reporting

```

```

Related Information

```

set\_operating\_conditions

get\_available\_operating\_conditions

For more information about the get\_available\_operating\_conditions command

# **Document Revision History**

## Table 6-3: Document Revision History

| Date          | Version | Changes                                           |

|---------------|---------|---------------------------------------------------|

| June 2014     | 14.0.0  | Updated format                                    |

| June 2012     | 12.0.0  | Added social networking icons, minor text updates |

| November 2011 | 11.1.0  | Initial release.                                  |

#### **Related Information**

**Quartus II Handbook Archive**

For previous versions of the Quartus II Handbook.