# 7. The Quartus II TimeQuest Timing Analyzer

The Quartus<sup>®</sup> II TimeQuest Timing Analyzer is a powerful ASIC-style timing analysis tool that validates the timing performance of all logic in your design using an industry-standard constraint, analysis, and reporting methodology. Use the TimeQuest analyzer GUI or command-line interface to constrain, analyze, and report results for all timing paths in your design.

This chapter contains the following sections:

- "Getting Started with the TimeQuest Analyzer"

- "Constraining and Analyzing with Tcl Commands" on page 7–7

- "Creating Clocks and Clock Constraints" on page 7–14

- "Creating I/O Requirements" on page 7–24

- "Creating Delay and Skew Constraints" on page 7–26

- "Creating Timing Exceptions" on page 7–27

- "Examples of Basic Multicycle Exceptions" on page 7–35

- "Application of Multicycle Exceptions" on page 7–44

- "Timing Reports" on page 7–57

- For more information about basic timing analysis concepts and how they pertain to the TimeQuest analyzer, refer to the *Timing Analysis Overview* chapter in volume 3 of the *Quartus II Handbook*.

- **For more information about Altera resources available for the TimeQuest analyzer,** refer to the TimeQuest Timing Analyzer Resource Center of the Altera website.

- **For more information about the TimeQuest analyzer, refer to the Altera Training page of the Altera website.**

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and summers or any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Getting Started with the TimeQuest Analyzer**

This section provides an overview of the design steps for setting up your project for timing and analysis and to constrain your design with the TimeQuest analyzer.

# **Running the TimeQuest Analyzer**

To run the TimeQuest analyzer directly from the Quartus II software GUI, click **TimeQuest Timing Analyzer** on the Tools menu.

? For more information about the TimeQuest analyzer GUI, refer to About TimeQuest Timing Analysis in Quartus II Help.

To run the TimeQuest analyzer as a stand-alone GUI application, type the following command at the command prompt:

quartus\_staw 🛩

To run the TimeQuest analyzer in command-line mode for easy integration with scripted design flows, type the following command at a system command prompt:

quartus\_sta -s←

Table 7–1 describes the available command-line options.

| Table 7–1. Summary of Command-Line Optic | ons (Part 1 of 2) |

|------------------------------------------|-------------------|

|------------------------------------------|-------------------|

| Command-Line Option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| -h  help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Provides help information on quartus_sta. |

| -t <script file="">  <br>script=<script file></td><td>Sources the <i><script file></i>.</td></tr><tr><td>-s  shell</td><td>Enters shell mode.</td></tr><tr><td>tcl_eval <tcl command></td><td>Evaluates the Tcl command <i><tcl command></i>.</td></tr><tr><td></td><td>For all clocks in the design, run the following commands:</td></tr><tr><td></td><td>report_timing -npaths 1 -to_clock \$clock</td></tr><tr><td></td><td>report_timing -setup -npaths 1 -to_clock \$clock</td></tr><tr><td>do_report_timing</td><td>report_timing -hold -npaths 1 -to_clock \$clock</td></tr><tr><td></td><td>report_timing -recovery -npaths 1 -to_clock \$clock</td></tr><tr><td></td><td>report_timing -removal -npaths 1 -to_clock \$clock</td></tr><tr><td>force_dat</td><td>Forces an update of the project database with new delay information.</td></tr><tr><td>lower_priority</td><td>Lowers the computing priority of the quartus_sta process.</td></tr><tr><td>post_map</td><td>Uses the post-map database results.</td></tr><tr><td>sdc=<SDC file></td><td>Specifies the .sdc to use.</td></tr><tr><td>report_script=<script></td><td>Specifies a custom report script to call.</td></tr><tr><td>speed=<value></td><td>Specifies the device speed grade used for timing analysis.</td></tr><tr><td>tq2pt</td><td>Generates temporary files to convert the TimeQuest analyzer <b>.sdc</b> file(s) to a PrimeTime <b>.sdc</b>.</td></tr><tr><td>-f <argument file></td><td>Specifies a file containing additional command-line arguments.</td></tr><tr><td>-c <revision name>  <br>rev=<revision_name></td><td>Specifies which revision and its associated <b>.qsf</b> to use.</td></tr></tbody></table></script> |                                           |

| Command-Line Option                               | Description                                                                            |

|---------------------------------------------------|----------------------------------------------------------------------------------------|

| multicorner                                       | Specifies that all slack summary reports be generated for both slow- and fast-corners. |

| multicorner[=on off]                              | Turns off multicorner timing analysis.                                                 |

| voltage= <value_in_mv></value_in_mv>              | Specifies the device voltage, in mV used for timing analysis.                          |

| temperature=<br><value_in_c></value_in_c>         | Specifies the device temperature in degrees Celsius, used for timing analysis.         |

| parallel<br>[= <num_processors>]</num_processors> | Specifies the number of computer processors to use on a multiprocessor system.         |

| 64bit                                             | Enables 64-bit version of the executable.                                              |

| Table 7–1. Su | mmary of Comma | nd-Line Options | (Part 2 of 2) |

|---------------|----------------|-----------------|---------------|

|---------------|----------------|-----------------|---------------|

For more information about steps to perform before opening the TimeQuest analyzer, refer to "Recommended Flow" on page 7–3.

For more information about using Tcl commands to constrain and analyze your design, refer to "Constraining and Analyzing with Tcl Commands" on page 7–7.

### **Recommended Flow**

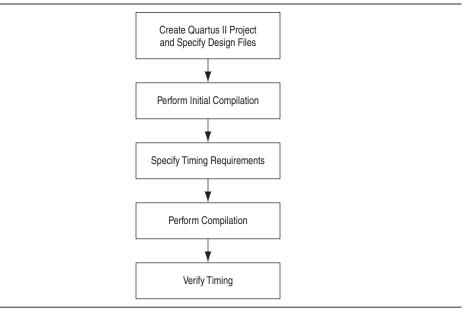

The Quartus II TimeQuest analyzer performs constraint validation to timing verification as part of the compilation flow. Figure 7–1 shows the recommended design flow to maximize the benefits of the TimeQuest Analyzer.

Figure 7–1. Design Flow with the TimeQuest Timing Analyzer

### **Creating and Setting Up your Design**

You must first create your project in the Quartus II software. Include all the necessary design files, including any existing Synopsys Design Constraints (.sdc) files that contain timing constraints for your design.

*?* For more information, refer to *Managing Files in a Project* in Quartus II Help.

### **Performing an Initial Compilation**

If you have never compiled your design, or you don't have an **.sdc** file, and you want to use the TimeQuest analyzer to create one interactively, you must compile your design to create an initial design database before you specify timing constraints. You can either perform Analysis and Synthesis to create a post-map database, or perform a full compilation to create a post-fit database. Creating a post-map database is faster than a post-fit database, and is sufficient for creating initial timing constraints. The type of database you create determines the type of timing netlist generated by the TimeQuest analyzer; a post-map netlist if you perform Analysis and Synthesis or a post-fit netlist if you perform a full compilation.

- If you are using incremental compilation, you must merge your design partitions after performing Analysis and Synthesis to create a post-map database.

- (?) For more information, refer to *Setting up and Running Analysis and Synthesis* and *Setting up and Running a Compilation* in Quartus II Help.

### **Specifying Timing Requirements**

Before running timing analysis with the TimeQuest analyzer, you must specify initial timing constraints that describe the clock characteristics, timing exceptions, and signal transition arrival and required times. You can use the TimeQuest Timing Analyzer Wizard to enter initial constraints for your design, and then refine timing constraints with the TimeQuest analyzer GUI or with a Tcl script.

- The Quartus II software assigns a default frequency of 1 GHz for clocks that have not been constrained, either in the TimeQuest GUI or an **.sdc** file, unless any constraint exists in the design. In that case, all unconstrained clocks remain unconstrained.

- ? For more information, refer to Specifying Timing Constraints and Exceptions in Quartus II Help.

The **.sdc** must contain only SDC commands. Tcl commands to manipulate the timing netlist or control the compilation flow should be run as part of a separate Tcl script. After you create timing constraints, update the timing netlist to apply the new constraints. The TimeQuest analyzer applies all constraints to the netlist for verification and removes any invalid or false paths in the design from verification.

I The constraints in the **.sdc** are read in sequence. You must first make a constraint before making any references to that constraint. For example, if a generated clock references a base clock, the base clock constraint must be made before the generated clock constraint.

The Quartus II Text Editor provides templates for SDC constraints. For more information, refer to "Using the Quartus II Templates" on page 7–6.

## **Performing a Full Compilation**

After creating initial timing constraints, you must fully compile your design. When compilation is complete, you can open the TimeQuest analyzer to verify timing results and to generate summary, clock setup and clock hold, recovery, and removal reports for all defined clocks in the design.

## **Verifying Timing**

The TimeQuest analyzer examines the timing paths in the design, calculates the propagation delay along each path, checks for timing constraint violations, and reports timing results as positive slack or negative slack. Negative slack indicates a timing violation. If you encounter violations along timing paths, use the timing reports to analyze your design and determine how best to optimize your design. If you modify, remove, or add constraints, you should perform a full compilation again. This iterative process helps resolve timing violations in your design.

⑦ For more information, refer to *Viewing Timing Analysis Results* in Quartus II Help.

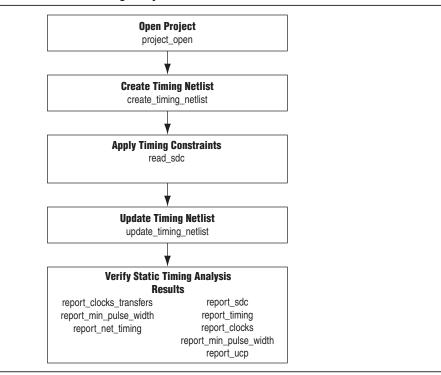

Figure 7–2 shows the recommended flow for constraining and analyzing your design within the TimeQuest analyzer. Included are the corresponding Tcl commands for each step.

Figure 7–2. The TimeQuest Timing Analyzer Flow

### **SDC File Precedence**

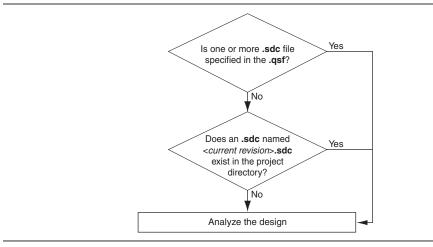

The Fitter and the TimeQuest analyzer process **.sdc** files in the order you specify in the Quartus II Settings File (**.qsf**). You can specify the files to process and the order they are processed from the **Assignments** menu. Click **Settings**, then **TimeQuest Timing Analyzer**. and specify a processing order in the **SDC files to include in the project** box.

If no **.sdc** files are listed in the **.qsf**, the Quartus II software looks for an **.sdc** named <*current revision*>**.sdc** in the project directory. An **.sdc** can also be added from a Quartus II IP File (**.qip**) included in the **.qsf**.

Figure 7–3 shows the order in which the Quartus II software searches for an .sdc.

Figure 7–3. .sdc File Order of Precedence

If you type the read\_sdc command at the command line without any arguments, the TimeQuest analyzer reads constraints embedded in HDL files, then follows the **.sdc** file precedence order shown in Figure 7–3.

# **Using the Quartus II Templates**

You can create an **.sdc** from constraint templates in the Quartus II software with the Quartus II Text Editor, or with your preferred text editor.

## **Creating a Constraint File with the Quartus II Text Editor**

To insert constraints with the Quartus II Text Editor, follow these steps:

- 1. On the File menu, click New.

- 2. In the **New** dialog box, select the **Synopsys Design Constraints File** type from the **Other Files** group. Click **OK**.

- 3. Click the **Insert Template** button on the text editor menu, or, right-click in the blank **.sdc** file in the Quartus II Text Editor, then click **Insert Template**.

- 4. In the **Insert Template** dialog box, expand the **TimeQuest** section, then expand the **SDC Commands** section.

- 5. Expand a command category, for example, Clocks.

- 6. Select a command. The SDC constraint appears in the Preview pane.

- 7. Click **Insert** to paste the SDC constraint into the blank **.sdc** you created in step 2.

- 8. Repeat as needed with other constraints, or click **Close** to close the **Insert Template** dialog box.

You can now use any of the standard features of the Quartus II Text Editor to modify the **.sdc** or save the **.sdc** to edit in a text editor.

? For more information on inserting a template with the Quartus II Text Editor, refer to *About the Quartus II Text Editor* in Quartus II Help.

# **Constraining and Analyzing with Tcl Commands**

You can use Tcl commands from the Quartus II software Tcl Application Programming Interface (API) to constrain, analyze, and collect information for your design. This section focuses on executing timing analysis tasks with Tcl commands; however, you can perform many of the same functions in the TimeQuest analyzer GUI. SDC commands are Tcl commands for constraining a design. SDC extension commands provide additional constraint methods and are specific to the TimeQuest analyzer. Additional TimeQuest analyzer commands are available for controlling timing analysis and reporting. These commands are contained in the following Tcl packages available in the Quartus II software:

- ::quartus::sta

- ::quartus::sdc

- ::quartus::sdc\_ext

- ⑦ For more information about TimeQuest analyzer Tcl commands and a complete list of commands, refer to ::quartus::sta in Quartus II Help. For more information about standard SDC commands and a complete list of commands, refer to ::quartus::sdc in Quartus II Help. For more information about Altera extensions of SDC commands and a complete list of commands, refer to ::quartus::sdc in Quartus II Help. For more information about Altera extensions of SDC commands and a complete list of commands, refer to ::quartus::sdc in Quartus II Help.

## **Collection Commands**

The TimeQuest analyzer Tcl commands often return port, pin, cell, or node names in a data set called a collection. In your Tcl scripts you can iterate over the values in collections to analyze or modify constraints in your design.

The TimeQuest analyzer supports collection commands that provide easy access to ports, pins, cells, or nodes in the design. Use collection commands with any valid constraints or Tcl commands specified in the TimeQuest analyzer.

Table 7–2 describes the collection commands supported by the TimeQuest analyzer.

Table 7–2. SDC Collection Commands (Part 1 of 2)

| Command       | Description of the collection returned                                                                                                                                                                                                                                                          |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| all_clocks    | All clocks in the design.                                                                                                                                                                                                                                                                       |

| all_inputs    | All input ports in the design.                                                                                                                                                                                                                                                                  |

| all_outputs   | All output ports in the design.                                                                                                                                                                                                                                                                 |

| all_registers | All registers in the design.                                                                                                                                                                                                                                                                    |

| get_cells     | Cells in the design. All cell names in the collection match the specified pattern. Wildcards can be used to select multiple cells at the same time.                                                                                                                                             |

| get_clocks    | Clocks in the design. When used as an argument to another command, such as the -from or -to of set_multicycle_path, each node in the clock represents all nodes clocked by the clocks in the collection. The default uses the specific node (even if it is a clock) as the target of a command. |

| get_nets      | Nets in the design. All net names in the collection match the specified pattern. You can use wildcards to select multiple nets at the same time.                                                                                                                                                |

| Command   | Description of the collection returned                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| get_pins  | Pins in the design. All pin names in the collection match the specified pattern. You can use wildcards to select multiple pins at the same time. |

| get_ports | Ports (design inputs and outputs) in the design.                                                                                                 |

#### Table 7–2. SDC Collection Commands (Part 2 of 2)

### **Wildcard Characters**

To apply constraints to many nodes in a design, use the "\*" and "?" wildcard characters. The "\*" wildcard character matches any string; the "?" wildcard character matches any single character.

If you make an assignment to node reg\*, the TimeQuest analyzer searches for and applies the assignment to all design nodes that match the prefix reg with any number of following characters, such as reg, reg1, reg[2], regbank, and reg12bank.

If you make an assignment to a node specified as reg?, the TimeQuest analyzer searches and applies the assignment to all design nodes that match the prefix reg and any single character following; for example, reg1, rega, and reg4.

### **Adding and Removing Collection Items**

Wildcards used with collection commands define collection items identified by the command. For example, if a design contains registers named src0, src1, src2, and dst0, the collection command [get\_registers src\*] identifies registers src0, src1, and src2, but not register dst0. To identify register dst0, you must use an additional command, [get\_registers dst\*]. To include dst0, you could also specify a collection command [get\_registers {src\* dst\*}].

To modify collections, use the add\_to\_collection and remove\_from\_collection commands. The add\_to\_collection command allows you to add additional items to an existing collection. Example 7–1 shows the add\_to\_collection command and arguments.

#### Example 7–1. add\_to\_collection Command

add\_to\_collection <first collection> <second collection>

The add\_to\_collection command creates a new collection that is the union of the two specified collections.

The remove\_from\_collection command allows you to remove items from an existing collection. Example 7–2 shows the remove\_from\_collection command and arguments.

#### Example 7–2. remove\_from\_collection Command

remove\_from\_collection <first collection> <second collection>

Example 7–3 shows examples of how to add elements to collections.

#### Example 7–3. Adding Items to a Collection

```

#Setting up initial collection of registers

set regs1 [get_registers a*]

#Setting up initial collection of keepers

set kprs1 [get_keepers b*]

#Creating a new set of registers of $regs1 and $kprs1

set regs_union [add_to_collection $kprs1 $regs1]

#OR

# Creating a new set of registers of $regs1 and b*

# Note that the new collection appends only registers with name b*

# not all keepers

set regs_union [add_to_collection $regs1 b*]

```

- In the Quartus II software, keepers are I/O ports or registers. An **.sdc** that includes get\_keepers can only be processed as part of the TimeQuest analyzer flow and is not compatible with third-party timing analysis flows.

- (?) For more information about the add\_to\_collection and remove\_from\_collection commands—including full syntax information, options, and example usage—refer to add\_to\_collection and remove\_from\_collection in Quartus II Help.

#### Using the query\_collection Command

You can display the contents of a collection with the query collection command.

Example 7–4 shows how to report the contents of a collection:

#### Example 7–4. query\_collection Command

query\_collection -report -all \$regs\_union

You can also examine collections and experiment with collections using wildcards in the TimeQuest analyzer by clicking **Name Finder** from the **View** menu.

#### Using the get\_pins Command

The collection commands get\_pins allow you to refine searches that include wildcard characters.

Table 7–3 shows examples of search strings that use options to refine the search and wildcards. The examples in Table 7–3 filter the following node and pin names to illustrate function:

- foo

- foo | dataa

- foo | datab

- foo|bar

- foo | bar | datac

#### ■ foo | bar | datad

Table 7–3.

Sample Search Strings and Search Results

| Search String                          | Search Result                  |

|----------------------------------------|--------------------------------|

| get_pins * dataa                       | foo dataa                      |

| get_pins * datac                       | <empty><sup>(1)</sup></empty>  |

| get_pins * * datac                     | foo bar datac                  |

| get_pins foo* *                        | foo dataa, foo datab           |

| get_pins -hierarchical * * datac       | <empty> (1)</empty>            |

| get_pins -hierarchical foo *           | foo dataa, foo datab           |

| get_pins -hierarchical * datac         | foo bar datac                  |

| get_pins -hierarchical foo * datac     | <empty> <sup>(1)</sup></empty> |

| get_pins -compatibility_mode * datac   | foo bar datac                  |

| get_pins -compatibility_mode * * datac | foo bar datac                  |

#### Note to Table 7-3:

(1) The search result is <empty> because more than one pipe character (|) is not supported.

The default method separates hierarchy levels of instances from nodes and pins with the pipe character (|). A match occurs when the levels of hierarchy match, and the string values including wildcards match the instance and/or pin names. For example, the command get\_pins <instance\_name>|\*|datac returns all the datac pins for registers in a given instance. However, the command get\_pins \*|datac returns and empty collection because the levels of hierarchy do not match.

Use the -hierarchical matching scheme to return a collection of cells or pins in all hierarchies of your design.

For example, the command get\_pins -hierarchical \*|datac returns all the datac pins for all registers in your design. However, the command get\_pins -hierarchical \*|\*|datac returns an empty collection because more than one pipe character (|) is not supported.

The -compatibility\_mode option returns collections matching wildcard strings through any number of hierarchy levels. For example, an asterisk can match a pipe character when using -compatibility\_mode.

# Identifying the Quartus II Software Executable from the SDC File

To identify which Quartus II software executable is currently running you can use the \$::TimeQuestInfo(nameofexecutable) variable from within an .sdc. Example 7–5 shows how to specify different SDC constraints for a specific Quartus II software executable.

Example 7–5. Identifying the Quartus II Executable

```

#Identify which executable is running:

set current_exe $::TimeQuestInfo(nameofexecutable)

if { [string equal $current_exe "quartus_fit"] } {

#Apply .sdc assignments for Fitter executable here

} else {

#Apply .sdc assignments for non-Fitter executables here

}

if { ! [string equal "quartus_sta" $::TimeQuestInfo(nameofexecutable)] } {

#Apply .sdc assignments for non-TimeQuest executables here

} else {

#Apply .sdc assignments for TimeQuest executable here

```

Examples of different executable names are quartus\_map for Analysis & Synthesis, quartus\_fit for Fitter, and quartus\_sta for the TimeQuest analyzer.

# **Locating Timing Paths in Other Tools**

You can locate paths and elements from the TimeQuest analyzer to other tools in the Quartus II software. Use the **Locate Path** command in the TimeQuest analyzer GUI or the locate command.

? For more information about locating paths from the TimeQuest analyzer, refer to Viewing Timing Analysis Results and locate in Quartus II Help.

Example 7–6 shows how to locate ten paths from TimeQuest analyzer to the Chip Planner and locate all data ports in the Technology Map Viewer.

#### Example 7–6. Locating from the TimeQuest Analyzer

```

# Locate in the Chip Planner all of the nodes in ten paths with the

longest delay

locate [get_path -npaths 10] -chip

# locate all ports that begin with data to the Technology Map Viewer

locate [get_ports data*] -tmv

```

# **Design Constraints: An Example**

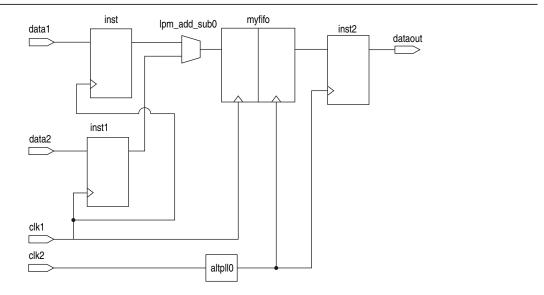

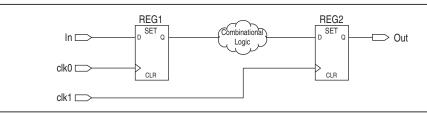

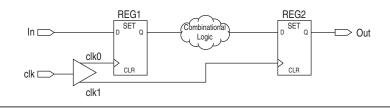

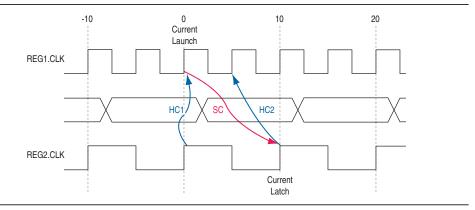

Figure 7–4 shows an example circuit including two clocks, a phase-locked loop (PLL), and other common synchronous design elements.

Figure 7–4. TimeQuest Constraint Example

Example 7–7 shows an **.sdc** file containing basic constraints for the circuit in Figure 7–4.

#### Example 7–7. Example Basic SDC Constraints

```

# Create clock constraints

create clock -name clockone -period 10.000 [get ports {clk1}]

create clock -name clocktwo -period 10.000 [get ports {clk2}]

# Create virtual clocks for input and output delay constraints

create clock -name clockone ext -period 10.000

create clock -name clockone_ext -period 10.000

derive_pll_clocks

# derive clock uncertainty

derive_clock_uncertainty

# Specify that clockone and clocktwo are unrelated by assinging

# them to seperate asynchronus groups

set clock groups \

-asynchronous \

-group {clockone} \

-group {clocktwo \

altpll0|altpll_component|auto_generated|pll1|clk[0]}]

# set input and output delays

set_input_delay -clock { clockone_ext } -max 4 [get_ports {data1}]

set_input_delay -clock { clockone_ext } -min -1 [get_ports {data1}]

set_input_delay -clock { clockone_ext } -max 4 [get_ports {data2}]

set_input_delay -clock { clockone_ext } -min -1 [get_ports {data2}]

set_output_delay -clock { clocktwo_ext } -max 6 [get_ports {dataout}]

set output delay -clock { clocktwo ext } -min -3 [get ports {dataout}]

```

The **.sdc** in Example 7–7 contains the following basic constraints you should include for most designs:

- Definitions of clockone and clocktwo as base clocks, and assignment of those settings to nodes in the design.

- Definitions of clockone\_ext and clocktwo\_ext as virtual clocks, which represent clocks driving external devices interfacing with the FPGA.

- Automated derivation of generated clocks on PLL outputs.

- Derivation of clock uncertainty.

- Specification of two clock groups, the first containing clockone and its related clocks, the second containing clocktwo and its related clocks, and the third group containing the output of the PLL. This specification overrides the default analysis of all clocks in the design as related to each other. For more information about asynchronous clock groups, refer to "Asynchronous Clock Groups" on page 7–22.

- Specification of input and output delays for the design.

The following sections describe each of these constraint types in detail.

# **Creating Clocks and Clock Constraints**

To ensure accurate static timing analysis results, you must specify all clocks and any associated clock characteristics in your design. The TimeQuest analyzer supports SDC commands that accommodate various clocking schemes and clock characteristics.

The TimeQuest analyzer supports the following types of clocks:

- Base clocks

- Virtual clocks

- Multifrequency clocks

- Generated clocks

Clocks are used to specify requirements for synchronous transfers and guide the Fitter optimization algorithms to achieve the best possible placement for your design.

Specify clock constraints first in the **.sdc** because other constraints may reference previously defined clocks. The TimeQuest analyzer reads SDC constraints and exceptions from top to bottom in the file.

## **Creating Base Clocks**

Base clocks are the primary input clocks to the device. Unlike clocks from PLLs that are generated in the device, base clocks are generated by off-chip oscillators or forwarded from an external device. Define base clocks first because generated clocks and other constraints often reference base clocks.

To create clock settings for the signal from any register, port, or pin, use the create\_clock command. You can create each clock with unique characteristics.

Example 7–8 shows how to create a 10 ns clock with a 50% duty cycle that is phase shifted by 90 degrees applied to port clk\_sys.

Example 7–8. 100 MHz Shifted by 90 Degrees Clock Creation

create\_clock -period 10 -waveform { 2.5 7.5 } [get\_ports clk\_sys]

Use the create\_clock command to constrain all primary input clocks. The target for the create\_clock command is usually a pin. To specify the pin as the target, use the get\_ports command. Example 7–9 shows how to specify a 100 MHz requirement on a clk\_sys input clock port.

#### Example 7–9. create\_clock Command

create\_clock -period 10 -name clk\_sys [get\_ports clk\_sys]

You can apply multiple clocks on the same clock node with the -add option. Example 7–10 shows how to specify that two oscillators drive the same clock port on the device.

Example 7–10. Two Oscillators Driving the Same Clock Port

```

create_clock -period 10 -name clk_100 [get_ports clk_sys]

create_clock -period 5 -name clk_200 [get_ports clk_sys] -add

```

⑦ For more information about the create\_clock and get\_ports commands—including full syntax information, options, and example usage—refer to *create\_clock* and *get\_ports* in Quartus II Help.

# **Creating Virtual Clocks**

A virtual clock is a clock that does not have a real source in the design or that does not interact directly with the design. Virtual clocks are used in most I/O constraints, they represent the clock at the external device connected to the FPGA.

To create virtual clocks, use the create\_clock command with no value specified for the <*targets*> option. Use virtual clocks for the reference clocks of set\_input\_delay and set\_output\_delay constraints.

Example 7–11 shows how to create a 10 ns virtual clock. The example is a virtual clock because no target is specified.

#### Example 7–11. Create Virtual Clock

create\_clock -period 10 -name my\_virt\_clk

⑦ For more information about the set\_input\_delay, and set\_output\_delay commands—including full syntax information, options, and example usage—refer to set\_input\_delay, and set\_output\_delay in Quartus II Help.

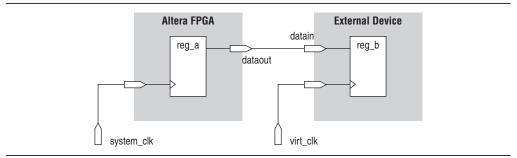

Figure 7–5 shows a design where a virtual clock is required for the TimeQuest analyzer to properly analyze the relationship between the external register and the registers in the design. Because the oscillator, virt\_clk, does not interact with the Altera device, but acts as the clock source for the external register, you must declare the clock as a virtual clock. After you create the virtual clock, you can perform a register-to-register analysis between the register in the Altera device and the register in the external device.

#### Figure 7–5. Virtual Clock Board Topology

Example 7–12 shows how to create a 10 ns virtual clock named virt\_clk with a 50% duty cycle where the first rising edge occurs at 0 ns. The virtual clock is then used as the clock source for an output delay constraint.

#### Example 7–12. Virtual Clock Example

```

#create base clock for the design

create_clock -period 5 [get_ports system_clk]

#create the virtual clock for the external register

create_clock -period 10 -name virt_clk

#set the output delay referencing the virtual clock

set_output_delay -clock virt_clk -max 1.5 [get_ports dataout]

set_output_delay -clock virt_clk -min 0.0 [get_ports dataout]

```

## I/O Interface Uncertainty

Virtual clocks are recommended for I/O constraints because the derive\_clock\_uncertainty command can add different uncertainty values on clocks that interface with an external I/O port than uncertainty values between register paths fed by a clock inside the FPGA.

To specify I/O interface uncertainty, you must create a virtual clock and constrain the input and output ports with the set\_input\_delay and set\_output\_delay commands that reference the virtual clock. When the set\_input\_delay or set\_output\_delay commands reference a clock port or PLL output, the virtual clock allows the derive\_clock\_uncertainty command to apply separate clock uncertainties for internal clock transfers and I/O interface clock transfers

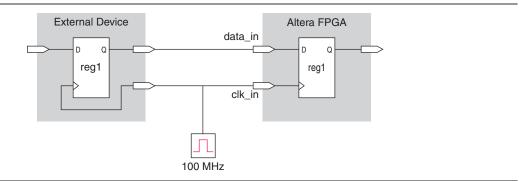

Create the virtual clock with the same properties as the original clock that is driving the I/O port. Figure 7–6 shows a typical input I/O interface with clock specifications.

#### Figure 7–6. I/O Interface Clock Specifications

Example 7–13 shows the SDC commands to constrain the I/O interface shown in Figure 7–6.

#### Example 7–13. SDC Commands to Constrain the I/O Interface

```

# Create the base clock for the clock port

create_clock -period 10 -name clk_in [get_ports clk_in]

# Create a virtual clock with the same properties of the base clock

# driving the source register

create_clock -period 10 -name virt_clk_in

# Create the input delay referencing the virtual clock and not the base

# clock

# DO NOT use set_input_delay -clock clk_in <delay value>

# [get_ports data_in]

set_input_delay -clock virt_clk_in <delay value> [get_ports data_in]

```

For more information about clock uncertainty and clock transfers, refer to "Clock Uncertainty" on page 7–23

### **Creating Multifrequency Clocks**

You must create a multifrequency clock if your design has more than one clock source feeding a single clock node in your design. The additional clock may act as a low-power clock, with a lower frequency than the primary clock. If your design uses multifrequency clocks, use the set\_clock\_groups command to define clocks that are exclusive. For more information about creating exclusive clock groups, refer to "Creating Clock Groups" on page 7–21.

To create multifrequency clocks, use the create\_clock command with the -add option to create multiple clocks on a clock node. Example 7–14 shows how to create a 10 ns clock applied to clock port clk, and then add an additional 15 ns clock to the same clock port. The TimeQuest analyzer uses both clocks when it performs timing analysis.

Example 7–14. Multifrequency Clock Example

```

create_clock -period 10 -name clock_primary -waveform { 0 5 } \

[get_ports clk]

create_clock -period 15 -name clock_secondary -waveform { 0 7.5 } \

[get_ports clk] -add

```

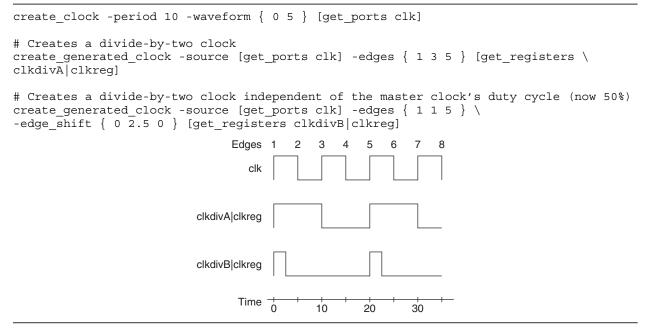

## **Creating Generated Clocks**

Generated clocks are applied in the design when you modify the properties of a source synchronous clock signal, including phase, frequency, offset, and duty cycle. In the **.sdc**, generated clocks, which can be the outputs of PLLs or register clock dividers, are constrained after all base clocks. Generated clocks capture all clock delays and clock latency where the generated clock target is defined, ensuring that all base clock properties are accounted for in the generated clock.

Use the create\_generated\_clock command to constrain generated clocks in your design. The source of the create\_generated\_clock command should be a node in your design and not a previously constrained clock.

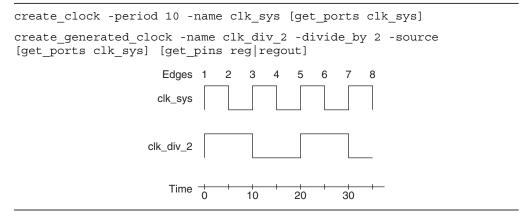

A common form of generated clock is a clock divider. Example 7–15 creates a base clock, clk\_sys, then defines a generated clock clk\_div\_2, which is the clock frequency of clk\_sys divided by two.

Example 7-15. Clock Divider

When you use the create\_generated\_clock command, the -source option specifies a node with a clock used as a reference for your generated clock. Best practice is to specify the input clock pin of the target node for your new generated clock. You can also specify the target node of the reference clock. In Example 7–15, the -source option specifies the clock port clk feeding the clock pin of register reg.

If you have multiple base clocks feeding a node that is the source for a generated clock, you must define multiple generated clocks. Each generated clock is associated to one base clock using the -master\_clock option in each generated clock statement.

The TimeQuest analyzer provides the derive\_pll\_clocks command to automatically generate clocks for all PLL clock outputs. The properties of the generated clocks on the PLL outputs match the properties defined for the PLL. For more information about deriving PLL clock outputs, refer to "Deriving PLL Clocks" on page 7–19.

⑦ For more information about the create\_generated\_clock and derive\_pll\_clocks commands—including for full syntax information, options, and example usage—refer to create\_generate\_clock and derive\_pll\_clocks in Quartus II Help.

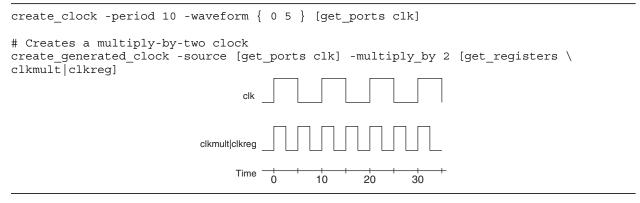

The inverse of a clock divider is a clock multiplier. Figure 7–7 shows the effect of applying a multiplication factor to the generated clock.

#### Figure 7–7. Multiplying a Generated Clock

An uncommon but useful type of generated clock is one with shifted edges. Figure 7–8 shows how to modify the generated clock by defining and shifting the edges.

#### Figure 7–8. Edge Shifting a Generated Clock

⑦ For information about creating generated clocks, refer to create\_generated\_clocks and Specifying Timing Constraints and Exceptions in Quartus II Help.

## **Deriving PLL Clocks**

Use the derive\_pll\_clocks command to direct the TimeQuest analyzer to automatically search the timing netlist for all unconstrained PLL output clocks. The derive\_pll\_clocks command automatically creates generated clocks on the outputs of every PLL by calling the create\_generated\_clock command. The source for the create\_generated\_clock command is the input clock pin of the PLL. Example 7–16 shows the command to create a base clock for the PLL input clock port and call derive\_pll\_clocks to create PLL output clocks.

#### Example 7–16. Create Base Clock for PLL input Clock Ports

```

create_clock -period 10.0 -name fpga_sys_clk [get_ports fpga_sys_clk]

derive_pll_clocks

```

- If your design contains LVDS transmitters, LVDS receivers, or transceivers, Altera recommends using the derive\_pll\_clocks command. The command automatically constrains this logic in your design by adding the appropriate multicycle constraints to account for any deserialization factors.

- ⑦ For more information about the derive\_pll\_clocks command—including full syntax information, options, and example usage—refer to *derive\_pll\_clocks* and *Derive PLL Clocks* in Quartus II Help.

You can include the derive\_pll\_clocks command in your .sdc, which automatically detects any changes to the PLL settings. Each time the TimeQuest analyzer reads your .sdc, the appropriate create\_generated\_clocks command is generated for the PLL output clock pin.

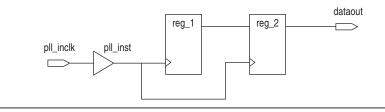

Figure 7–9 shows a simple PLL design with a register-to-register path.

Example 7–17 shows the messages generated by the TimeQuest analyzer when you use the derive\_pll\_clocks command to automatically constrain the PLL for the design shown in Figure 7–9.

#### Example 7–17. derive\_pll\_clocks Command Messages

Figure 7–9. Simple PLL Design

```

Info:

Info: Deriving PLL Clocks:

Info: create_generated_clock -source

pll_inst|altpll_component|pll|inclk[0] -divide_by 2 -name

pll_inst|altpll_component|pll|clk[0]

pll_inst|altpll_component|pll|clk[0]

Info:

```

The input clock pin of the PLL is the node

pll\_inst|altpll\_component|pll|inclk[0] is used for the -source option. The name

of the output clock of the PLL is the PLL output clock node,

pll\_inst|altpll\_component|pll|clk[0].

If the PLL is in clock switchover mode, multiple clocks are created for the output clock of the PLL; one for the primary input clock (for example, inclk[0]), and one for the secondary input clock (for example, inclk[1]). You should create exclusive clock groups for the primary and secondary output clocks.

For more information about creating exclusive clock groups, refer to "Creating Clock Groups" on page 7–21.

# **Automatically Detecting Clocks and Creating Default Clock Constraints**

To automatically create clocks for all clock nodes in your design, use the derive\_clocks command. The derive\_clocks command is equivalent to using the create\_clock command for each register or port feeding the clock pin of a register. The derive\_clocks command creates clock constraints on ports or registers to ensure every register in your design has a clock constraints, and it applies one period to all base clocks in your design.

If there are no clock constraints in your design, the TimeQuest analyzer automatically creates default clock constraints for all detected unconstrained clock nodes to provide a complete clock analysis. The TimeQuest analyzer automatically creates clocks only when all synchronous elements have no associated clocks. For example, the TimeQuest analyzer does not create a default clock constraint if your design contains two clocks and you assigned constraints to one of the clocks. However, if you do not assign constraints to either clock, then the TimeQuest analyzer creates a default clock constraint.

Example 7–18 shows how the TimeQuest analyzer creates a base clock with a 1 GHz requirement for unconstrained clock nodes.

#### Example 7–18. Create Base Clock for Unconstrained Clock Nodes

derive\_clocks -period 1

Do not use the derive\_clocks command for final timing sign-off; instead, you should create clocks for all clock sources with the create\_clock and create\_generated\_clock commands. If your design has more than a single clock, the derive\_clocks command constrains all the clocks to the same specified frequency. To achieve a thorough and realistic analysis of your design's timing requirements, you should make individual clock constraints for all clocks in your design.

You can also use the command derive\_pll\_clocks -create\_base\_clocks to create the input clocks for all PLL inputs automatically.

⑦ For more information about the derive\_clocks command—including full syntax information, options, and example usage—refer to *derive\_clocks* in Quartus II Help.

## **Creating Clock Groups**

The TimeQuest analyzer assumes all clocks are related unless constrained otherwise. To specify clocks in your design that are exclusive or asynchronous, use the set\_clock\_groups command. The set\_clock\_groups command cuts timing between clocks in different groups, and performs the same analysis regardless of whether you specify -exclusive or -asynchronous.

For more information about the set\_clock\_groups command—including full syntax information, options, and example usage—refer to set\_clock\_groups in Quartus II Help.

### **Exclusive Clock Groups**

Use the -exclusive option to declare that two clocks are mutually exclusive. You may want to declare clocks as mutually exclusive when multiple clocks are created on the same node or for multiplexed clocks. For example, a port can be clocked by either a 25-MHz or a 50-MHz clock. To constrain this port, you should create two clocks on the port, and then create clock groups to declare that they cannot coexist in the design at the same time. Declaring the clocks as mutually exclusive eliminates any clock transfers that may be derived between the 25-MHz clock and the 50-MHz clock. Example 7–19 shows how to create mutually exclusive clock groups.

#### Example 7–19. Create Mutually Exclusive Clock Groups

```

create_clock -period 40 -name clk_A [get_ports {port_A}]

create_clock -add -period 20 -name clk_B [get_ports {port_A}]

set_clock_groups -exclusive -group {clk_A} -group {clk_B}

```

A group is defined with the -group option. The TimeQuest analyzer excludes the timing paths between clocks for each of the separate groups.

If you apply multiple clocks to the same port, use the set\_clock\_groups command with the -exclusive option to place the clocks into separate groups and declare that the clocks are mutually exclusive. The clocks cannot physically exist in your design at the same time.

### **Asynchronous Clock Groups**

Use the -asynchronous option to create asynchronous clock groups. Clocks contained within an asynchronous clock group are considered asynchronous to clocks in other clock groups; however, any clocks within a clock group are considered synchronous to each other.

For example, if your design has three clocks, clk\_A, clk\_B, and clk\_C, and you establish that clk\_A and clk\_B are related to each other, but clock clk\_C operates completely asynchronously, you can set up clock groups to define the clock behavior. If set\_clock\_groups is used with only one group, the clocks in that group are asynchronous with all other clocks in the design. For example, you can create a clock group containing only clk\_C to ensure that clk\_A and clk\_B are synchronous with each other and asynchronous with clk\_C. Because clk\_C is the only clock in the constraint, it is asynchronous with every other clock in the design.

Example 7–20 shows how to create a clock group containing clocks clk\_A and clk\_B and a second unrelated clock group containing clk\_C.

#### Example 7–20. Create Asynchronous Clock Groups

set\_clock\_groups -asynchronous -group {clk\_A clk\_B} -group {clk\_C}

For more information about the set\_clock\_groups command—including full syntax information, options, and example usage—refer to set\_clock\_groups in Quartus II Help.

# **Accounting for Clock Effect Characteristics**

The clocks you create with the TimeQuest analyzer are ideal clocks that do not account for any board effects. You can account for clock effect characteristics with clock latency and clock uncertainty.

### **Clock Latency**

There are two forms of clock latency, clock source latency and clock network latency. Source latency is the propagation delay from the origin of the clock to the clock definition point (for example, a clock port). Network latency is the propagation delay from a clock definition point to a register's clock pin. The total latency at a register's clock pin is the sum of the source and network latencies in the clock path.

To specify source latency to any clock ports in your design, use the set\_clock\_latency command.

- The TimeQuest analyzer automatically computes network latencies; therefore, you only can characterize source latency with the set\_clock\_latency command. You must use the -source option.

- ⑦ For more information about the set\_clock\_latency command—including full syntax information, options, and example usage—refer to set\_clock\_latency in Quartus II Help.f

### **Clock Uncertainty**

The TimeQuest analyzer accounts for uncertainty clock effects for three types of clock-to-clock transfers; intraclock transfers, interclock transfers, and I/O interface clock transfers.

- Intraclock transfers occur when the register-to-register transfer takes place in the core of the device and the source and destination clocks come from the same PLL output pin or clock port.

- Interclock transfers occur when a register-to-register transfer takes place in the core of the device and the source and destination clocks come from a different PLL output pin or clock port.

- I/O interface clock transfers occur when data transfers from an I/O port to the core of the device or from the core of the device to the I/O port.

To manually specify clock uncertainty, or skew, for clock-to-clock transfers, use the set\_clock\_uncertainty command. You can specify the uncertainty separately for setup and hold, and you can specify separate rising and falling clock transitions. The TimeQuest analyzer subtracts setup uncertainty from the data required time for each applicable path and adds the hold uncertainty to the data required time for each applicable path.

To automatically apply interclock, intraclock, and I/O interface uncertainties, use the derive\_clock\_uncertainty command. The TimeQuest analyzer automatically applies clock uncertainties to clock-to-clock transfers in the design, and calculates both setup and hold uncertainties for each clock-to-clock transfer.

Any clock uncertainty constraints applied to source and destination clock pairs with the set\_clock\_uncertainty command have a higher precedence than the clock uncertainties derived with the derive\_clock\_uncertainty command for the same source and destination clock pairs. For example, if you use the set\_clock\_uncertainty command to set clock uncertainty between clka and clkb, the TimeQuest analyzer ignores the values for the clock transfer calculated with the derive\_clock\_uncertainty command. The TimeQuest analyzer reports the values calculated with the derive\_clock\_uncertainty command even if they are not used.

Use set\_clock\_uncertainty or derive\_clock\_uncertainty with the -overwrite option to overwrite previously applied clock uncertainty assignments. Use set\_clock\_uncertainty or derive\_clock\_uncertainty with the -add option to apply additional clock uncertainty to previously applied clock uncertainty. Use the remove\_clock\_uncertainty command to remove previous clock uncertainty assignments.

? For more information about the set\_clock\_uncertainty, derive\_clock\_uncertainty, and remove\_clock\_uncertainty commands—including full syntax information, options, and example usage—refer to set\_clock\_uncertainty, remove\_clock\_uncertainty and derive\_clock\_uncertainty, in Quartus II Help.

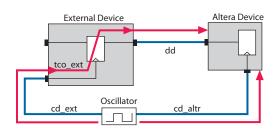

# **Creating I/O Requirements**

The TimeQuest analyzer reviews setup and hold relationships for designs in which an external source interacts with a register internal to the design. The TimeQuest analyzer supports input and output external delay modeling with the set\_input\_delay and set\_output\_delay commands. You can specify the clock and minimum and maximum arrival times relative to the clock.

You must specify timing requirements, including internal and external timing requirements, before you fully analyze a design. With external timing requirements specified, the TimeQuest analyzer verifies the I/O interface, or periphery of the device, against any system specification.

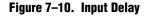

# **Input Constraints**

Input constraints allow you to specify all the external delays feeding into the device. Specify input requirements for all input ports in your design.

You can use the set\_input\_delay command to specify external input delay requirements. Use the -clock option to reference a virtual clock. Using a virtual clock allows the TimeQuest analyzer to correctly derive clock uncertainties for interclock and intraclock transfers. The virtual clock defines the launching clock for the input port. The TimeQuest analyzer automatically determines the latching clock inside the device that captures the input data, because all clocks in the device are defined. Figure 7–10 shows an example of an input delay referencing a virtual clock.

Equation 7–1 shows a typical input delay calculation.

#### Equation 7–1. Input Delay Calculation

```

\begin{aligned} \text{input delay}_{\text{MAX}} &= (\text{cd}_{\text{ext}_{\text{MAX}}} - \text{cd}_{\text{altr}_{\text{MIN}}}) + \text{tco}_{\text{ext}_{\text{MAX}}} + \text{dd}_{\text{MAX}} \\ \text{input delay}_{\text{MIN}} &= (\text{cd}_{\text{ext}_{\text{MIN}}} - \text{cd}_{\text{altr}_{\text{MAX}}}) + \text{tco}_{\text{ext}_{\text{MIN}}} + \text{dd}_{\text{MIN}} \end{aligned}

```

# **Output Constraints**

Output constraints allow you to specify all external delays from the device for all output ports in your design.

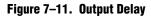

You can use the set\_output\_delay command to specify external output delay requirements. Use the -clock option to reference a virtual clock. The virtual clock defines the latching clock for the output port. The TimeQuest analyzer automatically determines the launching clock inside the device that launches the output data, because all clocks in the device are defined. Figure 7–11 shows an example of an output delay referencing a virtual clock.

Equation 7–2 shows a typical output delay calculation.

#### Equation 7–2. output Delay Calculation

```

\begin{array}{l} \text{output delay}_{MAX} \ = \ dd_{MAX} + tsu\_ext + (cd\_altr_{MAX} - cd\_ext_{MIN}) \\ \text{output delay}_{MIN} \ = \ (dd_{MIN} + th\_ext + (cd\_altr_{MIN} - cd\_ext_{MAX})) \end{array} \end{array}

```

⑦ For more information about the set\_input\_delay and set\_output\_delay commands—including full syntax information, options, and example usage—refer to set\_input\_delay and set\_output\_delay in Quartus II Help.

# **Creating Delay and Skew Constraints**

The TimeQuest analyzer supports the Synopsys Design Constraint format for constraining timing for the ports in your design. These constraints allow the TimeQuest analyzer to perform a system static timing analysis that includes not only the device internal timing, but also any external device timing and board timing parameters.

### Advanced I/O Timing and Board Trace Model Delay

The TimeQuest analyzer can use advanced I/O timing and board trace model assignments to model I/O buffer delays in your design.

If you change any advanced I/O timing settings or board trace model assignments, recompile your design before you analyze timing, or use the -force\_dat option to force delay annotation when you create a timing netlist. Example 7–21 shows how to force delay annotation when creating a timing netlist.

#### Example 7–21. Forcing Delay Annotation

create\_timing\_netlist -force\_dat 🕶

- ? For more information about using advanced I/O timing, refer to Using Advanced I/O Timing in Quartus II Help.

- For more information about advanced I/O timing, refer to the I/O Management chapter in volume 2 of the Quartus II Handbook.

### **Maximum Skew**

To specify the maximum path-based skew requirements for registers and ports in the design and report the results of maximum skew analysis, use the set\_max\_skew command in conjunction with the report max skew command.

By default, the set\_max\_skew command excludes any input or output delay constraints.

⑦ For more information about the set\_max\_skew and report\_max\_skew commands including full syntax information, options, and example usage—refer to set\_max\_skew report\_max\_skew in Quartus II Help.

Volume 3: Verification

# **Creating Timing Exceptions**

Timing exceptions in the TimeQuest analyzer provide a way to modify the default timing analysis behavior to match the analysis required by your design. Specify timing exceptions after clocks and input and output delay constraints because timing exceptions can modify the default analysis.

## Precedence

If a conflict of node names occurs between timing exceptions, the following order of precedence applies:

- 1. False path

- 2. Minimum delays and maximum delays

- 3. Multicycle path

The false path timing exception has the highest precedence. Within each category, assignments to individual nodes have precedence over assignments to clocks. Finally, the remaining precedence for additional conflicts is order-dependent, such that the assignments most recently created overwrite, or partially overwrite, earlier assignments.

### **False Paths**

Specifying a false path in your design removes the path from timing analysis. Use the set\_false\_path command to specify false paths in your design. You can specify either a point-to-point or clock-to-clock path as a false path. For example, a path you should specify as false path is a static configuration register that is written once during power-up initialization, but does not change state again. Although signals from static configuration registers often cross clock domains, you may not want to make false path exceptions to a clock-to-clock path, because some data may transfer across clock domains. However, you can selectively make false path exceptions from the static configuration register to all endpoints.

Example 7–22 shows how to make false path exceptions from all registers beginning with A to all registers beginning with B.

#### Example 7–22. False Path

set\_false\_path -from [get\_pins A\*] -to [get\_pins B\*]

The TimeQuest analyzer assumes all clocks are related unless you specify otherwise. The "Creating Clock Groups" on page 7–21 describes how you can use clock groups. Clock groups are a more efficient way to make false path exceptions between clocks, compared to writing multiple set\_false\_path exceptions between every clock transfer you want to eliminate.

? For more information about the set\_false\_path command—including full syntax information, options, and example usage—refer to set\_false\_path in Quartus II Help.

## **Minimum and Maximum Delays**

To specify an absolute minimum or maximum delay for a path, use the set\_min\_delay command or the set\_max\_delay commands, respectively. Specifying

minimum and maximum delay directly overwrites existing setup and hold

relationships with the minimum and maximum values.

Use the set\_max\_delay and set\_min\_delay commands to create constraints for asynchronous signals that do not have a specific clock relationship in your design, but require a minimum and maximum path delay. You can create minimum and maximum delay exceptions for port-to-port paths through the device without a register stage in the path. If you use minimum and maximum delay exceptions to constrain the path delay, specify both the minimum and maximum delay of the path; do not constrain only the minimum or maximum value.

If the source or destination node is clocked, the TimeQuest analyzer takes into account the clock paths, allowing more or less delay on the data path. If the source or destination node has an input or output delay, that delay is also included in the minimum or maximum delay check.

If you specify a minimum or maximum delay between timing nodes, the delay applies only to the path between the two nodes. If you specify a minimum or maximum delay for a clock, the delay applies to all paths where the source node or destination node is clocked by the clock.

You can create a minimum or maximum delay exception for an output port that does not have an output delay constraint. You cannot report timing for the paths associated with the output port; however, the TimeQuest analyzer reports any slack for the path in the setup summary and hold summary reports. Because there is no clock associated with the output port, no clock is reported for timing paths associated with the output port.

- To report timing with clock filters for output paths with minimum and maximum delay constraints, you can set the output delay for the output port with a value of zero. You can use an existing clock from the design or a virtual clock as the clock reference.

- ? For more information about the set\_min\_delay, and set\_max\_delay, commands including full syntax information, options, and example usage—refer to set\_min\_delay, and set\_max\_delay, in Quartus II Help.

## **Delay Annotation**

To modify the default delay values used during timing analysis, use the set\_annotated\_delay and set\_timing\_derate commands. You must update the timing netlist to see the results of these commands

To specify different operating conditions in a single **.sdc**, rather than having multiple **.sdc** files that specify different operating conditions, use the set\_annotated\_delay command with the -operating\_conditions option.

? For more information about the set\_annotated\_delay and set\_timing\_derate commands—including full syntax information, options, and example usage—refer to set\_annotated\_delay and set\_timing\_derate in Quartus II Help.

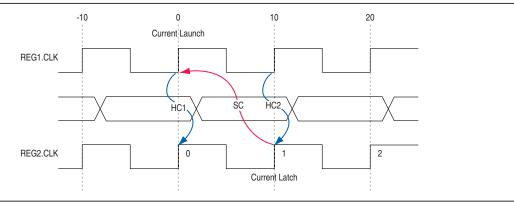

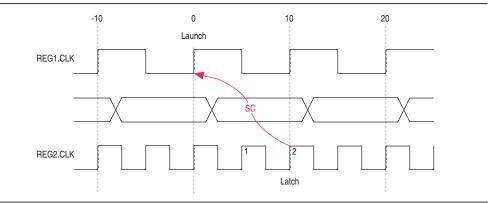

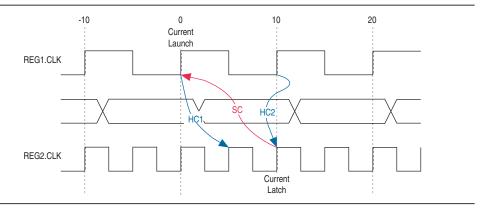

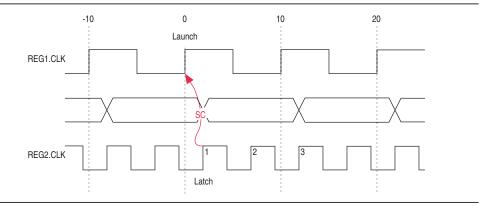

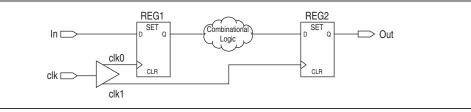

# **Multicycle Paths**

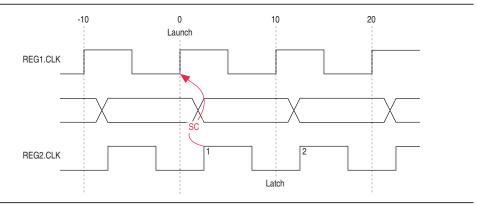

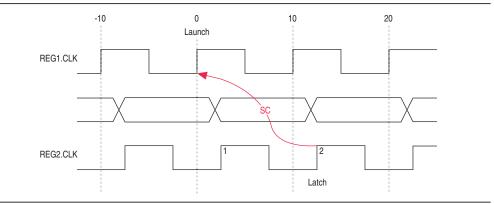

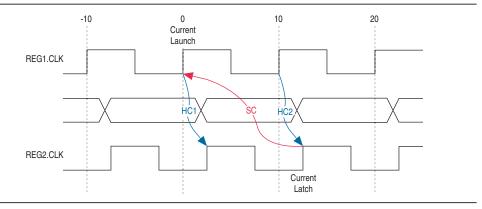

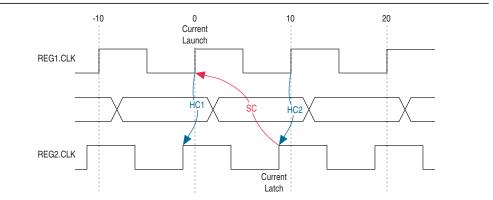

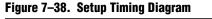

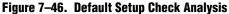

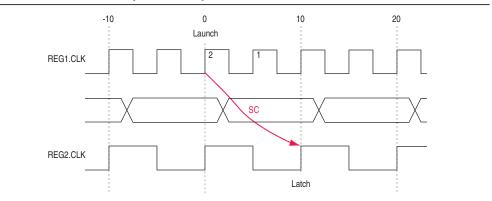

By default, the TimeQuest analyzer performs a single-cycle analysis, which is the most restrictive type of analysis. When analyzing a path, the setup launch and latch edge times are determined by finding the closest two active edges in the respective waveforms. For a hold analysis, the timing analyzer analyzes the path against two timing conditions for every possible setup relationship, not just the worst-case setup relationship. Therefore, the hold launch and latch times may be completely unrelated to the setup launch and latch edges. The TimeQuest analyzer does not report negative setup or hold relationships. When either a negative setup or a negative hold relationship is calculated, the TimeQuest analyzer moves both the launch and latch edges such that the setup and hold relationship becomes positive.

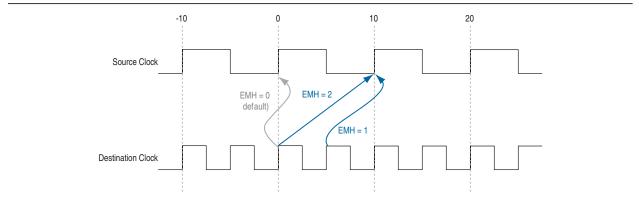

A multicycle constraint adjusts setup or hold relationships by the specified number of clock cycles based on the source (-start) or destination (-end) clock. An end setup multicycle constraint of 2 extends the worst-case setup latch edge by one destination clock period. If -start and -end values are not specified, the default constraint is - end.

Hold multicycle constraints are based on the default hold position (the default value is 0). An end hold multicycle constraint of 1 effectively subtracts one destination clock period from the default hold latch edge.

When the objects are timing nodes, the multicycle constraint only applies to the path between the two nodes. When an object is a clock, the multicycle constraint applies to all paths where the source node (-from) or destination node (-to) is clocked by the clock. When you adjust a setup relationship with a multicycle constraint, the hold relationship is adjusted automatically.

Table 7–4 shows the commands you can use to modify either the launch or latch edge times that the TimeQuest analyzer uses to determine a setup relationship or hold relationship.

| Command                                                     | Description of Modification                |

|-------------------------------------------------------------|--------------------------------------------|

| <pre>set_multicycle_path -setup -end <value></value></pre>  | Latch edge time of the setup relationship  |

| <pre>set_multicycle_path -setup -start<value></value></pre> | Launch edge time of the setup relationship |

| <pre>set_multicycle_path -hold -end <value></value></pre>   | Latch edge time of the hold relationship   |

| <pre>set_multicycle_path -hold -start <value></value></pre> | Launch edge time of the hold relationship  |

Table 7-4. Commands to Modify Edge Times

# **Common Multicycle Variations**

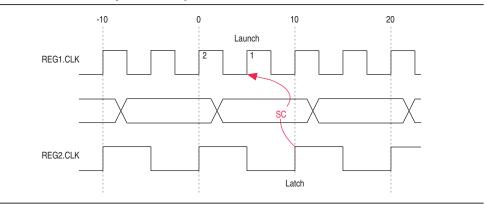

Multicycle exceptions adjust the timing requirements for a register-to-register path, allowing the Fitter to optimally place and route a design in a device. Multicycle exceptions also can reduce compilation time and improve the quality of results, and can be used to change timing requirements. Two common multicycle variations are relaxing setup to allow a slower data transfer rate, and altering the setup to account for a phase shift.

### **Relaxing Setup with set\_multicyle\_path**

A common type of multicycle exception occurs when the data transfer rate is slower than the clock cycle.

In this example, the source clock has a period of 10 ns, but a group of registers are enabled by a toggling clock, so they only toggle every other cycle. Since they are fed by a 10 ns clock, the TimeQuest analyzer reports a set up of 10 ns and a hold of 0 ns, However, since the data is transferring every other cycle, the relationships should be analyzed as if the clock were operating at 20 ns, which would result in a setup of 20 ns, while the hold remains 0 ns, in essence, extending the window of time when the data can be recognized.

Example 7–23 shows a pair of multicycle assignments that relax the setup relationship by specifying the -setup value of N and the -hold value as N-1. You must specify the hold relationship with a -hold assignment to prevent a positive hold requirement.

#### Example 7–23. Relaxing Setup while Maintaining Hold

```

set_multicycle_path -setup -from src_reg* -to dst_reg* 2

set_multicycle_path -hold -from src_reg* -to dst_reg* 1

```

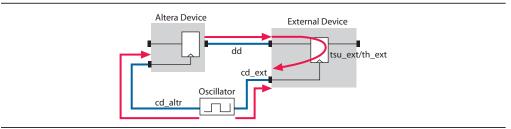

Figure 7–12 shows how the exception relaxes the setup by two or three cycles.

Figure 7–12. Relaxing Setup by Multiple Cycles

This pattern can be extended to create larger setup relationships in order to ease timing closure requirements. A common use for this exception is when writing to asynchronous RAM across an I/O interface. The delay between address, data, and a write enable may be several cycles. A multicycle exception to I/O ports can allow extra time for the address and data to resolve before the enable occurs.

Example 7–24 shows how a relaxing the setup by three cycles can be achieved.

#### Example 7–24. Three Cycle I/O Interface Exception

```

set_multicycle_path -setup -to [get_ports {SRAM_ADD[*] SRAM_DATA[*]} 3

set_multicycle_path -hold -to [get_ports {SRAM_ADD[*] SRAM_DATA[*]} 2

```

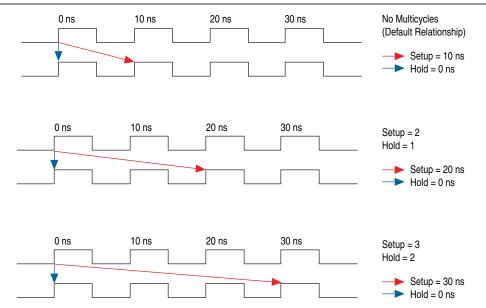

### **Accounting for a Phase Shift**

In this example, the design contains a PLL that performs a phase-shift on a clock whose domain exchanges data with domains that do not experience the phase shift. For example, when the destination clock is phase-shifted forward and the source clock is not, the default setup relationship becomes that phase-shift.

Example 7–25 shows a circumstance where a PLL phase-shifts one output forward by a small amount, for example 0.2 ns.

Example 7–25. Cross Domain Phase-Shift

```

create_generated_clock -source pll|inclk[0] -name pll|clk[0] pll|clk[0]

create_generated_clock -source pll|inclk[0] -name pll|clk[1] -phase 30 pll|clk[1]

```

The default setup relationship for this phase-shift is 0.2 ns, shown in Figure A, creating a scenario where the hold relationship is negative, which makes achieving timing closure nearly impossible.

Figure 7–13. Phase-Shifted Setup and Hold

Adding the constraint shown in Example Y allows the data to transfer to the following edge.

#### Example 7–26. Adjusting the Phase-Shift with a set\_multicycle\_path Constraint

```

set_multicycle_path -setup -from [get_clocks clk_a] -to [get_clocks clk_b] 2

```

The hold relationship is derived from the setup relationship, making a multicyle hold constraint unnecessary. For a more complete example refer to "Same Frequency Clocks with Destination Clock Offset" on page 7–44.

⑦ For more information about the set\_multicycle\_path command—including full syntax information, options, and example usage—refer to set\_multicycle\_path in Quartus II Help.

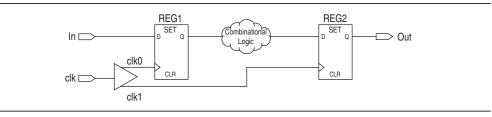

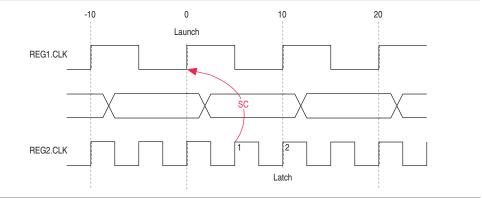

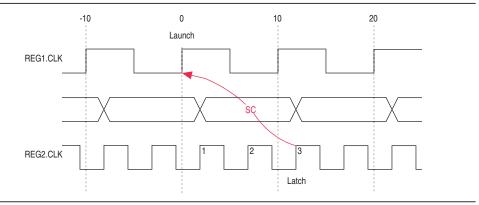

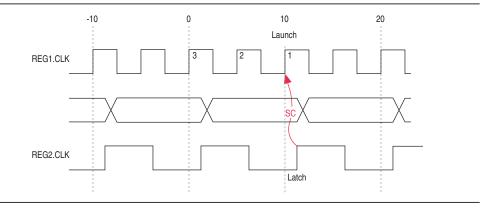

# **Multicycle Clock Setup Check and Hold Check Analysis**

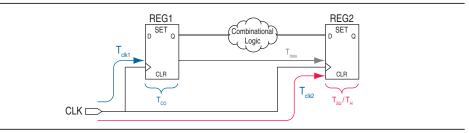

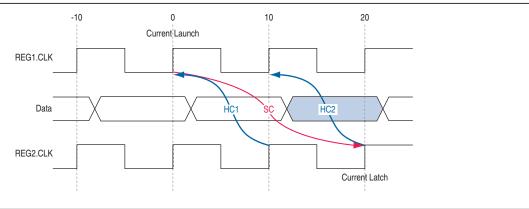

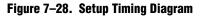

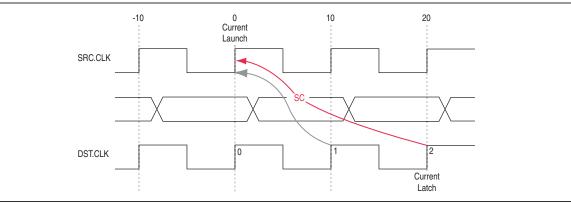

You can modify the setup and hold relationship when you apply a multicycle exception to a register-to-register path. Figure 7–14 shows a register-to-register path with various timing parameters labeled.

#### Figure 7–14. Register-to-Register Path

## **Multicycle Clock Setup**

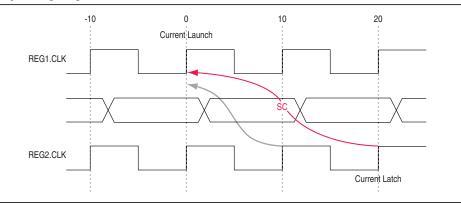

The setup relationship is defined as the number of clock periods between the latch edge and the launch edge. By default, the TimeQuest analyzer performs a single-cycle path analysis, which results in the setup relationship being equal to one clock period (latch edge – launch edge). Applying a multicycle setup assignment, adjusts the setup relationship by the multicycle setup value. The adjustment value may be negative.

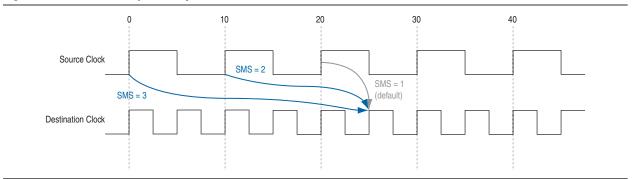

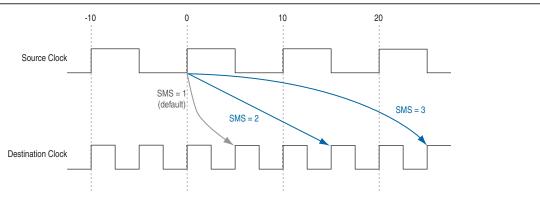

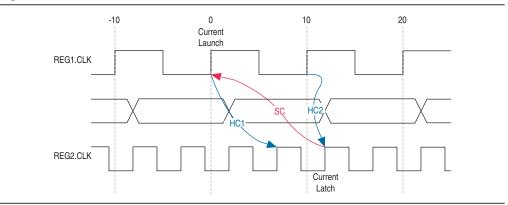

An end multicycle setup assignment modifies the latch edge of the destination clock by moving the latch edge the specified number of clock periods to the right of the determined default latch edge. Figure 7–15 shows various values of the end multicycle setup assignment and the resulting latch edge.

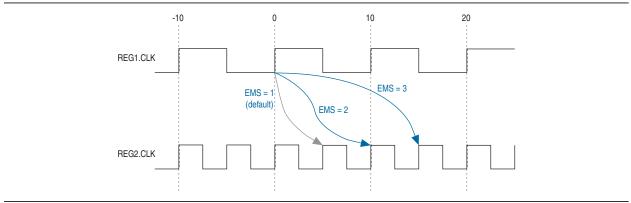

A start multicycle setup assignment modifies the launch edge of the source clock by moving the launch edge the specified number of clock periods to the left of the determined default launch edge. Figure 7–16 shows various values of the start multicycle setup assignment and the resulting launch edge.

Figure 7–16. Start Multicycle Setup Values

Figure 7–17 shows the setup relationship reported by the TimeQuest analyzer for the negative setup relationship shown in Figure 7–16.

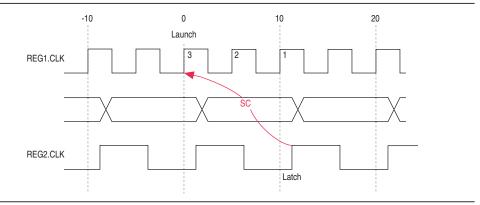

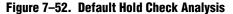

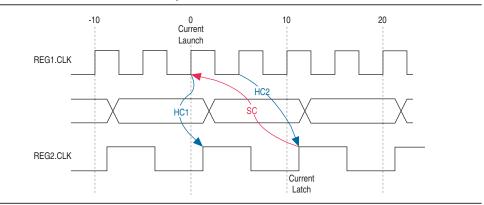

### **Multicycle Clock Hold**

The setup relationship is defined as the number of clock periods between the launch edge and the latch edge. By default, the TimeQuest analyzer performs a single-cycle path analysis, which results in the hold relationship being equal to one clock period (launch edge – latch edge). When analyzing a path, the TimeQuest analyzer performs two hold checks. The first hold check determines that the data launched by the current launch edge is not captured by the previous latch edge. The second hold check determines that the data launched by the current latch edge. The TimeQuest analyzer reports only the most restrictive hold check. Equation 7–3 shows the calculation that the TimeQuest analyzer performs to determine the hold check.

#### Equation 7–3. Hold Check

| hold check 1 = current launch edge – previous latch edge |  |

|----------------------------------------------------------|--|

| hold check 2 = next launch edge – current latch edge     |  |

If a hold check overlaps a setup check, the hold check is ignored.

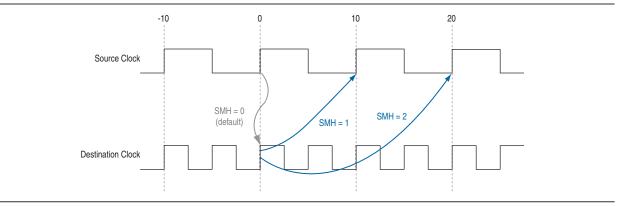

A start multicycle hold assignment modifies the launch edge of the destination clock by moving the latch edge the specified number of clock periods to the right of the determined default launch edge. Figure 7–18 shows various values of the start multicycle hold assignment and the resulting launch edge.

Figure 7–18. Start Multicycle Hold Values

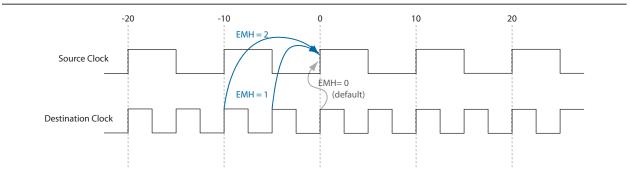

An end multicycle hold assignment modifies the latch edge of the destination clock by moving the latch edge the specific ed number of clock periods to the left of the determined default latch edge. Figure 7–19 shows various values of the end multicycle hold assignment and the resulting latch edge.

Figure 7–20 shows the hold relationship reported by the TimeQuest analyzer for the negative hold relationship shown in Figure 7–19.

## **Examples of Basic Multicycle Exceptions**

This section describes the following examples of combinations of multicycle exceptions:

- "Default Settings" on page 7–35

- "End Multicycle Setup = 2 and End Multicycle Hold = 0" on page 7–38