# Computer Capacitance Meter

Previously in D&ME we published an article for a capacitance meter add-on for the Beeb, Vic and Commodore micros. This appeared to be a very popular project, so our contributor has taken the original design and modified it for the Memotech 500 and 512 machines.

#### R.A. Penfold

ISSUE 4 of Digital And Micro Electronics contained a design for a digital capacitance meter for use in conjunction with the VIC-20, Commodore 64, and BBC Model B computers. This capacitance meter is based on the original design, but is for use with the Memotech MTX500 and MTX512 computers.

The present design has five measuring ranges with full scale values of: 65.535n, 655.35n, 6.5535u, 65.535u and 655.35u. The unit therefore covers most requirements with a wide range of values from a few picofarads to several hundred microfarads being catered for. Very large electrolytic capacitors are about the only types that cannot be accomodated, but these can usually be tested satisfactorily using an ordinary multimeter.

#### System Operation

With the original capacitance meter design it was possible to use the internal timer/counters to the computer to provide a clock frequency and a 16-bit counter where the value of the test component was registered. The Memotech computers have a built-in Z80A CTC four channel counter/timer, but this is only available for use with add-on devices in a very limited way, and is not usable in this application where full access to three of the four channels is required.

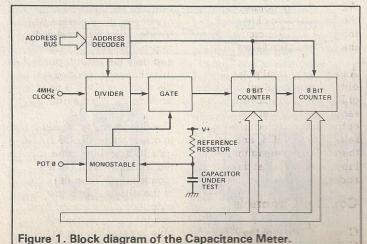

A Z80A CTC is therefore included in the capacitance meter unit. The block diagram of Figure 1 helps to explain

the way in which the unit functions.

A clock signal at a frequency of about 100kHz is required, and this is obtained from the 4MHz clock output of the computer using one channel of the Z80A CTC as a divide by 32 circuit. The clock signal is fed to a gate, and the output of the gate feeds into a 16-bit binary computer. In fact the computer is two 8-bit counters connected in series, and these are provided by two channels of the Z80A CTC device.

The Memotech computers have addresses from 16 to 31 available for add-ons, and the address decoder places the Z80A CTC in the input/output map at the four addresses from 16 to 19.

#### **Pulse Duration**

The gate is controlled by a monostable multivibrator. This is triggered by a short pulse from an output line of the user port, and the output pulse duration is controlled by a reference resistor and the capacitor under test. The higher the value of the test capacitor, the longer the pulse duration, and the greater the number of pulses that are allowed to pass through to the counter/timers.

By using a suitable clock frequency and reference resistance, the number in the counters at the end of the gate period will reflect the value of the capacitor with no more manipulation by the computer than simple binary to decimal conversion and placing the decimal point in the right place.

For example, on the 0 to 65.535n range a capacitor having a value of 62.5n would give an 0.5 second pulse. With a clock frequency of 125kHz (4MHz divided by 32) this would give a count of 62500 in the 16-bit counterr. Merely dividing this by 100 gives the correct reading of 62.500n.

In practice there are five switched reference resistors which give the unit its five measuring ranges.

The computer must obviously wait for the end of the gate pulse before the counter is read, and this hold-off is provided by a software loop. The resetting of the counters prior to taking a new measurement is also handled by the software. The program is made to loop continuously so that a constant stream of readings are taken and the diplayed value is updated about once per second.

#### The Circuit

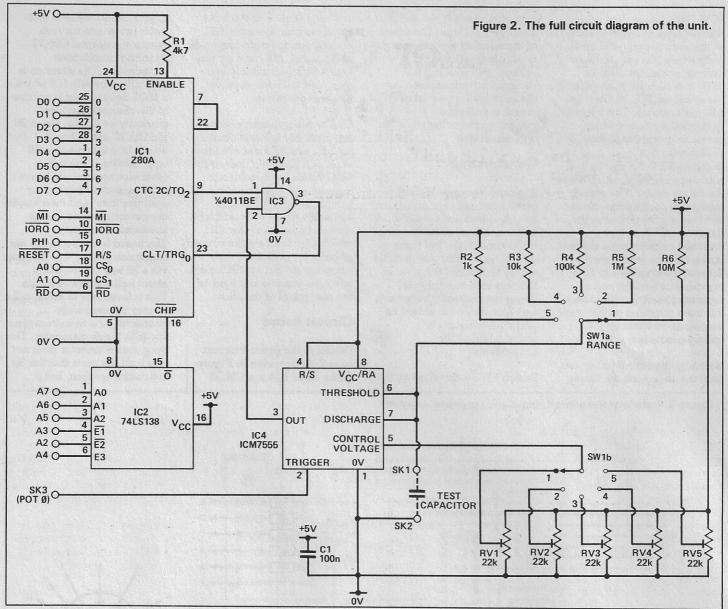

The circuit diagram of the capacitance meter appears in Figure 2.

As the Memotech computers are Z80A based there is no difficulty in interfacing them to the Z80A CTC. The data bus of

the computer and the Z80A CTC, IC1 are connected direct to one another. Similarly, some of the control bus lines such as RESET and IORO are connected direct to the relevant pins of IC1. Pin 13 is the "daisy chain" interrupt input, but as interrupts are not used in this case it is tied to the positive supply rail by R1. The register select pins of IC1, pins 18 and 19 are fed from address lines A0 and A1 so that the four registers of IC1, one for each channel appear at four contiguous addresses. The Memotech machines use a conventional Z80 input/output

mapping arrangement with

address lines being used,

giving 256 input/output

addresses from 0 to 255.

only the eight least significant

inputs, and A4 is connected to the positive chip select input.

A negative output pulse is obtained from output 0, pin 15 of IC2 when an address in the range 16 to 19 is accessed. This output is connected to the chip select input of IC1, and this IC

Address lines A2 to A7 are

decoded by IC2, which is a

decoder. Lines A5 to A7 are

A2 and A3 are connected to

the two negative chip select

fed to the three address inputs,

74LS 1383 to 8 line

addresses.

Counter Channels

therefore appears in the

Channels 0 to 2 of the Z80A CTC have an input terminal so

input/output map at these four

that pulses from an external source can be counted. All four channels have an output terminal that gives an output pulse when the counter reaches zero. All the counters are of the down counter variety incidentally. Channel 2 is used to provide the clock signal, and only the output, pin 9 of this channel is needed since the machine clock is used to provide the input signal.

The divided clock signal is fed to one input of CMOS NAND gate IC3, and the other input is fed from the output of the monostable. When the output of the monostable is low the output of IC3 is forced high, and the clock pulses are not able to pass through to the output. A high control signal

from the monostable enables the gate, and the clock pulses are able to pass through top the output. The pulses are actually inverted by IC3, but this is of no practical importance.

The output pulses from IC3 are fed to the input of the channel 0 counter. The underflow pulses from channel 0 are fed to the input of the channel 1 counter. Channel 0 therefore provides the low byte of the 16-bit number, and channel 1 provides the high byte. Channel 3 is not used in this circuit, and is simply ignored.

#### Monostable

The monostable is based on an

ICM 7555 device, IC4 which is the low power CMOS version of the ever popular 555 timer. In this case it is not the lower current consumption of the 7555 that makes it preferable to the standard 555, but its lower self-capacitance. This helps to give good accuracy when measuring very low value capacitors.

Resistors R2 to R6 are the five reference resistors, and SW1 is the range switch. The circuit must incorporate some means of trimming the output pulse duration of IC4 so that returned values can be made to agree with the test capacitor. Present resistors RV1 to RV5 provide this facility, and a separate preset for each range has been provided so that each range can be trimmed for optimum accuracy.

Normally the output pulse lasts until the charge on the timing

capacitor reaches two thirds of the supply voltage. The effect of the selected preset resistor is to modify this threshold voltage. By reducing this voltage, the output pulse duration for a given set of CR values is decreased — increasing the voltage has the opposite effect.

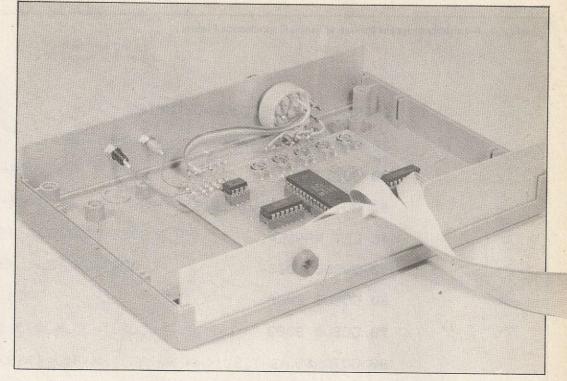

#### Construction

A plastic Verocase having metal front and rear panels and outside dimensions of 205 x 140 x40 mm is used as the housing for the prototype, but there should be no difficulty in using any case of about this size. In fact this case is somewhat larger than is really necessary, and a smaller case should be perfectly adequate to accomodate all the components.

Switch SW 1 is mounted on the

left hand section of the front panel leaving space for SK1 and SK2 on the right hand side of the panel. SW1 is a six way type with an adjustable end stop, and the latter is set for five way operation.

One or two millimetre sockets are probably the best choice for SK1 and SK2 since leadout wires will plug into these quite well. When using polarised capacitors the positive terminal must connect to SK1. It is advisable to use red and black sockets respectively for SK1 and SK2 to indicate the correct polarity for polarised components. Socket SK3 is a 4 mm type and it is mounted on the rear panel of the case.

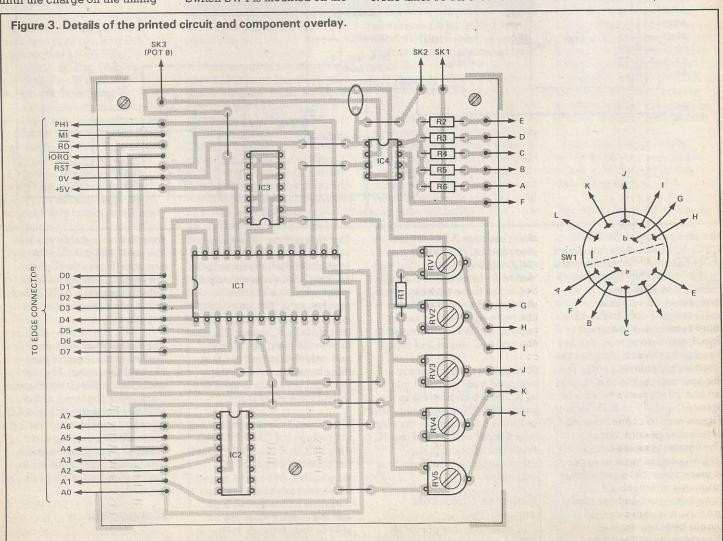

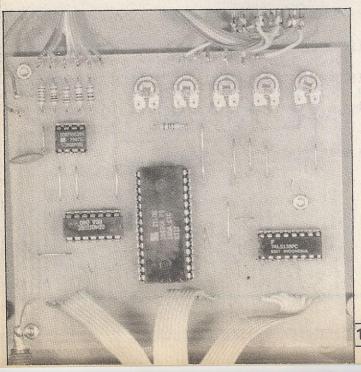

### Circuit Board

Details of the printed circuit board are provided in **Figure 3**. The timer IC4 is a CMOS

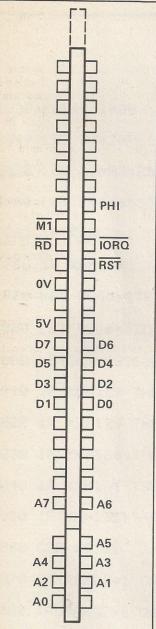

device, but its internal antistatic protection circuits render the normal CMOS handling precautions unnecessary. The situation is very different with ICI which is a MOS device, and is not one of the cheapest devices currently available. Use a 28 pin DIL IC socket for IC1, but do not fit it into place until construction of the unit is otherwise completed. Leave it in its protective packaging until this time, and then handle the device no more than is absolutely necessary. The board is connected to the expansion port of the computer via a 23 way ribbon cable about half a metre in length. This is terminate in either a 2 x 30 way 0.1 inch edge connector, or a Spectrum type 2 x 28 0.1 inch connector. The Spectrum connector does not reach all the parts that the 30 connector reaches, but it

Figure 4. Connection details for the edge connector.

connects to all the terminals that are needed on this application! Apart from being more readily available, a Spectrum edge connector has the further advantage of being fitted with a polarising key in the appropriate position, and it probably represents the best option.

Figure 4 gives connection details for the edge connector. The connections are grouped on the board in such a way as to make connecting the edge connector reasonably straightforward, but obviously great care to avoid errors should be taken when wiring the connector to the ribbon

cable.

Fit Veropins to the board at the points where connections to SW1 and the three sockets will be made. The completed board is mounted on the base panel of the case using M3 or 6BA fixings. It is advisable to include spacers about 6mm long to hold the connections on the underside of the board clear of the case, as otherwise the board might be distorted and damaged when it is bolted in place. The board is then wired to SW 1 and the sockets using ordinary hook-up wire. A slot must be filed in the rear panel of the case to provide a suitable exit hole for the 23 way ribbon cable. Socket SK3 is connected to the user port by way of an insulated lead about half a metre long and fitted with a 4mm plug at the end which connects to SK3, and either a

Figure 5. Connection details for the user port.

14 pin or 16 pin DIL plug at the end which connects to the computer's user port. The user port is the vacant 20 pin DIL socket on the computer's printed circuit board, and there is a gap at the rear of the machine to enable the lead to pass through to the outside

Figure 5 gives connection details for the user port. Although this port uses a 20 way DIL socket, a 14 or 16 pin plug has to be used as 20 pin plugs do not seem to be availble. Make sure that the plug is fitted into the socket at the right place. Note also that the user port outputs are three state types, and that the OTSTB terminal of the port must be tied to ground in order to take the outputs out of the high impedance state. A link wire must therefore be added to the plug, as shown in Figure 5.

#### Software

A suitable program for use with the unit is provided in **Listing 1**, and this is largely self explanatory in use.

The basic routine for taking a reading is to first set POT O high using an OUT 7, 1 instruction. Then OUT 18,5 is used to set channel 2 to IC1

into the mode where it first divides the clock by 16, and then by the number in the 8-bit counter. OUT 18,2 is then used to write a value of two to the counter, giving the required total division rate of 32. These instructions only need to be issued once at the beginning of the program.

Counter O is set to the right mode using an OUT 16,71 instruction, and then the 8-bit counter is set to "zero" using an OUT 16,255 instruction (255 rather than O since it is a down counter). This procedure is repeated for channel lusing OUT 17,71 and OUT 17,255 instructions. The monostable is then triggered by writing 0 and then 1 to the user port at address 7 to generate a negative pulse on POT O. The output pulse from IC4 can be no shorter than the length of the trigger pulse, and this pulse must therefore be quite short, (about one or two microseconds) in order to ensure that it does not result in the output pulse being stretched. This instruction should therefore be issued in assembly language as BASIC is too slow.

## Software Delay

Next a software delay is used to

## Listing 1. A suitable program for use with the Capacitance Meter.

10 REM MTX CAPACITANCE METER

20 REM JWP 15/6/84

30 OUT 7,1

40 OUT 18,5: OUT 18,2

45 LET RANGE=1

50 GOSUB 1000

60 GOSUB 2000

70 GOSUB 3000

80 GOTO 60

1000 CLS

1010 CSR 11,3: PRINT "CAPACITANCE METER"

1020 CSR 14.5: PRINT "Range "

1030 CSR 30,10: PRINT "F"

1040 CSR 7,20: PRINT "Change range with f1 - f5"

1050 RETURN

2000 OUT 16,71: OUT 16,255

2010 OUT 17,71: OUT 17,255

2020 CODE

811D LD A,0

811F OUT (7),A

8121 LD A,1

8123 OUT (7),A

8125 RET

Symbols:

```

2030 PAUSE 1000

2040 LET R1=IMP(16): LET R2=IMP(17)

2050 LET RS=R2*256+R1

2060 LET RDG=65535-R3

2063 IF RANGE=1 THEN LET RDG=RDG-27

2066 IF RANGE=2 THEN LET RDG=RDG-3

2070 LET RDGs=STRs(RDG)

2080 LET RDG==RIGHT=(RDG=,LEN (RDG=)-1)

<mark>3000 LET KN=ASC(IMKEY$): IF KNK128 OR KN>132 THEN GOTO 3060</mark>

3010 IF KM=128 THEN LET RANGE=1

3020 IF KN=129 THEN LET RANGE=2

3030 IF KH=130 THEN LET RANGE=3

3040 IF KN=131 THEN LET RANGE=4

3050 IF KM=132 THEN LET RANGE=5

3060 CSR 29,10

3070 IF RANGE=1 OR RANGE=2 THEM PRINT "n"

3080 IF RANGE=3 OR RANGE=4 OR RANGE=5 THEN PRINT """

|3090 IF LEN (RDG$)<5 THEN LET RDG$="0"+RDG$: GOTO 3090

3110 IF RANGE=1 OR RANGE=4 THEN LET DISP$=LEFT$(RDG$,2)+"."+RIGHT$(RDG$,3)

3120 IF RANGE=2 OR RANGE=5 THEN LET DISP$=LEFT$(RDG$,3)+"."+RIGHT$(RDG$,2)

3130 IF RANGE=3 THEN LET DISP$=LEFT$(RDG$,1)+","+RIGHT$(RDG$,4)

3140 CSR 20,10: PRINT DISP$

3150 CSR 20,5: PRINT RANGE

3160 RETURN

```

prevent the counters from being read until the count has been completed. Then the low byte is read using an INP (16) instruction, and the high byte is read using an INP(17) instruction. The high byte is multiplied by 256 and then added to the low byte to give the total number in the counters. Finally, this number is deducted from 65535 to effectivelty turn the down counter to an up counter, and the decimal point is then added at the appropriate position.

# Self Capacitance

On the lowest range the self capacitance of IC4, about 25p prevents reasonably accurate results from being obtained at low readings unless counter measures are taken. In a computer based design this is

quite easy, and it is merely necessary to deduct 25, or whatever, from the reading to effectively eliminate the self capacitance.

Range two suffers from the same problem, but to a much lesser degree. lines 2063 and 2066 make the necessary corrections to these two ranges, and the numbers used here can be altered to match the particular 7555 in you capacitance meter.

#### Calibration

Calibration of each range is very simple, and it is just a matter of connecting a capacitor to the unit, and then using trial and error to give the appropriate preset resistor a setting that gives the correct reading. Ideally the capacitor

should be a close tolerance type, and it should have a value which is something approaching the full scale value of the range being calibrated.

For example, on range one,0 to 65.535n a capacitor of about 33 to 56n in value would be suitable. On ranges four and five it is unlikely that close tolerance capacitors of suitably high value will be obtainable, and a lower level of accuracy will have to be tolerated on these ranges. Due to the high tolerance of large capacitors good accuracy on these ranges is not really necessary.

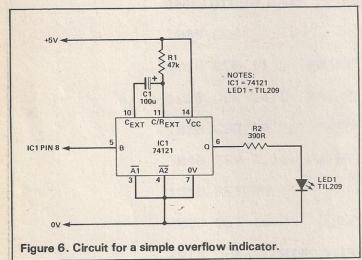

#### Overflow Indicator

The original capacitance meter design had an overflow indicator, and this was quite

easy to implement since an overflow of the counter resulted in a flag of the 6522/6526 chip being set. The overflow indicator could therefore be handled by a software routine monitoring this flag.

The Z80A CTC does not provide a direct equivalent of this, but if an overflow indicator is considered necessary it can be provided using a small amount of additional hardware. All that is needed is the 74121 monostable circuit of Figure 6.

If an overflow occurs a positive output pulse is produced at the channel 1 zero count output, (pin eight of IC 1). This pulse is used to trigger the 74121 which then flashes the LED indicator for about two to three seconds.

# **Parts List** RESISTORS All 1/4 watt 5% carbon R2......lk **POTENTIOMETERS** horiz preset CAPACITOR SEMICONDUCTORS counter/timer 1 of 8 decoder quad NAND gate IC4.....ICM7555 CMOS timer MISCELLANEOUS rotary switch red socket SK2.....lor 2mm black socket SK3.....4mm socket Case 205×140×40mm; printed circuit board; 2×30 ways or 2×28 way 0.1 inch edge connector (see text); DIL IC sockets; 1×16 pin; 1×14 pin; 1×8 pin; 1×28 pin; 14 or 16 pin DIL plug; 4mm plug; ribbon cable; Veropins; wire; solder etc.